mos -> Metal oricle Semiconductor

### MOS Denius

Mos clunces consist at 3 regions they are metal oricles and semiconcludor.

eg: mos capacitor, mos fet

# 1. Mos capacitor

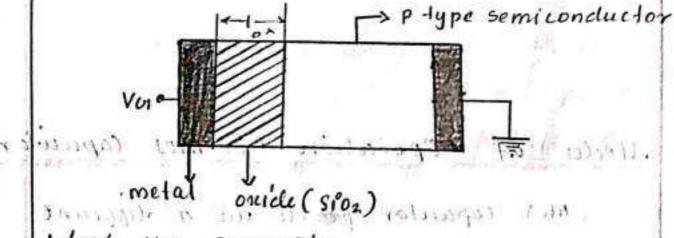

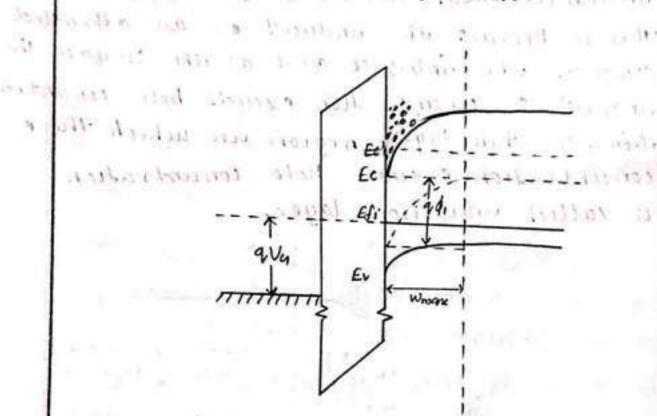

Is A 2 derminal metal orcicle semiconductor wis used as a mos eapacitor (also known as Mos diocle). The structure of a milal (A1) orcicle (8102) Semiconductor (p type si) capacitor is shown un fig below.

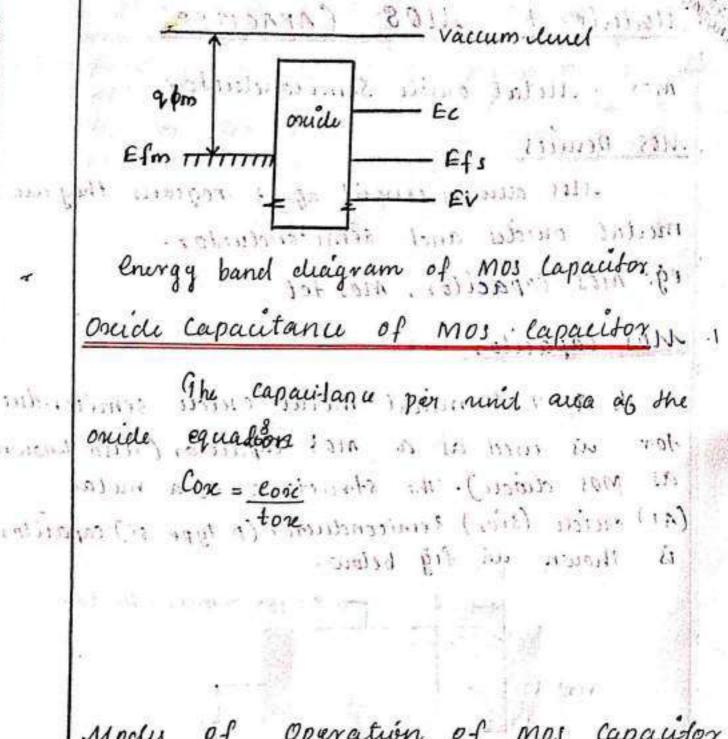

### Ideal Mos Capacitor

A Mos capacitor is considered to be ideal if (1) the work function by the metal and semiconductor are equal A) oxide is a perfect unsulador with no trapped charges, no dejects and no unterface states.

all sand

## Modes of Operation of mos capacidor

mos capacitor operate un 4 debbeeint teleat that earner modes.

I Accumulation mode (ver 40) metal loxide 1 ptype mursion mode (varo) instruct train 4] 8-trong mursion mode C.

-12 117

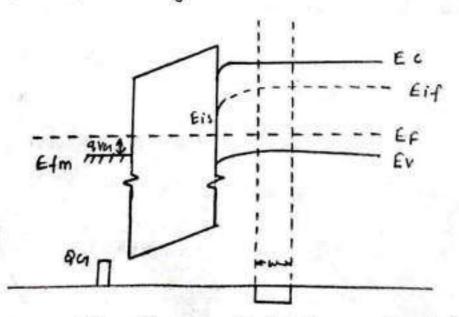

when a small the gate vollage is applied, charges are untroduced in the p-type, semiconductor. There -ve charge s recombined with horles up the semiconductor which borms depetition requor near the unterpace

The bending at energy bands undicating decrease at horse concentration near the untertace win the objection region. Effective capacitance is the series combination at oricle capacitance and depletion layer capacitance (CP)

ui,  $C_{total} = \frac{Cone \times C_D}{Cox + C_P}$

where Ctot → Total capacitance lunit area

cox → Oxicle capacitance lunit area

co → Depletion layer capacitance lunit area

Energy band diagram and charge dimity dustribution is guin below

W= width of the depletion region (layer) =

layer is guin by.

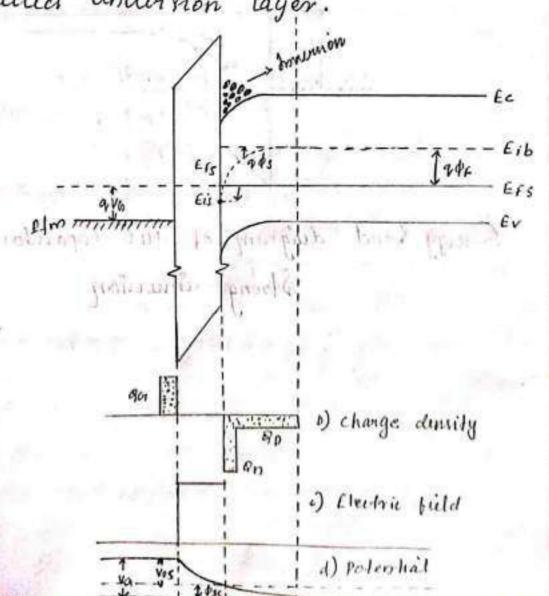

# of Inversion Requien

If Voi is unwasted pourther the beams duel on the so side mones up pourther. The bands bend down pivilher so that the fermilial at the swyaw die above the witrings duel wit, the swiface gets unwilled this is because the unduced e's au attracted dowards the interface and at the swiface the unduced e' conuntration excueds hole conuntration. The thin layer region un which the e-conuntration excueds hole conuntration is called unwersion layer.

energy lund at the swiface get below barmi dund by an amount equal to that it is about the beami dund at the buck. I the e-tonuntration at the swiface become equal to the total hole concentration un the semiconcludor.

Energy band diagram of mos Capacitos uneler Strong unwision

Manual I Thorashold Vollage At is the voiltage viequied do un troclute strong ununion un the sec uncler this the condition a conducting layer is unduced below the gate region.

At the onset of inversion.

$$\frac{V_{ih} = \frac{-Q_{Dm}}{cox} + 2\phi s}{cox}$$

$$w_{m} = \int \frac{2E R dF}{aNa}$$

$$\Phi \ \text{Gom} = - q N_A \int \frac{4 \varepsilon \, \Phi F}{q \, N_A}$$

The sent Victorial Car and pro-

the state of the second of the

the owner was a first open with the same of the territory of the same of the s

Maries and the state of the sta

Effects of Real surgace

when mos dernies are made rung differents material departures from the idual mos capacilor il can s-trongly. affect by the bollowing I threshold vollage (V4) (Reb. thrushold vollage) & I work Function dyfeunce 3] Interface charge

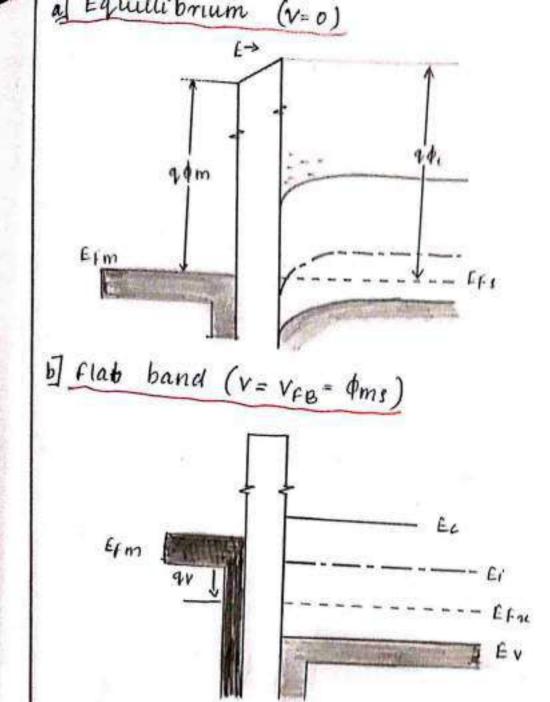

work function Difference

In wal mos system the work function at metal and se may be dybicunt. Let Oms be the difference un morkfunction of metal and sc het oms = om - osc TALLET

If we try to construct an equilli bruin diagram with Ims negative me fund that un aligning Ex un must unclude a dill un the oxide conduction band. Thust the metal is the charged and the semiconductor swegare is negatively charged at equillibrium to accomodate the work function difference: As a result, the band bends bend down near the semi conductor sweak. In fact, if oms is sufficiently negative, an unversion region can exist with no external voctage applied. To obtain the blat band condition pictured we must applied a -ne votlage

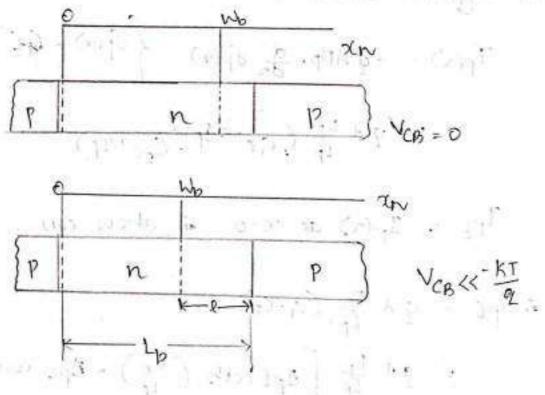

# Base Width Modulation or Early Effect

The effective base width NB & Essentially independent of the bias weltage applied to the collecter and emitter junctions. The is not always valid.

13 bear region is slightly diped; the depletion rigios at severe busised collector for can extend significantly into the integre loave region its collector wortage introduction of the base layer takes up more of metallugical concepts of the base Lp, and effective bear width made to decreased. This effect as manipusly called base massocions, base windth modulation to carry effect.

Nb = 46-1 Id JVB

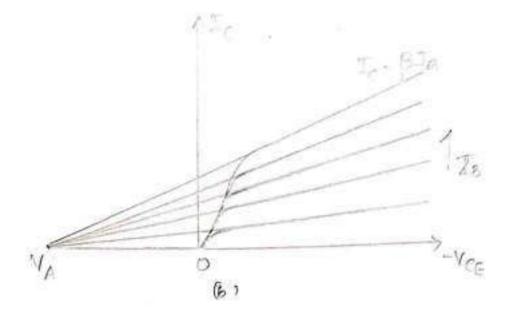

Effects of base narrowing on characteristics of a pt-n-pt

- 6) Decrease in the effective bour width as the severe bios on collector giv wireard.

- (b) common entitles characteristics showing the increase so  $\Gamma_t$  with increased collector moltage.

- (c) The black line of (b) inducate the extrapolarisation of courses to the early nothings VA.

#### MOSFET SCALING

One approach to size reduction is a scaling of the MOSFET that requires all device dimensions to reduce proportionally. The main device dimensions are the channel length, channel width, and oxide thickness Lateral dimensions such as channel length and width are reduced by a factor of k, so should the vertical dimensions such as source/drain junction depths and gate insulator thickness

Scaling of depleton width is achieved indirectly by scaling up doping conentrations. If we simply reduce the dimensions of the device and kept the power supply voltages same, the internal electric field in the device would increase.

#### Scaling improves

- 1.Packing density

- 2.Speed

- 3.Power dissipation

Two types of scaling are common:

- (i) constant field scaling

- (ii) constant voltage scaling.

#### Full scaling (constant-field scaling) -

- All dimensions are scaled by k and the supply voltage and other voltages are so scaled

- Magnitude of internal electic field is kept constant

- Only lateral dimensions are changed

- Threshold voltage is also affected

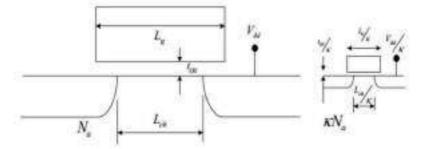

Figure 2: 5 thustration of MOSFET minimum risation. The sketch on the right hand is the scaled device according to the constant field rule. (Reference [2,15])

Constant field scaling yields the largest reduction in the power-delay product of a single transistor. However, it requires a reduction in the power supply voltage as one decreases the minimum feature size.

For ideal scaling, power supply voltages should be reduced to keep the internal electric field reasonably constant from one technology generation to the next. But power supply voltages are not scaled hand in hand with the device dimensions, partly because of other system related constraints.

The longitudinal electric field in the pinch off region and the transverse electric field across the gate oxide increase with MOSFET scaling which causes hot electron effects and short channel effects.

Table 6-1 Scaling rules for MOSFETs according to a constant factor K. The horizontal and vertical dimensions are scaled by the same factor. The voltages are also scaled to keep the internal electric fields more or less constant, and the hot carrier effects manageable.

| Scaling factor              |                  |  |  |  |  |

|-----------------------------|------------------|--|--|--|--|

| Surface dimensions (L,Z)    | 1/K              |  |  |  |  |

| Vertical dimensions (d,x)   | 1/K              |  |  |  |  |

| Impurity Concentrations     | K                |  |  |  |  |

| Current, Voltages           | 1/K              |  |  |  |  |

| Current Density             | K                |  |  |  |  |

| Capacitance (per unit area) | K                |  |  |  |  |

| Transconductance            | 1                |  |  |  |  |

| Circuit Delay Time          | 1/K              |  |  |  |  |

| Power Dissipation           | 1/K <sup>2</sup> |  |  |  |  |

| Power Density               | 1                |  |  |  |  |

| Power-Delay Product         | 1/K <sup>3</sup> |  |  |  |  |

Constant voltage scaling does not have this problem and is therefore the preferred scaling method since it provides voltage compatibility with older circuit technologies.

The disadvantage of constant voltage scaling is that the electric field increases as the minimum feature length is reduced.

Constant-voltage scaling The voltages are not scaled and, in some cases, dimensions associated with voltage are not scaled.

#### Constant voltage scaling

| Parameter                                    | Scaled parameter |

|----------------------------------------------|------------------|

| Channel length (L)                           | 1/α              |

| Junction depth (x <sub>j</sub> )             | 1/α              |

| Substrate doping (N <sub>A</sub> )           | a                |

| Depletion layer thickness (d)                | 1/α              |

| Transconductance (g <sub>m</sub> )           | α                |

| Static power dissipation (P <sub>sat</sub> ) | α                |

| Dynamic power dissipation (Pon)              | α                |

| Current (I)                                  | α                |

| Gate delay (τ <sub>p</sub> )                 | 1/a²             |

| Load capacitance (C <sub>1</sub> )           | 1/α              |

| Channel width (W)                            | 1/α              |

| Supply voltage (V)                           | 1                |

| Gate oxide thickness (t <sub>ox</sub> )      | 1/α              |

| Current density (J)                          | α³               |

#### Comparison

| Quantity             | Sensitivity    | Constant Field | Constant<br>Voltage |

|----------------------|----------------|----------------|---------------------|

|                      | Scaling Parame | eters          |                     |

| Length               | L              | 1/S            | 1/S                 |

| Width                | W              | I/S            | I/S                 |

| Gate Oxide Thickness | tox            | 1/S            | 1/S                 |

| Supply Voltage       | Vali           | I/S            | 1                   |

|                      |                |                |                     |

| Threshold Voltage               | V <sub>T0</sub>                 | 1/S              | 1                |

|---------------------------------|---------------------------------|------------------|------------------|

| Doping Density                  | N <sub>A</sub> , N <sub>D</sub> | S                | $S^2$            |

| De                              | vice Characterist               | ics              |                  |

| Area (A)                        | WL                              | I/S <sup>2</sup> | 1/S <sup>2</sup> |

| D-S Current (Ios)               | $\beta(V_{dd} - v_T)^2$         | 1/S              | S                |

| Gate Capacitance (Cg)           | WL/tax                          | I/S              | I/S              |

| Power Dissipation (P)           | I <sub>DS</sub> V <sub>dd</sub> | I/S <sup>2</sup> | S                |

| Power Dissipation Density (P/A) | P/A                             | I                | S                |

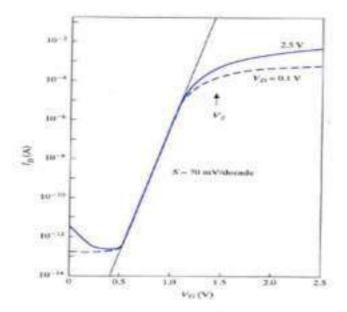

#### Subthreshold conduction / Subthreshold Characteristics

For the conduction to happen in the MOSFET; we need the V<sub>G</sub> to be greater than the threshold voltage V<sub>T</sub>. But, this threshold voltage is calculated at the point where the region below the oxides has entered into strong inversion.

From experimental results, one can observe that there is still some non-zero current flowing from drain to source even when we are operating at a region with  $V_G < V_T$  (sub-threshold region). This happens because, for the subthreshold region, the substrate near oxide-interface is in "Weak-Inversion". At this point, if we apply a positive  $V_{DS}$ , there will be a small current  $I_D$  flowing. This effect is plotted in the transfer characteristics in figure below. We have,

$$I_D = \frac{W}{L} \cdot \mu_n C_{OX} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

In this equation, current abruptly goes to zero as soon as V<sub>G</sub> is reduced to V<sub>T</sub>. In reality there is still some drain conduction below threshold, and is known as subthreshold conduction. This current is due to weak inversion in the channel between flat band and threshold which leads to a diffusion current from source to drain.

Subthreshold Swing,

$$S = \log \frac{d(V_G)}{d(\log I_D)}$$

- Generally, in order to improve the performance and reduce the cost of production, one

would prefer to scale down the size of the transistors.

- This scaling down also eliminates many stray capacitances that are present in the overall device. Ultimately increasing the speed of operation.

- But when the channel length is scaled down to the order of the depletion layer, a certain number of non-ideal effects come into play. These are called second-order effects

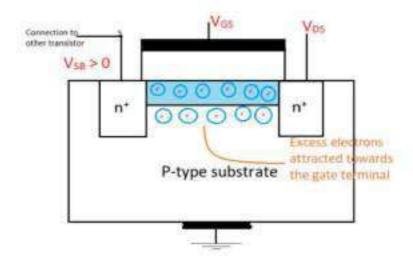

#### Substrate Bias Effect

For the ideal IV characteristics, the biasing scheme we used had the source and the body both connected to ground.

But in practical design applications, Source is connected to substrate(body) so that there is a voltage Vsa

In such scenarios, the difference in potential between the body and the source terminal causes a change in the threshold voltage of the MOSFET. This effect of change in threshold voltage is called the "Body Effect" or the "Back Gate Effect".

When V<sub>SB</sub> is positive, there is reveres bias between source and bulk. This causes depletion layer to widen.

The electrons in the bulk are repelled by the body terminal and are now attracted by the gate toward the oxide layer.

The threshold voltage of the MOS is also proportional to the density of electrons in the depletion layer.

Hence as we accumulate more and more electrons in the depletion layer below the oxide interface, there will be an increase in the value of threshold voltage.

As depletion region is widened, larger charge density is occupied. Therefore, the threshold required to achieve inversion increases.

$$V_{TN} = V_{T0} + \gamma \left( \sqrt{2|\phi_F|} + V_{SB} - \sqrt{2|\phi_F|} \right)$$

$V_{T0} = \text{zero-substrate-bias } V_T$

$\gamma = \text{body effect parameter}$

$|\phi_F| = \text{surface potential parameter}$

#### Short Channel Effects

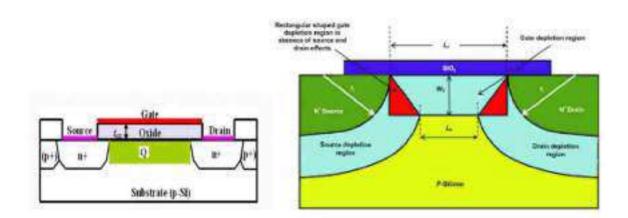

Short-channel effects occur in MOSFETs in which the channel length is comparable to the depletion layer widths of the source and drain junctions.

A MOSFET device is considered to be short channel device when the channel length is the same order of magnitude as the depletion-layer widths (x<sub>dD</sub>, x<sub>dS</sub>) of the source and drain junction. (That is, the effective channel length L<sub>eff</sub> is approximately equal to the source and drain junction depth x). As the channel length L is reduced to increase both the operation speed and the number of components per chip, the so-called short-channel effects arise.

The short-channel effects are attributed to two physical phenomena:

- 1. The limitation imposed on electron drift characteristics in the channel

- 2. The modification of the threshold voltage due to the shortening channel length.

This occurs due to the charge sharing between source/drain and gate. A triangle region forms at both ends

Hence the rectangular area under the gate becomes Trapizoid

Different short-channel effects include

- 1. Channel Length Modulation

- 2. Drain-induced barrier lowering and "Punch through"

- 3. Velocity saturation

- 4. Threshold voltage variations

- 5. Hot carrier effects

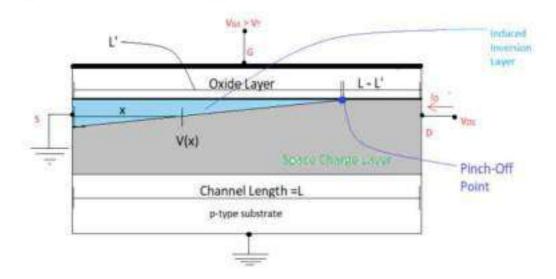

#### Channel Length Modulation(CLM)

As we keep on increasing V<sub>DS</sub>, the region for which the inversion charge is zero keeps on increasing for a constant value of V<sub>GS</sub> maintained. Thus channel length keeps on decreasing. This phenomenon is called Channel Length Modulation.

This is a similar to "Base Width Modulation" Thus we get a V<sub>DS</sub> term in the expression for I<sub>D</sub> even when we are operating in the saturation region.

Generally, the fabrication of the MOSFET devices is done in a way such that the change in length given by ΔL=L-L' is low with a change in V<sub>DS</sub>.

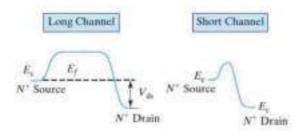

#### Drain Induced Barrier Lowering (DIBL)

When the depletion regions surrounding the drain extends to the source, so that the two-depletion layer merge (i.e., when  $x_{dS} + x_{dD} = L$ ), punch through occurs.

Punch through can be minimized with thinner oxides, larger substrate doping, shallower junctions, and obviously with longer channels.

The current flow in the channel depends on creating and sustaining an inversion layer on the surface.

If the gate bias voltage is not sufficient to invert the surface (V<sub>GS</sub> <V<sub>T</sub>), the carriers (electrons) in the channel face a potential barrier that blocks the flow. Increasing the gate voltage reduces this potential barrier and, eventually, allows the flow of carriers under the influence of the channel electric field.

In small-geometry MOSFETs, the potential barrier is controlled by both the gate-to-source voltage V<sub>GS</sub> and the drain-to-source voltage V<sub>DS</sub>.

If the drain voltage is increased, the potential barrier in the channel decreases, leading to draininduced barrier lowering (DIBL).

The reduction of the potential barrier eventually allows electron flow between the source and the drain, even if the gate-to-source voltage is lower than the threshold voltage.

The channel current that flows under this condition (VGS < VT) is called the sub-threshold current

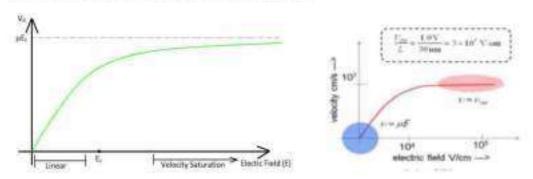

#### Velocity Saturation

The velocity of charge carriers, such as electrons or holes, is proportional to the electric field that drives them, but that is only valid for small fields.

As the field gets stronger, their velocity tends to saturate. That means that above a critical electric field, they tend to stabilize their speed and eventually cannot move faster.

Velocity saturation is specially seen in short-channel MOSFET transistors, because they have higher electric fields

The drift velocity of the electrons in the inversion layer to be proportional to the lateral electric field applied. The proportionality constant was given by  $\mu_n$ .

The key point to understand the effect of velocity saturation is that the linearity of the drift velocity only holds true for low values of the applied electric field. The actual variation of drift velocity with respect to the applied electric field is shown in figure 6.

The exact formula for the drift velocity can be given as:

$$v_d = \frac{\mu E}{1 + E/E_c}$$

The term  $E_r$  is called the critical electric field. Here the electric field E is equal to  $\frac{V_{BS}}{L}$ , i.e. the lateral voltage applied across the channel divided by the effective channel length. We can see that for large channel devices, the drift velocity formula simplifies to  $v_d = \mu E$ . Hence this is also a short channel effect because the lateral electric field is higher in case of short channel devices for similar range of drain-to-source voltage applied.

Figure 6: Variation of drift velocity of electron w.r.t. applied electric field

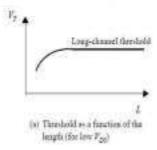

#### Threshold Variations

The threshold voltage is only a function of the manufacturing technology and the applied body bias V<sub>SB</sub>.

The threshold can therefore be considered as a constant over all NMOS (PMOS) transistors in a design. As the device dimensions are reduced, this model becomes inaccurate, and the threshold potential becomes a function of L, W, and V<sub>DS</sub>.

Two-dimensional second-order effects that were ignorable for long-channel devices suddenly become significant.

In the traditional derivation of the V<sub>TO</sub>, for instance, it is assumed that the channel depletion region is solely due to the applied gate voltage and that all depletion charge beneath the gate originates from the MOS field effects.

This ignores the depletion regions of the source and reverse-biased drain junction, which become relatively more important with shrinking channel lengths.

Since a part of the region below the gate is already depleted (by the source and drain fields), a smaller threshold voltage suffices to cause strong inversion.

In other words, V<sub>10</sub> decreases with L for short-channel devices (Figure 3.35a).

Figure 3.35 Threshold variations

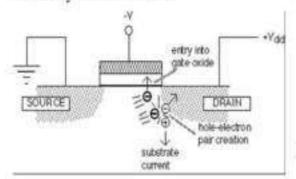

#### **Hot-Carrier Effects**

Another problem, related to high electric fields, is caused by so-called hot electrons. This high energy electrons can enter the oxide, where they can be trapped, giving rise to oxide charging that can accumulate with time and degrade the device performance by increasing V<sub>T</sub> and affect adversely the gate's control on the drain current.

Besides varying over a design, threshold voltages in short-channel devices also have the tendency to drift over time. This is the result of the hot-carrier effect Over the last decades, device dimensions have been scaled down continuously, while the power supply and the operating voltages were kept constant. The resulting increase in the electrical field strength causes an increasing velocity of the electrons, which can leave the silicon and tunnel into the gate oxide upon reaching a high-enough energy level.

Electrons trapped in the oxide change the threshold voltage, typically increasing the thresholds of NMOS devices, while decreasing the V<sub>T</sub> of PMOS transistors.

For an electron to become hot, an electrical field of at least 10<sup>4</sup> V/cm is necessary. This condition is easily met in devices with channel lengths around or below 1 mm.

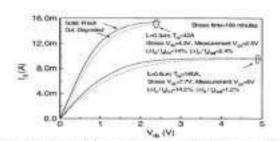

The hot-electron phenomenon can lead to a long-term reliability problem, where a circuit might degrade or fail after being in use for a while. This is illustrated in Figure 3.36, which shows the degradation in the I-V characteristics of an NMOS transistor after it has been subjected to extensive operation.

MOSFET technologies, therefore use specially-engineered drain and source regions to ensure that the peaks in the electrical fields are bounded, hence preventing carriers to reach the critical values necessary to become hot.

Figure 3.36. However, efforts some the J.P elementerative of an PARIS interiors to degrale from attractor range (finite [Michiga](478)).

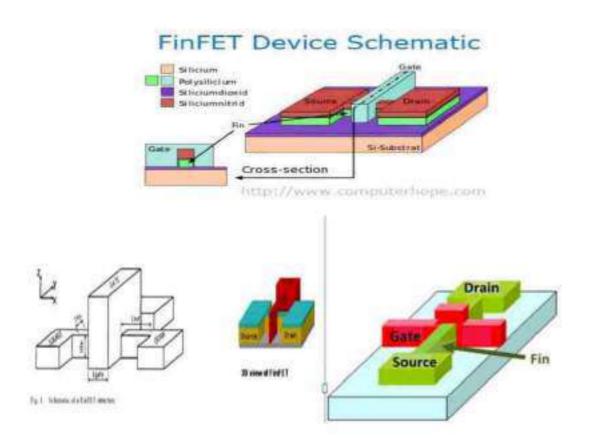

#### FinFET

- FinFET, also known as Fin Field Effect Transistor, is a type of non-planar or "3D" transistor used in the design of modern processors

- FinFETs are new generation transistors which utilize tri-gate structure. In contrast to planar transistors where the Gate electrode was (usually) above the channel, the Gate electrode "wraps" the channel

- The distinguishing characteristic of the FinFET is that the conducting channel is wrapped by a thin silicon "fin", which forms the body of the device.

- The conducting channel is greatly controlled by the gate.

- The thickness of the fin (measured in the direction from source to drain) determines the

effective channel length of the device.

- These effects make it harder for the voltage on a gate electrode to deplete the channel

underneath and stop the flow of carriers through the channel in other words, to turn the

transistor Off. By raising the channel above the surface of the wafer instead of creating the

channel just below the surface, it is possible to wrap the gate around up to three of its sides,

providing much greater electrostatic control over the carriers within it.

#### Advantages

Reduced short-channel effects (SCEs) and leakage current.

To overcome the worst types of short-channel effect encountered by deep submicron transistors, such as drain-induced barrer lowering (DIBL).

This technique provides increased operating speed by low-threshold MOSFET and reduced leakage by high-threshold voltage.

- The very first finFETs were manufactured on top of insulating layer.

- The fact that the current can't flow "underneath" the gate when the transistor is in OFF state reduces the leakage current.

- Alternative techniques for stopping leakage current from flowing in the bulk were introduced later, which allowed for manufacturing of Bulk finFETs.

- This technique utilizes very high doping gradients along the height of the fin in order to prevent the current from flowing in the bulk.

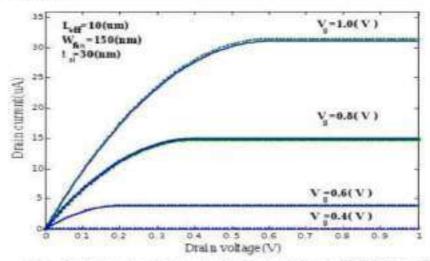

#### Output Characteristics

#### **Drain Characteristics**

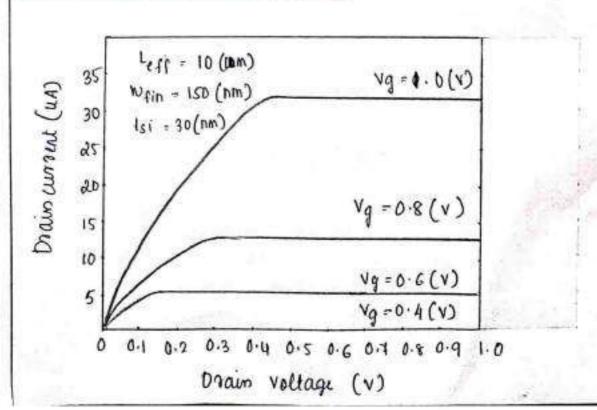

Fig. 2: show the output characteristics of FinFET of Lch=10μm, Wfin=150nm, tsi= 30nm for various gate voltage. Symbols are for experimental data and solid line for simulation result of this work.

#### Transfer Characteristics

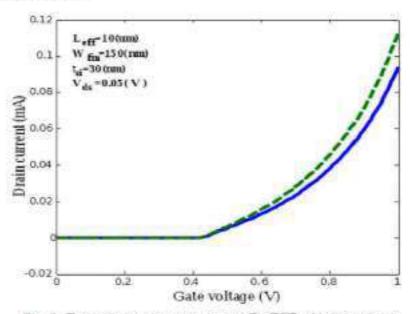

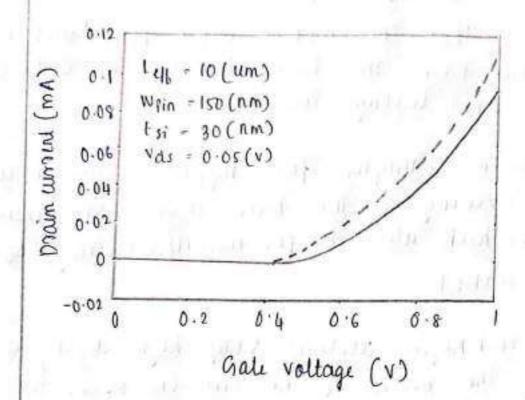

Fig.3: Transfer characteristics of FinFET of Lch=10μm, Wfin=150nm and tsi= 30nm Desh line for the experimental data and solid line for simulation result of this work.

## FINFET

- \* Fin PET, also known as Pin Pield Effect Mansister, is a type of non-planar on "30" transister used in the design of modern processors.

- \* Pinfers are new generation transistons which utilize tri-gate structure. In constrast to planar transistons where the crate electrode was above the channel, the Gate electrode "wraps" the channel.

- \* The distinguishing characteristics of the FinEET is that the conducting channel is wrapped by a thin Silicon "fin", which forms the body of the device:

- \* The conducting channel is greatly controlled by the gate.

- \* The thickness of the fin determines the effective channel length of the device.

- \* Thise effects make it harder for the voltage on a gate electrode to deplete the channel under realth and stop the flow of carriers through the channel in other words, to true the transistor Off. By raising the channel above the surface of the water instead of oreating the channel just below the

Surface, it is possible to wrap the gate around up to there of its sides, providing much greater electrostatic control over the carriers within it.

# Advantages

Reduced short-channel effects (SCES) and leakerge

To overcome the worst types of short-channel effect encountered by deep submicron transistors, such as drain-induced barrier lowering (DIBL).

This technique provides increased operating speed by low - threshold MOSFET and reduced beadges leakage by high - thushold voltage.

contained as digital landaut

and the a manufacture with our properties and

to be there in the amount of which record made a

- Latt Long as of daight of the same days

The state of the s

the state of the state of the state of

with the same I would the the same of appropria

the top of the set of the set of the

- top of insullating layer.

- \* The fact that the current can't flow "underneath" the gate when the transister is in OFF state reduces the leakage current

- \* Alternative techniques for stopping leakage unsent from flowing in the bulk were introduced later, which allowed for manufacturing of BULK finfers

- \* This technique utilizes very high doping gradien along the height of the fin in order to prevent the current from flowing in the bulk

# Output characteristics

Drain characteristics

## Manger characteristics

the set of the set of

GOT ST

TROM D

- AF ADMILE HALL

- Land Land Contract of

alirah 11-

41.12 - 11.7

of the state of

d lare