Design and Development of Embedded Product – Firmware Design and Development – Design Approaches, Firmware Development Languages.

# FIRMWARE DESIGN AND DEVELOPMENT Introduction

- Embedded firmware is responsible for controlling various peripherals of the embedded hardware and generating responses in accordance with the functional requirements mentioned in the requirements for the particular product

- Firmware is considered as the master brain of the embedded systems

- Imparting intelligence to an embedded system is a one time process and it can happens at any stage of the design

- Once the intelligence is imparted to the embedded product, by embedding the firmware in the hardware, the product start functioning properly and will continue serving the assigned task till hardware breakdown occurs or a corruption in embedded firmware occurs

- Designing an embedded firmware requires understanding of embedded product hardware like, various component interfacing, memory map details I/O port details, configuration and register details of various hardware chips used and some programming language.

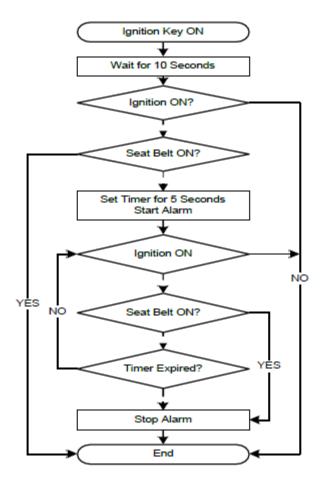

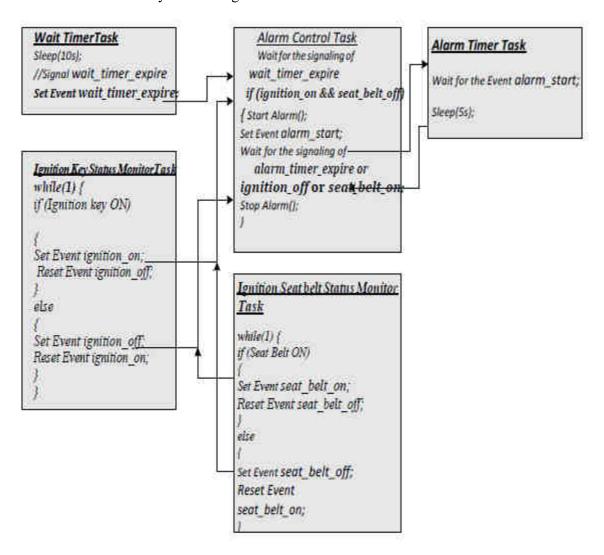

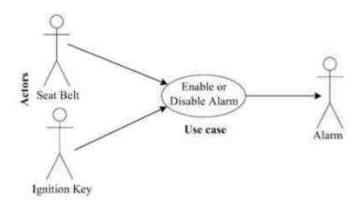

- Embedded firmware development process start with conversion of firmware requirements into a program model using modeling tools like UML or flow chart based representation

- UML diagram gives diagrammatic representation of the decision items to be taken and the task to be performed

- Once the program modeling is created, next step is the implementation of the task and actions by capturing the model using a language which is understandable by the target processor

- Following gives an overview of the various steps involved in the embedded firmware design and development

## EMBEDDED FIRMWARE DESIGN APPROACHES

- •Firmware design approaches depends on the

- -Complexity of the function to be performed

- -Speed of operation required ..

- -Etc

- •Two basic approaches for firmware design

- 1. Conventional Procedure based Firmware Design/Super Loop Design

- 2. Embedded Operating System Based Design

## 1. SUPER LOOP BASED APPROACH

- ➤ This approach is applied for the applications that are not time critical and the response time is not so important

- ➤ Similar to the conventional procedural programming where the code is executed task by task

- Task listed at the top of the program code is executed first and task below the first task are executed after completing the first task

- > It is True procedural one ```

- In multiple task based systems, each task executed in serial

- Firmware execution flow of this will be as following

- 1. Configure the common parameter and perform initialization for various hardware components, memory, registers etc.

- 2. Start the first task and execute it

- 3.Execute the second task

- 4.Execute the next task

- 5.....

- 6....

- 7.Execute the last defined task

- 8.Jump back to the first task and follow the same flow

- From the firmware execution sequence, it is obvious that the order in which the task to be executed are fixed and they are hard coded in the code itself

- ➤ Operations are infinite loop based approach In terms of C program code as:

```

Void main() {

configuration();

initializations();

while(1) {

task1();

task2();

```

. . . . .

## taskn();} }

- Almost all task in embedded applications are non-ending and are repeated infinitely throughout the operation

- ➤ By analyzing C code we can see that the task 1 to n are performed one after another and when the last task is executed, the firmware execution is again redirected to task 1 and it is repeated forever in the loop. This repetition is achieved by using an infinite loop(while(1)) Therefore Super loop based Approach

- ➤ Since the task are running inside an infinite loop, the only way to come out of the loop is either

- -Hardware reset

or

## -Interrupt assertion

- A Hardware reset brings the program execution back to the main loop

- ➤ Whereas the interrupt suspend the task execution temporarily and perform the corresponding interrupt routine and on completion of the interrupt routine it restart the task execution from the point where it got interrupted

- ➤ Super Loop based design does not require an OS, since there is no need for scheduling which task is to be executed and assigning priority to each task.

- ➤ In a super Loop based design, the priorities are fixed and the order in which the task to be executed are also fixed

- ➤ Hence the code for performing these task will be residing in the code memory without an operating system image

- This type of design is deployed in low-costembedded products where the response time is not time critical

- > Some embedded products demand this type of approach if some tasks itself are sequential

- For example, reading/writing data to and from a card using a card reader requires a sequence of operations like checking the presence of the card, authenticating the operation, reading/writing etc..It should strictly follows a specified sequence and the combination of these series of tasks constitutes a single task namely read write

- ➤ There is no use in putting the sub tasks into independent task and running them parallel

- ➤ Example of "Super Loop Based Design" is

-Electronic video game toy containing keypad and display unit

- ➤ The program running inside the product must be designed in such a way that it reads the key to detect whether user has given any input and if any key press is detected the graphic display is updated. The keyboard scanning and display updating happens at a reasonable high rate

- > Even if the application misses the key press, itwon't create any critical issue Rather it will treated as a bug in the firmware

## **Drawback of Super Loop based Design**

- ➤ Major drawback of this approach is that any failure in any part of a single task will affect the total system

- If the program hang up at any point while executing a task, it will remain there forever and ultimately the product will stop functioning

## -Some remedial measures are there

- •Use of Hardware and software Watch Dog Timers (WDTs) helps in coming out from the loop when an unexpected failure occurs or when the processor hang up

- -May cause additional hardware cost and firmware overhead

- ➤ Another major drawback is lack of real timeliness

- If the number of tasks to be executed within an application increases, the time at which each task is repeated also increases. This brings the probability of missing out some events

- For example in a system with keypad, there will be task for monitoring the keypad connected I/O lines and this need not be the task running while you press the keys

- That is key pressing event may not be in sync with the keypad press monitoring task within the firmware

- To identify the key press, you may have to press the key for a sufficiently long time till the keypad status monitoring task is executed internally.

- Lead to lack of real timeliness

# 2. Embedded Operating System Based Approach

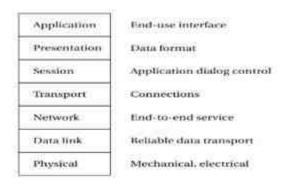

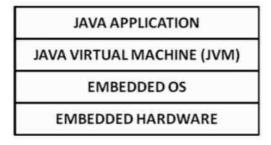

➤ Contains OS, which can be either a General purpose Operating System (GPOS) or real Time Operating System (RTOS)

# General purpose Operating System (GPOS) based design

- ➤ GPOS based design is very similar to the conventional PC based Application development where the device contain an operating system and you will be creating and running user applications on top of it

- Examples of Microsoft Windows XP OS are PDAs, Handheld devices/ Portable Devices and point of Sale terminals

- ➤ Use of GPOS in embedded product merges the demarcation of Embedded systems and General Purpose systems in terms of OS

- For developing applications on the top of the OS, OS supported APIs are used

- > OS based applications also requires 'Driver Software' for OS based applications also requires 'Driver Software' for different hardware present on the board to communicate with them

## RTOS based design

- ➤ RTOS based design approach is employed in embedded product demanding Real Time Responses

- > RTOS respond in a timely and predictable manner to events

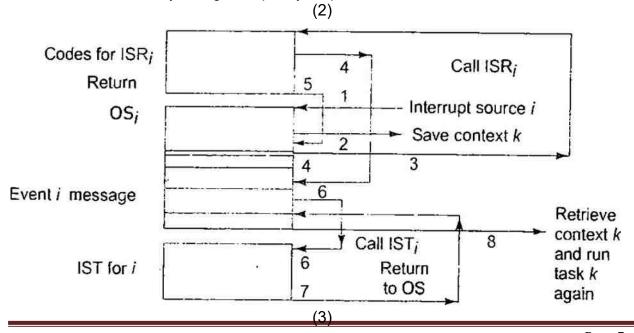

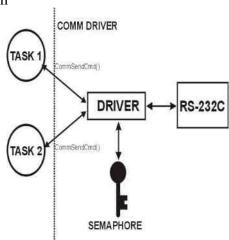

- > RTOS contain a real time Kernel responsible for performing pre- emptive multi tasking scheduler for scheduling the task, multiple thread etc.

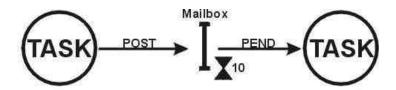

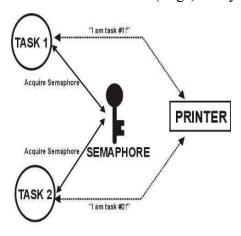

- > RTOS allows a flexible scheduling of system resources like the CPU and Memory and offer some way to communicate between tasks

- -Examples of RTOS are

- •Windows CE, pSOS, VxWorks, ThreadX, Micro C/OS II,Embedded Linux, Symbian etc...

## EMBEDDED FIRMWARE DEVELOPMENT LANGUAGES

For embedded firmware development you can use either

- -Target processor/controller specific language (Assembly language) or

- -Target processor/ controller independent language (High level languages) or

- -Combination of Assembly and high level language

## ASSEMBLY LANGUAGE BASED DEVELOPMENT

- Assembly language is human readable notation of machine language whereas machine language is a processor understandable language. Processor deal only with binaries

- Machine language is a binary representation and it consist of 1s and 0s.Machine language is made readable by using specific symbols called 'mnemonics'. Hence machine language can be considered as an interface between processor and programmer

- Assembly language and machine languages are processor dependant and assembly program written for one processor family will not work with others

- Assembly language programming is the task of writing processor specific machine code in mnemonics form, converting the mnemonics into actual processor instructions (machine language) and associated data using an assembler

- Assembly language program was the most common type of programming adopted in the beginning of software revolution

- ➤ Some OS dependant task requires low level languages

- ➤ In particular assembly language is used in writing low level interaction between the OS and the hardware, for instance in device drivers

- > The general format of an assembly language instruction is

## Opcode Operand

- -Opcode tells what to do

- -Operand gives the information to do the task

The operand may be single operand, dual operand or more

example-

MOV A, #30

- –Move the decimal value 30 to the accumulator register of 8051

- -Here MOV A is the opcode and 30 is Operand

- -Same instruction in machine language like this

## 01110100 00011110

- -Here the first 8 bit represent opcode MOV A and next 8 bit represent the operand 30

- The mnemonic INC A is an example for the instruction holding operand implicitly in the Opcode

The machine language representation is 00000100

- -This instruction increment the 8051 Accumulator register content by 1

- ➤ LJMP 16 BIT ADDRESS is an example of dual operand instruction

- The machine language for the same is

10 addr\_bit15 to addr\_bit8 addr\_bit7 to addr\_bit0

- The first binary data is the representation of LJMP machine code

- The first operand that immediately follow the opcode represent the bit 8 to 15 of the 16 bit address to which the jump is requited and the second

- operand represent the bit 0 to 7 of the address to which the jump targeted

- ➤ Assembly language instructions are written in one per line

- A machine code program thus consisting of a sequence of assembly language instructions, where each statement contains a mnemonic(opcode+operand)

- Each line of assembly language program split into four field as given below

## LABEL OPCODE OPERAND COMMENTS

- ➤ Label is an optional field. A label is an identifier to remembering where data or code is located

- ➤ LABEL is commonly used for representing

- -A memory location, address of a program, sub-routine, code portion etc...

- -The max length of the label differ between assemblers. Labels are always suffixed by a colon and begin with a valid character. Labels can contain numbers from 0 to 9 and special character

- -Labels are used for representing subroutine names and jump locations in Assembly language programming

DELAY: MOV R0, #255 ;load Register R0 with 255

DJNZ R1, DELAY ;Decrement R1 and loop

; till R1=0

RET ; return to calling program

The assembly program contain a main routine which start at address 0000H and it may or may not contain subroutines..In main program subroutine is invoked by the assembly instruction

## LCALL DELAY

Executing this instruction transfers the program flow to the memory address referenced by the 'LABEL' DELAY .While assembling the code a ';' inform the assembler that the rest of the part coming in a line after the ';' symbol is comments and simply ignore it •Each assembly instruction should be written in a separate line.More than one ASM code lines are not allowed in single line

•In the previous example LABEL DELAY represent the reference to the start of the subroutine

DELAY: MOV R0, #255 ;load Register R0 with 255

DJNZ R1, DELAY ;Decrement R1 and loop

; till R1=0

RET ;return to calling program

We can directly replace the LABEL by putting desired address first and then writing assembly code for the routine

**ORG** 0100H

MOV R0, #255 ;load Register R0 with 255

DJNZ R1, DELAY ;Decrement R1 and loop

; till R1=0

RET ;return to calling program

ORG 0100H is not an assembly language instruction; it is an assembler directive instruction. It tells the assembler that the instruction from here onwards should be placed at location starting from 0100H. Assembler directive instructions are known as 'pseudo ops'

They are used for

- -Determining the start address of the program (eg. ORG 0100H)

- -Determining the entry address of the program (eg. ORG 0100H)

- -Reserving the memory for data variables, arrays and structures (eg. Var EQU 70H)

- -Initializing variable values (e.g. val DATA 12H)

- ➤ EQU directive is used for allocating memory to a variable and DATA directive is used for initializing a variable with data

- ➤ No machine codes are generated for the 'Pseudo-ops'

- Assembly language program written in assembly code is saved as .asm file or an .src file

- ➤ Any text editor can be used for writing assembly instructions

- > Similar to other high level programming, you can have multiple source files called modules in assembly language programming.

- Each module is represented by .asm or .src file

- > This approach is known as modular programming

- ➤ Modular program is employed when program is too complex or too big.

- ➤ In modular programming the entire code is divided into sub modules and each module is made reusable

- ➤ Modular programs are usually easy to code, debug and alter

Conversion of assembly language into machine language is carried out by a sequence of operations

- 1. SOURCE FILE TO OBJECT FILE TRANSLATION

- 2. Library file creation and usage

- 3. Linker and Loader

- 4. Object to hex file convertor

- 1. SOURCE FILE TO OBJECT FILE TRANSLATION

- •Translation of assembly code to machine code is performed by assembler

- •The assemblers for different target machines are different and it is common that assemblers from multiple vendors are available in the market for the same target machines

- •Some assemblers are supplied by single vendor only

- •Some assemblers are freely available

- •Some are commercial and requires license from vendors

- -A51 Macro Assembler from Keil software is a popular assembler for 8051 family microcontroller

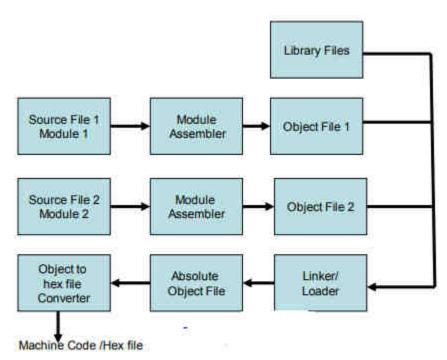

Fig . Assembling language to machine language convertion process

Each source module is written in assembly and is stored in .src or .asm file.Each file can be assembled separately to examine the syntax errors and incorrect assembly instructions.On assembling of each .src/.asm file a corresponding object file is created with extension .obj.The object file does not contain the absolute address of where the generated code need to be placed on the program memory and hence it is called relocatable segment. It can be placed at any code memory location and it is responsibility of the linker/loader to assign absolute address for this

module. Absolute address allocation is done at absolute object file creation stage. Each module can share variables and subroutine among them. Exporting a variable from a module is done by declaring that variable as PUBLIC in source module. Importing a variable or a function from a module is done by declaring that variable or function as EXTRN in the module where it is going to be accessed

- •PUBLIC keyword inform the assembler that the variable / function need to be exported

- •EXTRN inform that the variable/function need to be imported from some other modules

- •Corresponding to a variable /function declared as PUBLIC in a module, there can be one or modules using these variables/function using EXTRN keyword

- •For all those modules using variables or function with EXTRN keyword, there should be one and only one module which export those variables/functions PUBLIC keyword

- •If more than one module in a project tries to export variables or functions with the same name using PUBLIC keyword, it will generate linker errors

- •If a variable or function declared as EXTRN in one or two modules, there should be one module defining these variables or function and exporting them using PUBLIC keyword

- •If no module in a project export the variable or functions which are declared as EXTRN in other modules it will generate linker warnings or error depending on the error level/warning level setting of the linker

- 2. Library file creation and usage

- ➤ Libraries are specially formatted, ordered program collection of object modules that may be used by the linker at a later time

- ➤ When a linker process a library, only those object modules in the library that are necessary to create the program are used

- ➤ Library files are generated with the extension '.lib'

- ➤ Library file is some kind of source code hiding technique

- ➤ If you don't want to reveal the source code behind the various functions you have written in your program and at the same time you want them to be distributed to application developers for making use of them in their applications, you can supply them as library files and give them the details of the public functions available from the library

- For using a library file in a project, add library to the project

- ➤ If you are using a commercial version of assembler suit for your development, the vendor of utility may provide you pre written library files for performing multiplication, floating point arithematic, etc. as an add-on utility

## •Example LIB51 from keil software

## 3.Linker and Locator

- Linker and locator is another software utility responsible for" linking the various object modules in a multi module project and assigning absolute address to each module"

- Linker generate an absolute object module by extracting the object module from the library, if any and those obj files created by the assembler, which is generated by assembling the individual modules of a project

- ➤ It is the responsibility of the linker to link any external dependent variables or functions declared on various modules and resolve the external dependencies among the modules

- An absolute object file or modules does not contain any re-locatable code or data

- ➤ ALL code and data reside at fixed memory locations

- ➤ The absolute object file is used for creating hex files for dumping into the code memory of the processor/controller

- •Example 'BL51' from keil software

## 3. Object to Hex File Converter

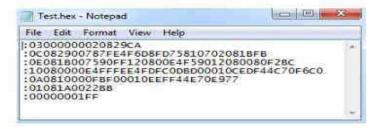

- ➤ This is the final stage in the conversion of Assembly language to machine understandable language

- ➤ Hex file is the representation of the machine code and the hex file is dumped into the code memory of the processor

- ➤ Hex file representation varies depending on the target processor make

- ➤ For intel processor the target hex file format willbe 'Intel HEX' and for Motorola, hex file should be in 'Motorola HEX' format

- ➤ HEX files are ASCII files that contain a hexadecimal representation of target application

- ➤ Hex file is created from the final 'Absolute Object File' using the Object to Hex file Converter utility

Example 'OH51' is an example utility for object to hex file convertor in8051 specific controller

# Advantage of Assembly Language based Development

Assembly language based development is the most common technique adopted from the beginning of the embedded technology development. Thorough understanding of the processor architecture, memory organization, register set and mnemonics is very essential for Assembly Language based Development. Following are the advantages of the same.

# 1. Efficient Code Memory and data Memory Usage (Memory Optimization)

- -Since the developer is well versed with the target processor architecture and memory organization, optimized code can be written for performing operations

- -This lead to the less utilization of code memory and efficient utilization of data memory

- -Memory is the primary concern in any embedded product

## 2. High Performance

- -Optimized code not only improve the code memory usage but also improve the total system performance

- -Though effective assembly coding optimum performance can be achieved for target applications

## 3. Low level Hardware access

-Most of the code for low level programming like accessing external device specific registers from the operating system kernel, device drivers and low level interrupt routine etc. are making use of direct assembly coding since low level device specific operation support is not commonly avail with most of the high level language compilers

# 4. Code Reverse Engineering

- -Reverse Engineering is the process of understanding the technology behind a product by extracting the information from the finished product

- -Reverse engineering is performed by 'hawkers' to reveal the technology behind the proprietary product

- -Though most of the product employ code memory protection, if it may be possible to break the memory protection and read the code memory, it can easily be converted into assembly code using dis-assembler program for the target machine

## DRAWBACKS OF ASSEMBLY LANGUAGE BASED DEVELOPMENT

# 1. High Development time

- -Assembly language programs are much harder to program than high level languages

- -Developer must have thorough knowledge of architecture, memory organization and register details of target processor in use

- -Learning the inner details of the processor and its assembly instructions are high time consuming and it create delay impact in product development

# 2. Developer Dependency

-There is no common rule for developing assembly language based applications whereas all high level language instruct certain set of rules for application development

- -In Assembly language programming, the developers will have the freedom to choose the different memory locations and registers

- -Also programming approach varies from developers to developers depending on their taste

- -For example moving a data from a memory location to accumulator can be achieved through different approaches

- -If the approach is done by a developer is not documented properly at the development stage, it may not be able to recollect at later stage or when a new developer is instruct to analyze the code, he may not be able to understand what is done and why it is done

- -Hence upgrading/modifying on later stage is more difficult. This can be solved by Well Documentation

## 3. Non-Portable

- -Target applications written in assembly instructions are valid only for that particular family of processors

- •Example—Application written for Intel X86 family of processors

- -Cannot be reused for another target processors

- -If the target processor changes, a complete rewriting of the application using assembly instructions for the new target processor is required

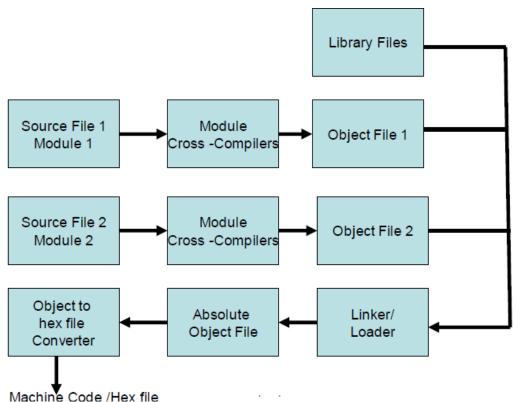

## HIGH LEVEL LANGUAGE BASED DEVELOPMENT

- Any High level language with supported cross compilers for the target processor can be used for embedded firmware development

- ➤ Cross Compilers are used for converting the application development in high level language into target processor specific assembly code

- ➤ Most commonly used language is C

- C is well defined easy to use high level language with extensive cross platform development tool support

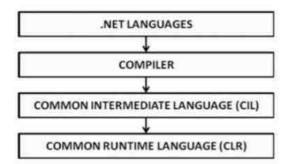

Fig:High level language to machine language convertion process

- > The program written in any of the high level language is saved with the corresponding language extension

- ➤ Any text editor provided by IDE tool supporting the high level language in use can be used for writing the program

- ➤ Most of the high level language support modular programming approach and hence you can have multiple source files called modules written in corresponding high level language

- ➤ The source file corresponding to each module is represented by a file with corresponding language extension

- > Translation of high level source code to executable object code is done by a cross compiler

- > The cross compiler for different high level language for same target processor are different

- ➤ Without cross-compiler support a high level language cannot be used for embedded firmware development

- -Example C51 Compiler fromKeil

# Advantages of High Level Languagebased Development

## 1. Reduced Development Time

- -Developers requires less or little knowledge on the internal hardware details and architecture of the target processor

- -Syntax of high level language and bare minimal knowledge of memory organization and register details of target processor are the only pre- requisites for high level language based firmware development

- -With High level language, each task can be accomplished by lesser number of lines of code compared to the target processor specific assemblylanguage based development

# 2. Developer Independency

- -The syntax used by most of the high level languages are universal and a program written in high level language can be easily be understood by a second person knowing the syntax of the language

- -High level language based firmware development makes the firmware , developer independent

- -High level language always instruct certain set of rules for writing code and commenting the piece of code

# 3. Portability

- -Target applications written in high level languages are converted to target processor understandable format by a cross compiler

- -An application written in high level language for a particular target processor can be easily converted to another target processor with little effort by simply recompiling the code modification followed by the recompiling the application for the required processor

- -This makes the high level language applications are highly portable

# Limitations of High level language based development

- > Some cross compilers avail for the high level languages may not be so efficient in generating optimized target processor specific instructions

- Target images created by such compilers may be messy and no optimized in terms of performance as well as code size

## MIXING ASSEMBLY AND HIGH LEVEL LANGUAGE

- ➤ High level language and assembly languages are usually mixed in three ways

- -Mixing assembly language with high level language

- -Mixing high level language with Assembly

- -In line assembly programming

# MixingAssemblyLanguagewith HighlevelLanguage (Assembly Language with 'C')

- Assembly routines are mixed with C in situations where entire program is written in C and the cross compiler in use do not have built in support for implementing certain features like Interrupt Service Routine or if the programmer want to take the advantage of speed and optimized code offered by machine code generated by hand written assembly rather than cross compiler generated machine code

- ➤ When accessing certain low level hardware, the timing specification may be very critical and a cross compiler generated binary may not be able to offer the required time specifications accurately

- ➤ Writing the hardware access routine in processor specific assembly language and invoking it from C is the most advised method to handle such situations

- •Mixing C and Assembly is little complicated in the sense-

- -the programmer must be aware of how parameters are passed from the C routine to Assembly and

- -values are returned from assembly routine to C and

- -how the assembly routine is invoked from the C code

- •These are cross compiler dependent

- •There is no universal rule for it

- •You must get the information from the documentation of cross compiler you are using

- •Different cross compilers implement these features in different ways depending upon the general purpose registers and the memory supported by the target processor

- The Example is to give an idea on how C%!cross compiler perform mixing of C with assembling language

- 1.Write a simple function in C that passes parameters and return values the way you want your assembly routine to

- 2.Use the SRC directive (#pragma SRC) so that C compiler generate an SRC file instead of .OBJ file

- 3.Compile the C code. Since the SRC directive is specified the .SRC file is generated. The .SRC file contain the assembly code generated for the C code you wrote

- 4.Rename .SRC to .A51 file

5.Edit .A51 file and insert the assembly code you want to execute in the body of the assembly function shell included in the .A51 file

As an example consider the following sample code (Extracted from Keil C51 documentation)

This C function on cross compilation generates the following assembly SRC file.

```

TESTCODE

NAME

?PR? my assembly func?TESTCODE

SEGMENT CODE

PUBLIC my assembly func

; #pragma SRC

; unsigned char my assembly func (

#pragma SRC

unsigned char my assembly func (unsigned int argument)

return (argument + 1); // Insert dummy lines to access all args and

// retvals

This C function on cross compilation generates the following assembly SRC file.

TESTCODE

NAME

?PR?_my assembly func?TESTCODE

SEGMENT CODE

PUBLIC my assembly func

```

; #pragma SRC

; unsigned char my assembly func (

```

RSEG ?PR? my_assembly_func?TESTCODE

USING 0

my_assembly_func:

;--- Variable 'argument?040' assigned to Register 'R6/R7' ----

; SOURCE LINE # 2

; unsigned int argument)

; {

SOURCE LINE # 4

; return (argument + 1); // Insert dummy lines to access all args

; and retvals

; SOURCE LINE # 5

MOV A,R7

INC A

MOV R7,R

; SOURCE LINE # 6

; CO001:

RET

; END OF _my_assembly_func

END

```

## Mixing high level language with assembly (Eg C with assembly language)

Mixing the code written in a high level language like 'C' and Assembly language is useful in the following scenarios:

- The source code is already available in Assembly language and a routine written in a high level language like 'C' needs to be included to the existing code.

- The entire source code is planned in Assembly code for various reasons like optimised code, optimal performance, efficient code memory utilisation and proven expertise in handling the Assembly, etc. But some portions of the code may be very difficult and tedious to code in Assembly. For example 16bit multiplication and division in 8051 Assembly Language.

- To include built in library functions written in 'C' language provided by the cross compiler. For example Built in Graphics library functions and String operations supported by 'C'.

Most often the functions written in 'C' use parameter passing to the function and returns value/s to the calling functions. The major question that needs to be addressed in mixing a 'C' function with Assembly is that how the parameters are passed to the function and how values are returned from the function and how the function is invoked from the assembly language environment. Parameters are passed to the function and values are returned from the function using CPU registers, stack memory and fixed memory. Its implementation is cross compiler dependent and it varies across cross compilers. A typical example is given below for the Keil C51 cross compiler

C51 allows passing of a maximum of three arguments through general purpose registers R2 to R7. If the three arguments are *char* variables, they are passed to the function using registers R7, R6 and R5

respectively. If the parameters are int values, they are passed using register pairs (R7, R6), (R5, R4) and (R3, R2). If the number of arguments is greater than three, the first three arguments are passed through registers and rest is passed through fixed memory locations. Refer to C51 documentation for more details. Return values are usually passed through general purpose registers. R7 is used for returning char value and register pair (R7, R6) is used for returning int value. The 'C' subroutine can be invoked from the assembly program using the subroutine call Assembly instruction (Again cross compiler dependent).

Cfunction E.g. LCALL

Where Cfunction is a function written in 'C'. The prefix informs the cross compiler that the parameters to the function are passed through registers. If the function is invoked without the \_ prefix, it is understood that the parameters are passed through fixed memory locations.

## **Inline Assembly**

Inline assembly is another technique for inserting target processor/controller specific Assembly instructions at any location of a source code written in high level language 'C'. This avoids the delay in calling an assembly routine from a 'C' code (If the Assembly instructions) to be inserted are put in a subroutine as mentioned in the section mixing assembly with 'C'). Special keywords are used to indicate that the start and end of Assembly instructions. The keywords are crosscompiler specific. C51 uses the keywords #pragma asm and #pragma endasm to indicate a block of code written in assembly.

#pragma asm MOV-A, #13H #pragma endasm

## **MODULE-1**

Introduction to Embedded System: Understanding the Basic Concepts, The Typical Embedded System - Characteristics and Quality attributes.

#### FUNDAMENTALS OF EMBEDDED SYSTEMS

#### **SYSTEM**

- A system is an arrangement in which all its unit assemble work together according to a set of rules.

- It can also be defined as a way of working, organizing or doing one or many tasks according to a fixed plan. For example, a watch is a time displaying system. Its components follow a set of rules to show time. If one of its parts fails, the watch will stop working. So we can say, in a system, all its subcomponents depend on each other.

### EMBEDDED SYSTEM

- Embedded means something that is attached to another thing.

- An embedded system can be thought of as a computer hardware system having software embedded in it.

- An embedded system can be an independent system or it can be a part of a large system. An embedded system is a microcontroller or microprocessor based system which is designed to perform a specific task.

For example, a fire alarm is an embedded system; it will sense only smoke.

- An embedded system has three components It has hardware. It has application software. It has Real Time Operating system that supervises the application software and provide mechanism to let the processor run a process as per scheduling by following a plan to control the latencies.

- RTOS defines the way the system works. It sets the rules during the execution of application program.

A small scale embedded system may not have RTOS.

- So we can define an embedded system as a Microcontroller based, software driven, and reliable, real-time control system.

- An embedded system is designed to do a specific job only. Example: a washing machine can only wash clothes, an air conditioner can control the temperature in the room in which it is placed.

- The hardware & mechanical components will consist all the physically visible things that are used for input, output, etc.

- An embedded system will always have a chip (either microprocessor or microcontroller) that has the code or software which drives the system.

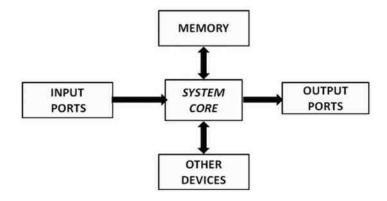

An embedded system is a combination of 3 things

- Hardware

- Software

- Mechanical Components

MGM CET, DEPT OF CSE

And it is supposed to do one specific task only. Diagrammatically an embedded system can be represented as follows:

## EMBEDDED SYSTEM & GENERAL PURPOSE COMPUTER

- The Embedded System and the General purpose computer are at two extremes.

- The embedded system is designed to perform a specific task

- The general purpose computer is meant for general use. It can be used for playing games, watching movies, creating software, work on documents or spreadsheets etc.

Following are certain specific points of difference between embedded systems and general purpose computers:

| Criteria                 | General Purpose<br>Computer                                                                             | Embedded system                                                                                          |

|--------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Contents                 | It is combination of generic hardware and a general purpose OS for executing a variety of applications. | It is combination of special purpose hardware and embedded OS for executing specific set of applications |

| Operating<br>System      | It contains general purpose operating system                                                            | It may or may not contain operating system.                                                              |

| Alterations              | Applications are alterable by the user.                                                                 | Applications are non-alterable by the user.                                                              |

| Key factor               | Performance" is key factor.                                                                             | Application specific requirements are key factors.                                                       |

| Power<br>Consumpti<br>on | More                                                                                                    | Less                                                                                                     |

| Response<br>Time         | Not Critical                                                                                            | Critical for some applications                                                                           |

Embedded computing systems have to provide sophisticated functionality:

- *Complex algorithms*: The operations performed by the microprocessor may be very sophisticated. For example, the microprocessor that controls an automobile engine must perform complicated filtering functions to optimize the performance of the car while minimizing pollution and fuel utilization.

- *User interface:* Microprocessors are frequently used to control complex user interfaces that may include multiple menus and many options. The moving maps in Global Positioning System (GPS) navigation are good examples of sophisticated user interfaces.

# To make things more difficult, embedded computing operations must often be performed to meet deadlines:

- **Real time:** Many embedded computing systems have to perform in real time—if the data is not ready by a certain deadline, the system breaks. In some cases, failure to meet a deadline is unsafe and can even endanger lives. In other cases, missing a deadline does not create safety problems but does create unhappy customers—missed deadlines in printers ,for example, can result in scrambled pages.

- *Multirate*: Not only must operations be completed by deadlines, but many embedded computing systems have several real-time activities going on at the same time. They may simultaneously control some operations that run at slow rates and others that run at high rates. Multimedia applications are prime examples of **multirate** behavior. The audio and video portions of a multimedia stream run at very different rates, but they must remain closely synchronized. Failure to meet a deadline on either the audio or video portions spoils the perception of the entire presentation.

### Costs of various sorts are also very important:

- *Manufacturing cost:* The total cost of building the system is very important in many cases. Manufacturing cost is determined by many factors, including the type of microprocessor used, the amount of memory required, and the types of I/O devices.

- **Power and energy:** Power consumption directly affects the cost of the hardware, since a larger power supply may be necessary. Energy consumption affects battery life, which is important in many applications, as well as heat consumption, which can be important even in desktop applications.

### CHARACTERISTICS OF AN EMBEDDED SYSTEM

Single-functioned – an embedded system usually performs a specialized operation and does the same repeatedly. For example: A pager always functions as a pager.

Page 4

- Tightly constrained All computing systems have constraints on design metrics, but those on an embedded system can be especially tight. Design metrics is a measure of an implementation's features such as its cost, size, power, and performance. It must be of a size to fit on a single chip, must perform fast enough to process data in real time and consume minimum power to extend battery life.

- Reactive and Real time Many embedded systems must continually react to changes in the system's environment and must compute certain results in real time without any delay. Consider an example of a car cruise controller; it continually monitors and reacts to speed and brake sensors. It must compute acceleration or de-accelerations repeatedly within a limited time; a delayed computation can result in failure to control of the car.

- Microprocessors based It must be microprocessor or microcontroller based.

- Memory It must have a memory, as its software usually embeds in ROM. It does not need any secondary memories in the computer.

- **Connected** It must have connected peripherals to connect input and output devices.

- **HW-SW systems** Software is used for more features and flexibility. Hardware is used for performance and security.

### APPLICATION OF EMBEDDED SYSTEM

The application areas and the products in the embedded domain are countless.

- 1. Consumer Electronics: Camcorders, Cameras.

- 2. Household appliances: Washing machine, Refrigerator.

- **3**. Automotive industry: Anti-lock breaking system (ABS), engine control.

- **4.** Home automation & security systems: Air conditioners, sprinklers, fire alarms.

- **5**. Telecom: Cellular phones, telephone switches.

- **6**. Computer peripherals: Printers, scanners.

- 7. Computer networking systems: Network routers and switches.

- **8**. Healthcare: EEG, ECG machines.

- 9. Banking & Retail: Automatic teller machines, point of sales.

- 10. Card Readers: Barcode, smart card readers.

MGM CET, DEPT OF CSE

## CHALLENGES IN EMBEDDED COMPUTING SYSTEM DESIGN

- How much hardware do we need?

- Control over the amount of computing power we apply to our problem.

- Select the type of microprocessor, amount of memory and the peripheral devices

- To meet both performance deadlines and manufacturing cost constraints, the choice of hardware is important

- Too little hardware and the system fail to meet its deadlines, too much hardware and it becomes too expensive.

- How do we meet deadlines?

- The brute force way of meeting a deadline is to speed up the hardware so that the program runs faster, that makes the system more expensive.

- It is also entirely possible that increasing the CPU clock rate may not make enough difference to execution time, since the program's speed may be limited by the memory system.

- \* How do we minimize power consumption?

- In battery-powered applications, power consumption is extremely important. Even in non-battery applications, excessive power consumption can increase heat dissipation.

- One way to make a digital system consume less power is to make it run more slowly, but naively slowing down the system can obviously lead to missed deadlines.

- Careful design is required to slow down the noncritical parts of the machine for power consumption while still meeting necessary performance goals.

- How do we design for upgradability?

- The hardware platform may be used over several product generations or for several different versions of a product in the same generation, with few or no changes.

- We want to be able to add features by changing software.

- > Does it really work?

- Reliability is always important when selling products

- Reliability is especially important in some applications, such as safety-critical systems.

Let's consider some ways in which the nature of embedded computing machines makes their design more difficult.

- *Complex testing:* Exercising an embedded system is generally more difficult than typing in some data. We may have to run a real machine in order to generate the proper data. The timing of data is often important, meaning that we cannot separate the testing of an embedded computer from the machine in which it is embedded.

- Limited observability and controllability: Embedded computing systems usually do not come with keyboards and screens. This makes it more difficult to see what is going on and to affect the system's operation. We may be forced to watch the values of electrical signals on the microprocessor bus, for example, to know what is going on inside the system. Moreover, in real-time applications we may not be able to easily stop the system to see what is going on inside.

■ **Restricted development environments:** The development environments for embedded systems (the tools used to develop software and hardware) are often much more limited than those available for PCs and workstations. We generally compile code on one type of machine, such as a PC, and download it onto the embedded system. To debug the code, we must usually rely on programs that run on the PC or workstation and then look inside the embedded system.

### PERFORMANCE IN EMBEDDED COMPUTING

- Embedded system designers have a very clear performance goal in mind—their program must meet its *deadline*. The heart of embedded computing is *real-time computing*

- The program receives its input data; the deadline is the time at which a computation must be finished. If the program does not produce the required output by the deadline, then the program does not work, even if the output that it eventually produces is functionally correct. This notion of deadline-driven programming is at once simple and demanding.

- We need tools to help us analyze the real-time performance of embedded systems; we also need to adopt programming disciplines and styles that make it possible to analyze these programs.

- In order to understand the real-time behavior of an embedded computing system, we have to analyze the system at several different levels of abstraction. Those layers include:

- *CPU*: The CPU clearly influences the behavior of the program, particularly when the CPU is a pipelined processor with a cache.

- *Platform:* The platform includes the bus and I/O devices. The platform components that surround the CPU are responsible for feeding the CPU and can dramatically affect its performance.

- **Program:** Programs are very large and the CPU sees only a small window of the program at a time. We must consider the structure of the entire program to determine its overall behavior.

- *Task:* We generally run several programs simultaneously on a CPU, creating a *multitasking system*. The tasks interact with each other in ways that have profound implications for performance.

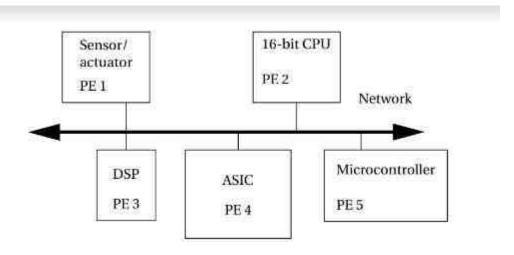

- *Multiprocessor:* Many embedded systems have more than one processor—they may include multiple programmable CPUs as well as accelerators. Once again, the interaction between these processors adds yet more complexity to the analysis of overall system performance.

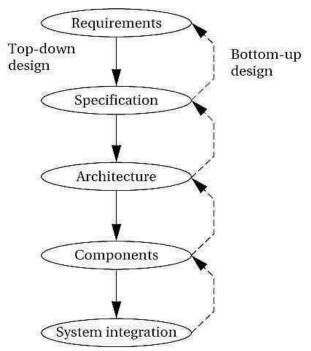

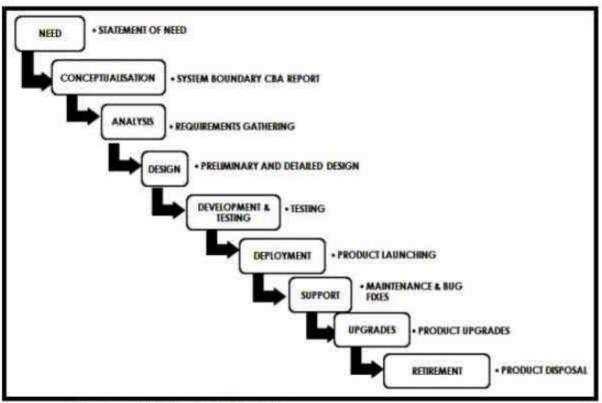

### THE EMBEDDED SYSTEM DESIGN PROCESS

The following figure summarizes the major steps in the embedded system design process. In this top—down view, we start with the system *requirements*.

In the next step, *specification*, we create a more detailed description of what we want. The specification states only how the system behaves, not how it is built.

Fig: Major levels of abstraction in the design process

The details of the system's internals begin to take shape when we develop the **architecture**, which gives the system structure in terms of large **components**. Once we know the components we need, we can design those components, including both software modules and any specialized hardware we need. Based on those components, we can finally build a complete system.

We also need to consider the major goals of the design:

- manufacturing cost

- **■** performance (both overall speed and deadlines)

- **■** power consumption.

We must also consider the tasks we need to perform at every step in the design process. At each step in the design, we add detail:

- We must *analyze* the design at each step to determine how we can meet the specifications.

- We must then *refine* the design to add detail.

- And we must verify the design to ensure that it still meets all system goals, such as cost, speed, and so on.

## 1. Requirements:

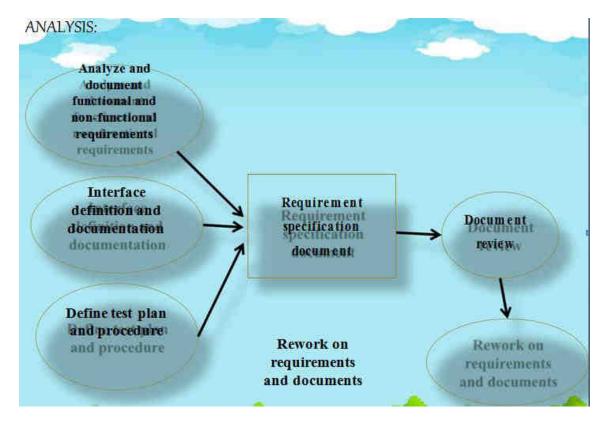

In first step we gather informal description from customers known as requirements, we then refine that requirement into a specification that contain enough information to start design. Reurements are of 2 types

- Fuctional Reurements

- -focused on function of the system

- Non functional Reurements

- -performance

- -cost

- -physical size and cost

- -Power consumption

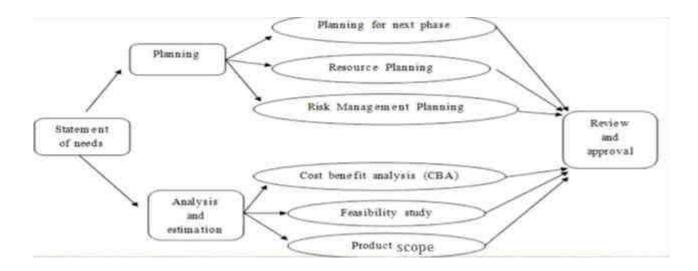

Requirement analysis of a large system is complex and time consuming .the following figure shows a sample requirement analysis form that need to filled during the start of a project.

#### Sample requirements form.

Name

Purpose

Inputs

Outputs

Functions

Performance

Manufacturing cost

Power

Physical size and weight

Name : Selection of name that depicts the theme of project

Purpose : One or two line description of what the system is supposed to do

Inputs and Outputs: Type of data, analog digital or mechanical input or output

Functions: Is a description of what the system does Performance: Measure of is the system work precisely?

Manufacturing cost: Cost of hardware, application software including all the cost involved in the

manufacturing

Power: Measure of how much power the system consume Physical size and weight: It guided to certain architectural design

### 2. Specification

- The specification is more precise—it serves as the contract between the customer and the architects.

- The specification must be carefully written so that it accurately reflects the customer's requirements and does so in a way that can be clearly followed during design.

- The specification should be understandable enough so that someone can verify that it meets system requirements and overall expectations of the customer

- meets system requirements and overall expectations of the customer.

It should also be unambiguous enough that designers know what they need to build.

- If global characteristics of the specification are wrong or incomplete, the overall system architecture derived from the specification may be inadequate to meet the needs of implementation.

MGM CET, DEPT OF CSE

### 3. Architecture

The specification does not say how the system does things, only what the system does.

- Describing how the system implements those functions is the purpose of the architecture.

- The architecture is a plan for the overall structure of the system that will be used later to design the components that make up the architecture.

- The creation of the architecture is the first phase of what many designers think of as design.

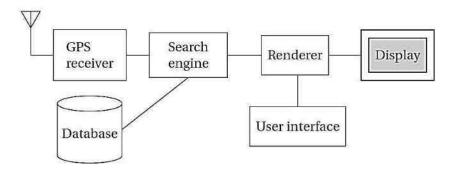

To understand what an architectural description is, let's look at sample architecture for the moving map. The moving map is a handheld device that displays for the user a map of the terrain around the user's current position; the map display changes as the user and the map device change position. The moving map obtains its position from the GPS, a satellite-based navigation system. Following figure shows sample system architecture in the form of a *block diagram* that shows major operations and data flows among them.

Fig: Block diagram for the moving map.

This block diagram is still quite abstract—we have not yet specified which operations will be performed by software running on a CPU, what will be done by special-purpose hardware, and so on.

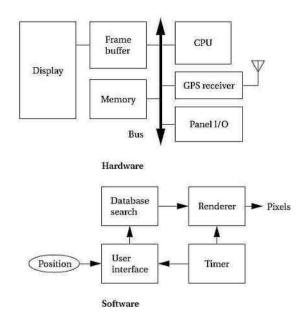

Fig: Hardware and software architectures for the moving map.

## 4. Designing Hardware and Software Components

- The architectural description tells us what components we need.

- The components will in general include both hardware—FPGAs, boards, and so on—and software modules.

- Some of the components will be ready-made. The CPU, for example, will be a standard component in almost all cases, as will memory chips and many other components.

- In the moving map, the GPS receiver is a good example of a specialized component that will nonetheless be a predesigned, standard component. We can also make use of standard software modules.

### 5.System Integration

- After component design the next step is to integrate them together and see whether the system works correctly as per the requirements.

- Many bugs appear only at this stage.

- Have a plan for integrating components to uncover bugs quickly, test as much functionality as early as possible.

## Formalism for system design

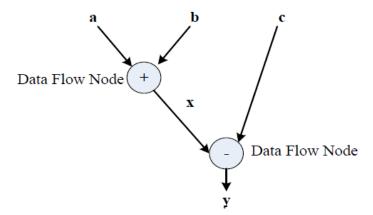

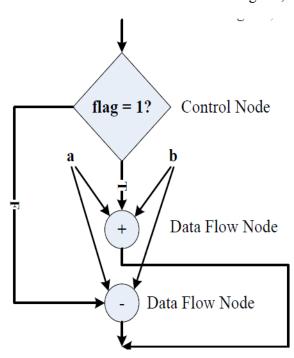

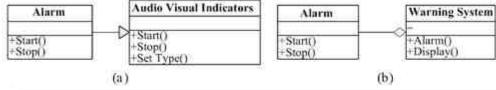

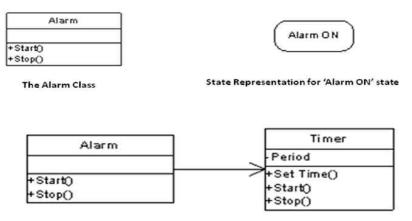

*Unified Modeling Language (UML)* - UML was designed to be useful at many levels of abstraction in the design process. UML is useful because it encourages design by successive refinement and progressively adding detail to the design, rather than rethinking the design at each new level of abstraction. UML is an *object-oriented* modeling language.

### **Structural Description**

- By *structural description*, we mean the basic components of the system.

- The principal component of an object-oriented design is the *object*. An object includes a set of *attributes* that define its internal state. When implemented in a programming language, these attributes usually become variables or constants held in a data structure.

- In some cases, we will add the type of the attribute after A class is a form of type definition—all objects derived from the same class have the same characteristics, although their attributes may have different values.

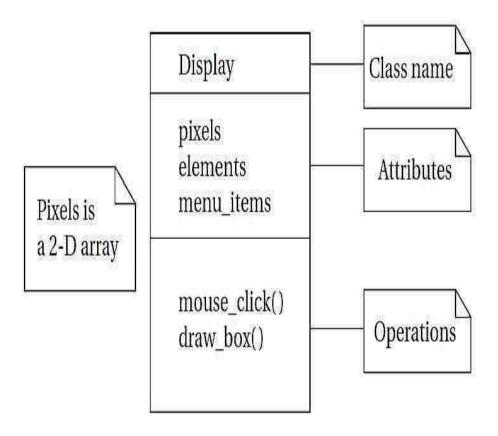

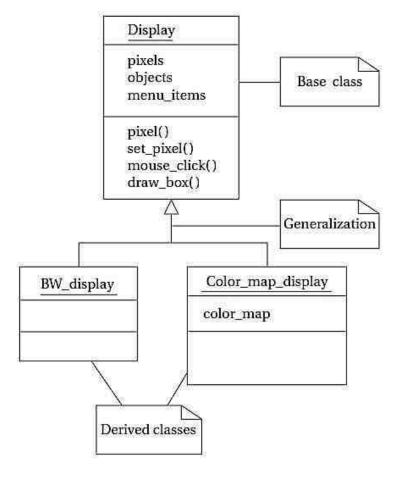

- A class defines the attributes that an object may have. It also defines the *operations* that determine how the object interacts with the rest of the world. In a programming language, the operations would become pieces of code used to manipulate the object. The UML description of the *Display* class is shown below

Fig: A class in UML notation

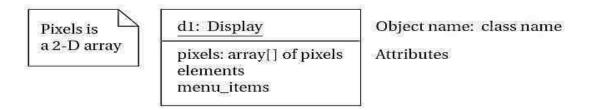

- The class has the name that we saw used in the d 1 object since d 1 is an instance of class **Display**.

- The **Display** class defines the *pixels* attribute seen in the object; remember that when we instantiate the class an object, that object will have its own memory so that different objects of the same class have their own values for the attributes.

- Other classes can examine and modify class attributes; if we have to do something more complex than use the attribute directly, we define a behavior to perform that function.

- A class defines both the *interface* for a particular type of object and that object's *implementation*.

- When we use an object, we do not directly manipulate its attributes—we can only read or modify the object's state through the operations that define the interface to the object.

Fig: An object in UML notation.

### There are several types of *relationships* that can exist between objects and classes:

- *Association* occurs between objects that communicate with each other but have no ownership relationship between them.

- Aggregation describes a complex object made of smaller objects.

- *Composition* is a type of aggregation in which the owner does not allow access to the component objects.

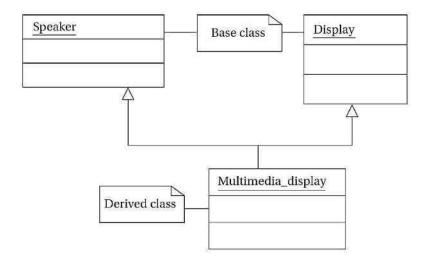

- *Generalization* allows us to define one class in terms of another.

Unified Modeling Language allows us to define one class in terms of another. An example is shown below, where we derive two particular types of displays. The first, BW\_display, describes a black- and-white display. This does not require us to add new attributes or operations, but can specialize both to work on one-bit pixels. The second, Color\_map\_display, uses a graphic device known as a color map to allow the user to select from behaviors—for example, large

number of available colors even with a small number of bits per pixel. This class defines a *color map* attribute that determines how pixel values are mapped onto display colors.

Fig: Derived classes as a form of generalization in UML.

- A derived class inherits all the attributes and operations from its base class.

- In this class, *Display* is the base class for the two derived classes. A derived class is defined to include all the attributes of its base class.

- This relation is transitive—if *Display* were derived from another class, both *BW\_display* and *Color\_map\_display* would inherit all the attributes and operations of *Display*'s base class as well.

- Vnified Modeling Language considers inheritance to be one form of generalization. A generalization relationship is shown in a UML diagram as an arrow with an open (unfilled) arrowhead.

- UML also allows us to define *multiple inheritances*, in which a class is derived from more than one base class.

Fig: Multiple inheritances in UML.

- In the above figure we have created a *Multimedia\_display* class by combining the *Display* class with a *Speaker* class for sound.

- The derived class inherits all the attributes and operations of both its base classes, *Display* and *Speaker*.

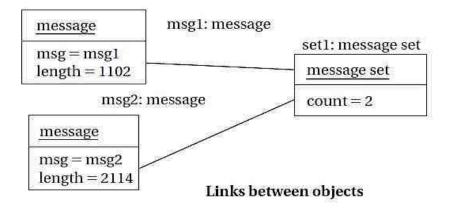

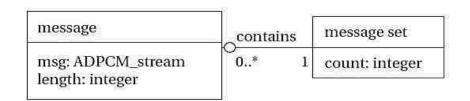

- A *link* describes a relationship between objects; association is to link as class is to object. Following figure shows examples of links and an association

Association between classes

- When we consider the actual objects in the system, there is a set of messages that keeps track of the current number of active messages (two in the above example) and points to the active messages. In this case, the link defines the *contains* relation.

- The association is drawn as a line between the two labeled with the name of the association, namely, *contains*.

## **Behavioral Description**

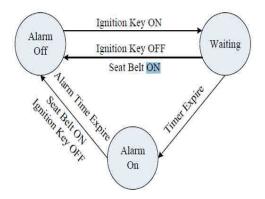

We have to specify the behavior of the system as well as its structure. One way to specify the behavior of an operation is a *state machine*. Following figure shows UML states; the transition between two states is shown by a skeleton arrow.

Fig: A state and transition in UML.

- The state machines will not rely on the operation of a clock, as in hardware; rather, changes from one state to another are triggered by the occurrence of *events*.

- An event is some type of action. The event may originate outside the system, such as a user pressing a button. It may also originate inside, such as when one routine finishes its computation and passes the result on to another routine.

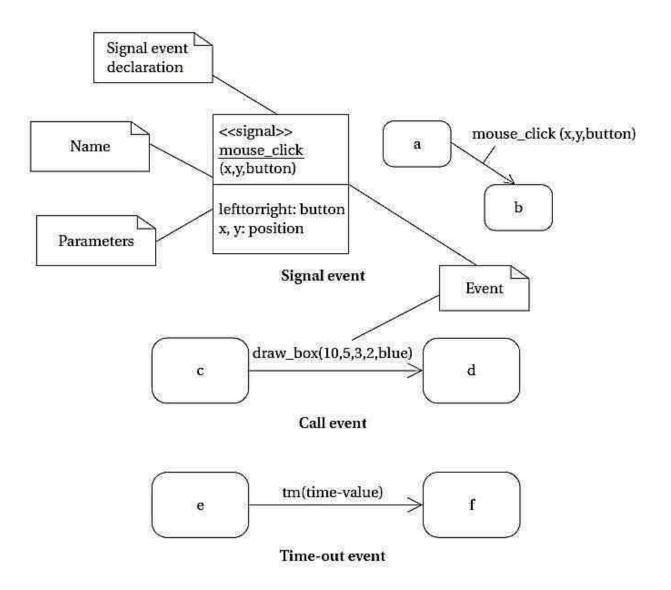

- The three types of events defined by UML are

- 1. A *signal* is an asynchronous occurrence. It is defined in UML by an object that is labeled as a << *signal*>>. The object in the diagram serves as a declaration of the event's existence. Because it is an object, a signal may have parameters that are passed to the signal's receiver.

- 2. A *call event* follows the model of a procedure call in a programming language.

- 3. *time-out event* causes the machine to leave a state after a certain amount of time. The label *tm(time-value)* on the edge gives the amount of time after which the transition occurs. A time-out is generally implemented with an external timer. This notation simplifies the specification and allows us to defer implementation details about the time-out mechanism.

Fig: Signal, call, and time-out events in UML.

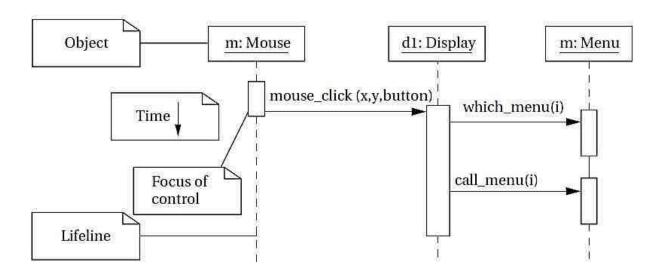

## sequence diagram

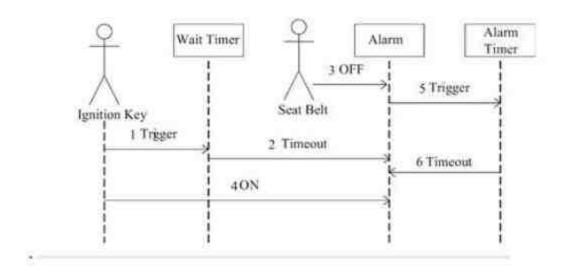

- It is sometimes useful to show the sequence of operations over time, particularly when several objects are involved. In this case, we can create a sequence diagram, like the one for a mouse click scenario shown below

- A sequence diagram is somewhat similar to a hardware timing diagram,

- The time flows vertically in a sequence diagram, whereas time typically flows horizontally in a timing diagram.

- The sequence diagram is designed to show a particular scenario or choice of events

- In the following *sequence diagram*, the sequence shows what happens when a mouse click is on the menu region. Processing includes three objects shown at the top of the diagram. Extending below each object is its *lifeline*, a dashed line that shows how long the object is alive. In this case, all the objects remain alive for the entire sequence, but in other cases objects may be created or destroyed during processing. The boxes along the

lifelines show the *focus of control* in the sequence, that is, when the object is actively processing. In this case, the mouse object is active only long enough to create the *mouse\_click* event. The display object remains in play longer; it in turn uses call events to invoke the menu object twice: once to determine which menu item was selected and again to actually execute the menu call. The find\_region() call is internal to the display object, so it does not appear as an event in the diagram.

Fig: A sequence diagram in UML.

## CHARACTERISTICS OF EMBEDDED SYSTEM

Following are some of the characteristics of an embedded system that make it different from a general purpose computer:

# 1. Application and Domain specific

An embedded system is designed for a specific purpose only. It will not do any other task.

Ex. A washing machine can only wash, it cannot cook

Certain embedded systems are specific to a domain: ex. A hearing aid is an application that belongs to the domain of signal processing.

## 2. Reactive and Real time

Certain Embedded systems are designed to react to the events that occur in the nearby environment. These events also occur real-time.

Ex. An air conditioner adjusts its mechanical parts as soon as it gets a signal from its sensors to increase or decrease the temperature when the user operates it using a remote control. An embedded system uses Sensors to take inputs and has actuators to bring out the required functionality.

## 3. Operation in harsh environment

Certain embedded systems are designed to operate in harsh environments like very high temperature of the deserts or very low temperature of the mountains or extreme rains.

These embedded systems have to be capable of sustaining the environmental conditions it is designed to operate in.

#### 4. Distributed

Certain embedded systems are part of a larger system and thus form components of a distributed system.

These components are independent of each other but have to work together for the larger system to function properly.

Ex. A car has many embedded systems controlled to its dash board. Each one is an independent embedded system yet the entire car can be said to function properly only if all the systems work together.

## 5. Small size and weight

An embedded system that is compact in size and has light weight will be desirable or more popular than one that is bulky and heavy.

Ex. Currently available cell phones. The cell phones that have the maximum features are popular but also their size and weight is an important characteristic. For convenience users prefer mobile phones than phablets. (phone + tablet pc)

#### 6. Power concerns

It is desirable that the power utilization and heat dissipation of any embedded system be low.

If more heat is dissipated then additional units like heat sinks or cooling fans need to be added to the circuit.

If more power is required then a battery of higher power or more batteries need to be accommodated in the embedded system.

## QUALITY ATTRIBUTES OF EMBEDDED SYSTEM

These are the attributes that together form the deciding factor about the quality of an embedded system.

There are two types of quality attributes are:-

## **Operational Quality Attributes.**

These are attributes related to operation or functioning of an embedded system. The way an embedded system operates affects its overall quality.

## Non-Operational Quality Attributes.

These are attributes **not** related to operation or functioning of an embedded system. The way an embedded system operates affects its overall quality.

These are the attributes that are associated with the embedded system before it can be put in operation.

## **Operational Attributes**

## 1. Response

Response is a measure of quickness of the system. It gives you an idea about how fast your system is tracking the input variables.

Most of the embedded system demand fast response which should be real-time.

## 2. Throughput

Throughput deals with the efficiency of system.

It can be defined as rate of production or process of a defined process over a stated period of time. In case of card reader like the ones used in buses, throughput means how much transaction the reader can perform in a minute or hour or day.

## 3. Reliability

Reliability is a measure of how much percentage you rely upon the proper functioning of the system.

Mean Time between failures and Mean Time To Repair are terms used in defining system reliability.

Mean Time between failures can be defined as the average time the system is functioning before a failure occurs.

Mean time to repair can be defined as the average time the system has spent in repairs.

## 4. Maintainability

Maintainability deals with support and maintenance to the end user or a client in case of technical issues and product failures or on the basis of a routine system checkup

It can be classified into two types:-

#### **Scheduled or Periodic Maintenance**

This is the maintenance that is required regularly after a periodic time interval.

## Example:

Periodic Cleaning of Air Conditioners

Refilling of printer cartridges.

## Maintenance to unexpected failure

This involves the maintenance due to a sudden breakdown in the functioning of the system.

## Example:

Air conditioner not powering on

Printer not taking paper in spite of a full paper stack

## 5. Security

Confidentiality, Integrity and Availability are three corner stones of information security. Confidentiality deals with protection data from unauthorized disclosure. Integrity gives protection from unauthorized modification.

Availability gives protection from unauthorized user

Certain Embedded systems have to make sure they conform to the security measures.

Ex. An Electronic Safety Deposit Locker can be used only with a pin number like a password.

## Safety

Safety deals with the possible damage that can happen to the operating person and environment due to the breakdown of an embedded system or due to the emission of hazardous materials from the embedded products.

A safety analysis is a must in product engineering to evaluate the anticipated damage and determine the best course of action to bring down the consequence of damages to an acceptable level.

## **Non Operational Attributes**

## 1. Testability and Debug-ability

- It deals with how easily one can test his/her design, application and by which mean he/she can test it.

- In hardware testing the peripherals and total hardware function in designed manner

- Firmware testing is functioning in expected way

- Debug-ability is means of debugging the product as such for figuring out the probable sources that create unexpected behavior in the total system

## 2. Evolvability

• For embedded system, the qualitative attribute "Evolvability" refer to ease with which the embedded product can be modified to take advantage of new firmware or hardware technology.

## 3. Portability

- o Portability is measured of "system Independence".

- An embedded product can be called portable if it is capable of performing its operation as it is intended to do in variousenvironments irrespective of different processor and or controller and embedded operating systems.

## 4. Time to prototype and market

Time to Market is the time elapsed between the conceptualization of a product and time at which the product is ready for selling or use

Product prototyping help in reducing time to market.

Prototyping is an informal kind of rapid product development in which important feature of the under consider are develop.

In order to shorten the time to prototype, make use of all possible option like use of reuse, off the self component etc.

#### 5. Per unit and total cost

Cost is an important factor which needs to be carefully monitored. Proper market study and cost benefit analysis should be carried out before taking decision on the per unit cost of the embedded product.

When the product is introduced in the market, for the initial period the sales and revenue will be low

There won't be much competition when the product sales and revenue increase.

During the maturing phase, the growth will be steady and revenue reaches highest point and at retirement time there will be a drop in sales volume.

## **MODULE 4**

## **Integration of Hardware & Firmware**

Integration of hardware and firmware deals with the embedding of firmware into the target hardware board. It is the process of 'Embedding Intelligence' to the product. The embedded processors/controllers used in the target board may or may not have built in code memory. For non-operating system based embedded products, if the processor/controller contains internal memory and the total size of the firmware is fitting into the code memory area, the code memory is downloaded into the target controller/processor. If the processor/controller does not support built in code memory or the size of the firmware is exceeding the memory size supported by the target processor/controller, an external dedicated EPROM/FLASH memory chip is used for holding the firmware. This chip is interfaced to the processor/control-

- Out-of-Circuit Programming

- In System Programming(ISP)

- In Application Programming

- Use of Factory programmed chip

#### **Out-of-Circuit Programming**

Its performed outside the target board

- The processor or memory chip into which the firmware needs to be embedded is taken out of the target board and its programmed with the programming device

- The programming device is a dedicated unit which contains the necessary hardware circuits generate the programming signals

- Most of this devices are capable to support different family of devices

- The programmer contains ZIF socket locking pin to hold the device to be programmed

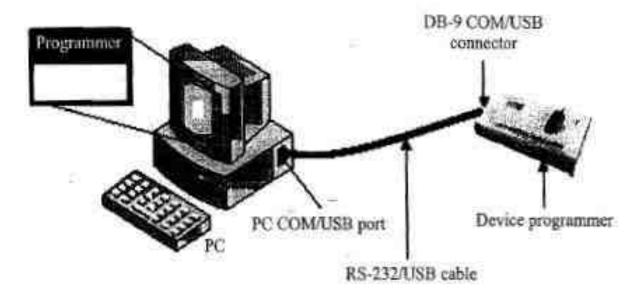

- Programmer is interfaced to pc through RS232/USB/Parallel port interface

# Interfacing of device programmer with pc

- The sequence of operations for embedded firmware with a programmer is

- 1. Connect the programming device to specified port(USB/COM/Parallel port)

- 2. Power up the device

- 3. Execute the programming utility on the pc and ensure proper connectivity between pc and programmer

- 4. Unlock the ZIF socket by turning the lock pin

- 5. Insert the device to be programmed into the open socket

- 6. Lock ZIP socket

- 7. Select the device name from the list of supported devices

- 8. Load the hex file which is to be embedded into the device

- 9. Program the device by program option of utility program

- 10. Wait till the completion of programming operation

- 11. Ensure that programming is successful by checking the status LED on the programmer

- 12. Unlock the ZIF socket & take device out of programmer

If security is required, enable the memory protection on the utility before programming the device

Only EEPROM/FLASH memory are erasable

#### **Drawback**

- 1. High development time

- 2. Not suitable for batch production(Option Gang programmer)

- 3. Very difficult to update firmware(Especially after the product is released)

#### **In System Programming**

- Firmware is embedded into the target device without removing it from the target board

- The target device must have ISP support

- Normally serial interface communication and protocols preferred

- ISP with SPI(Serial peripheral interface) protocol

- The primary i/o lines in this methods are

**MOSI**

**MISO**

**SCK**

**RST**

**GND**

- PC acts as master and target device acts like slave in ISP

- The key player behind ISP is a factory programmed memory called boot ROM.

- It contains a set of low level instruction APIs and those APIs allows the mc/p to perform flash programming

- ISP with SPI protocol-Programming e.g for Atmel AT 89S

- 1. Apply supply voltage b/w VCC and GND pin of target chip

- 2. Set RST pin to HIGH

- 3. If crystal is not connected across pins XTAL1 and XTAL2,apply 3 to 24 Mhz clock to XLAL1 and wait for 10s

- 4. Enable serial programming by sending the programming enable serial instruction to pin MOSI/P1.5

- 5. The code or data array is programmed one byte at a time by supplying the address and data together with the appropriate write instruction

- 6. Any memory location is verified by using read instruction, which returns the content at the selected address at serial output MISO/P1.6

- 7. After successfully programming the device, set RST to low or turn off the chip power supply and turn it to ON to commence the normal operation

## In Application Programming

- It's a technique used by firmware running on the target device for modifying a selected portion of the code memory

- It modifies the program code memory under the control of embedded application including updating calibration data, look up tables etc

## **Use of factory Programmed Chip**

- Here embed the firmware into the target processor/controller memory at the time of chip fabrication itself

- Once the firmware design is over and the firmware achieved operational stability, the firmware files can be sent to the chip fabricator to embed it into the code memory

- It reduces the product development time.

## Firmware Loading for OS based devices

- Its programmed using ISP technique

- OS based system contain a special piece of code called boot loader program which takes control of the OS and application firmware embedding and copying of the OS images to the RAM of the system for execution

- Boot loader contains necessary driver initialization implementation for initializing the support interface like UART,TCP/IP etc

- E.g. Load from FLASH ROM, Load from network ,Load through UART etc

The Embedded System Development Environment

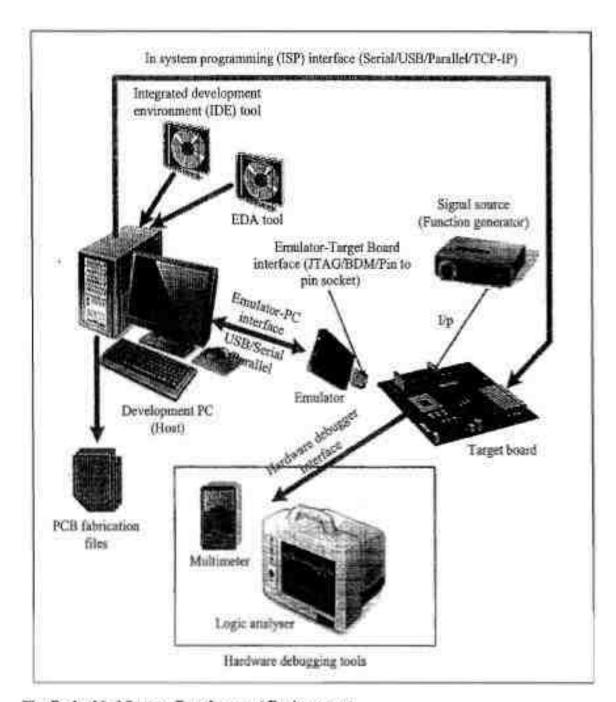

### EMBEDDED SYSTEM DEVELOPMENT ENVIRONMENT

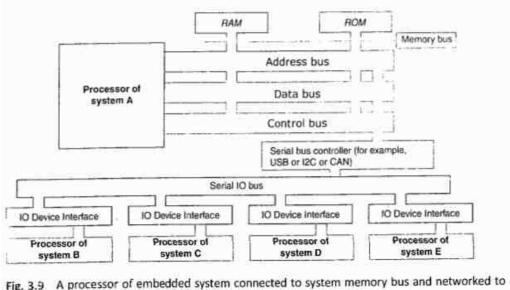

•The most important characteristic of E.S is the cross-platform development technique.

- •The primary components in the development environment are the host system, the target system and many connectivity solutions between the host and the target E.S.

- •The development tools offered by the host system are the cross complier, linker and source-level debugger.

- •The target embedded system offers a dynamic loader, link loader, a monitor and a debug agent.

- •Set of connections are required between the source computer and the target system.

- •These connections can be used for transmitting debugger information between the host debugger and the target debug agent.

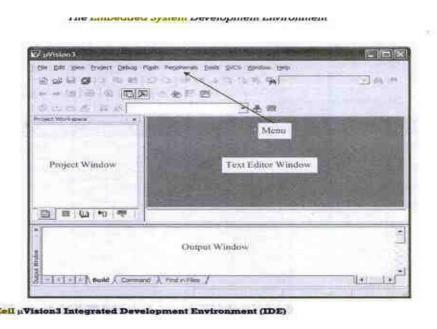

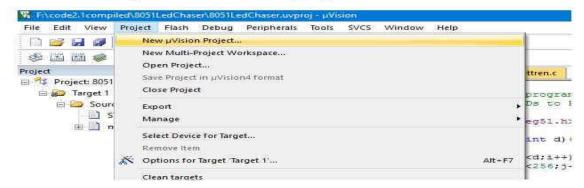

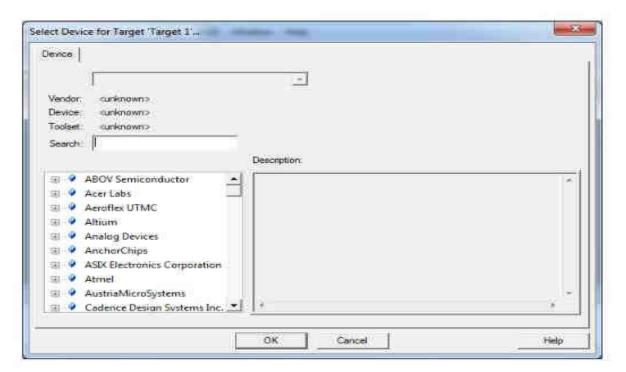

## IDE

- In E.S, IDE stands for an integrated environment for developing and debugging the target processor specific embedded firmware

- An IDE is also known as integrated design environment or integrated debugging environment.

- IDE is a software package which bundles a "Text Editor", "Cross-compiler", "Linker" and a "Debugger"

- IDE is a software application that provides facilities to computer programmers for software development. IDEs can either command line based or GUI based

## **IDE Components**

- 1. Text Editor or Source code editor

- 2.A compiler and an

interpreter

3. Build automation

tools 4.Debugger

- 5. Simulators

- 6. Emulators and logic analyzer

E.g. Turbo C/C++, Microsoft visual c++ etc

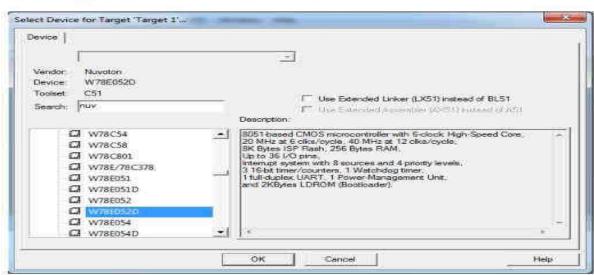

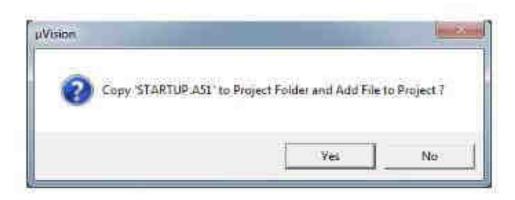

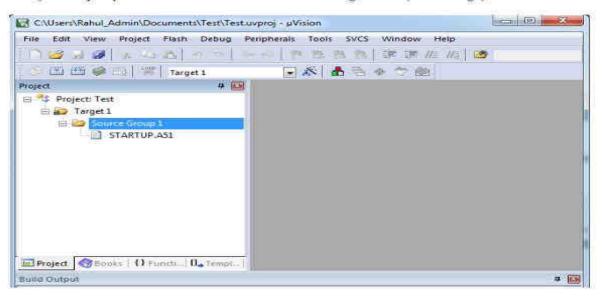

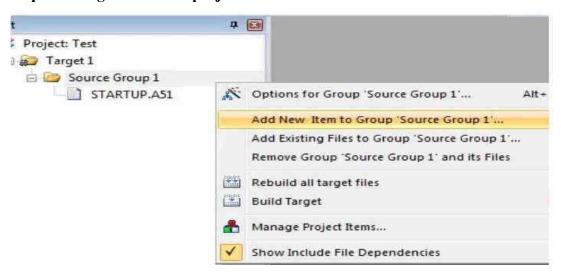

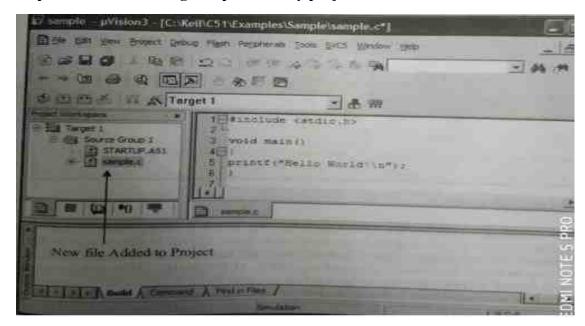

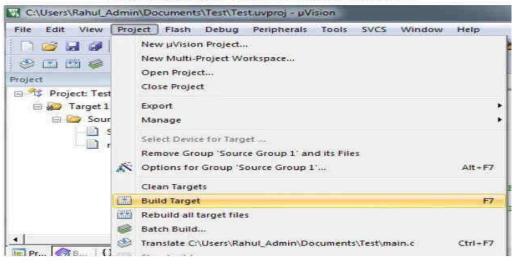

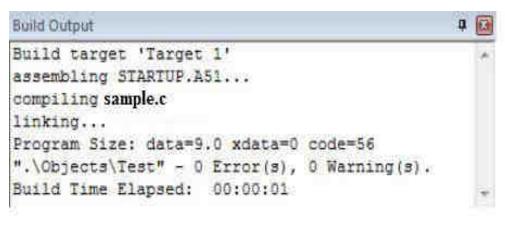

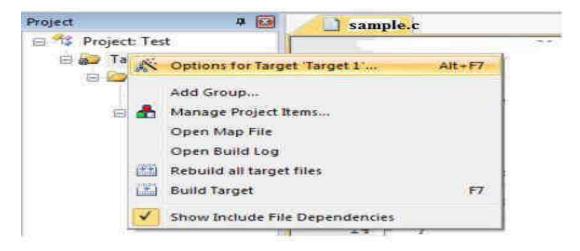

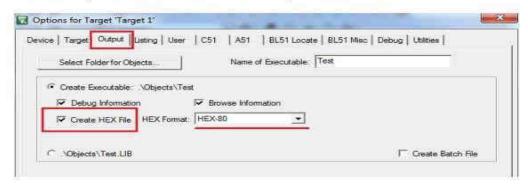

## Keil uVersion3 IDE for 8051