# BJT Bipolan Junction Transiston

pap bransistor upn biansiston &

npn

pnp

3 terminals = 2 emitter (E), Base (B), collector (C)

Emitter = heavily doped, moderate surface area

Base = Lightly doped, small surface area

collector = Moderately deped, large surface area

configuration => 1) common base

2) common emitter

3) Common collector

In a bransistors there are two types of characteristics. they are

Dilp characteristics ochotonship b/w i/p correct & ilp Vollege at const. Olp Vallege

2) o/p characteristics = notationship b/w o/p current & o/p voltage at cons. i/p current

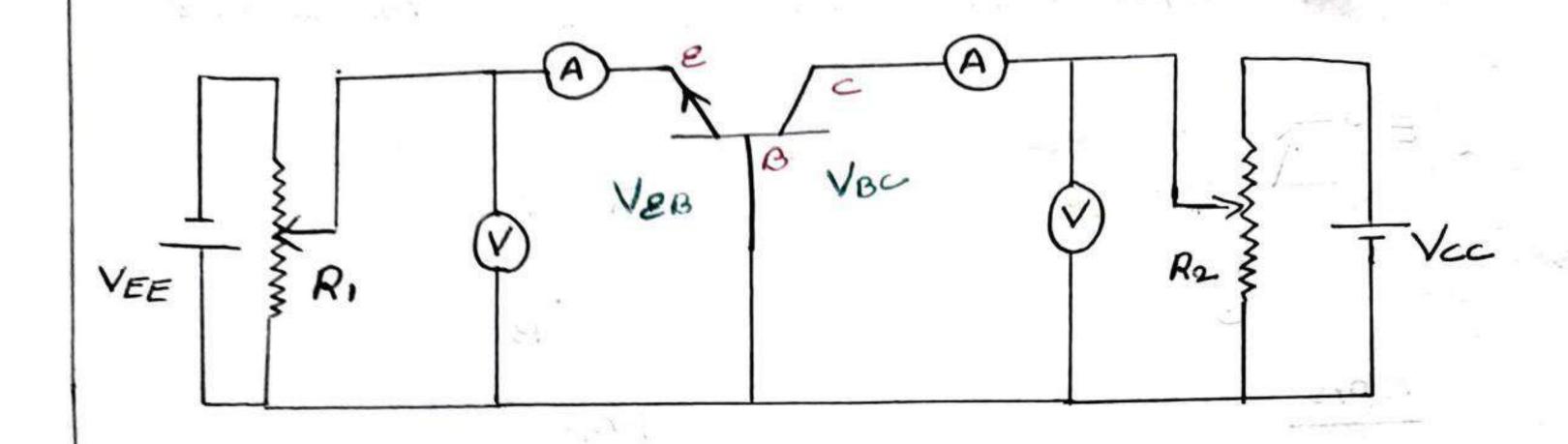

# Common Base Configuration

Hore base is common to olp & ilp

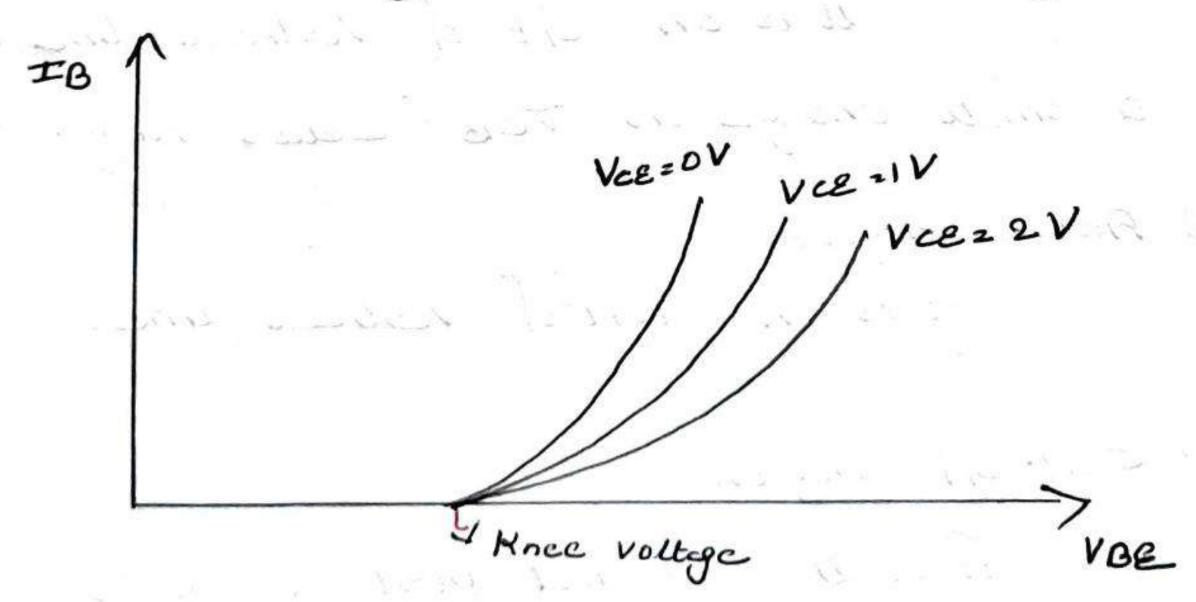

ilp chara

First adjust VCB (olp Vallege) to a fixed value then adjust R. & take ammeter & vollmeter readings. Plat a graph but VeB (ilp Vallege) & IE (ilp current)

The Vollege at rulich, current just starts Placeting is called knee vollege, it is 05 V for silicon & 0.1 V for

germarion

Up nosistance Ri = A Veb A IE.

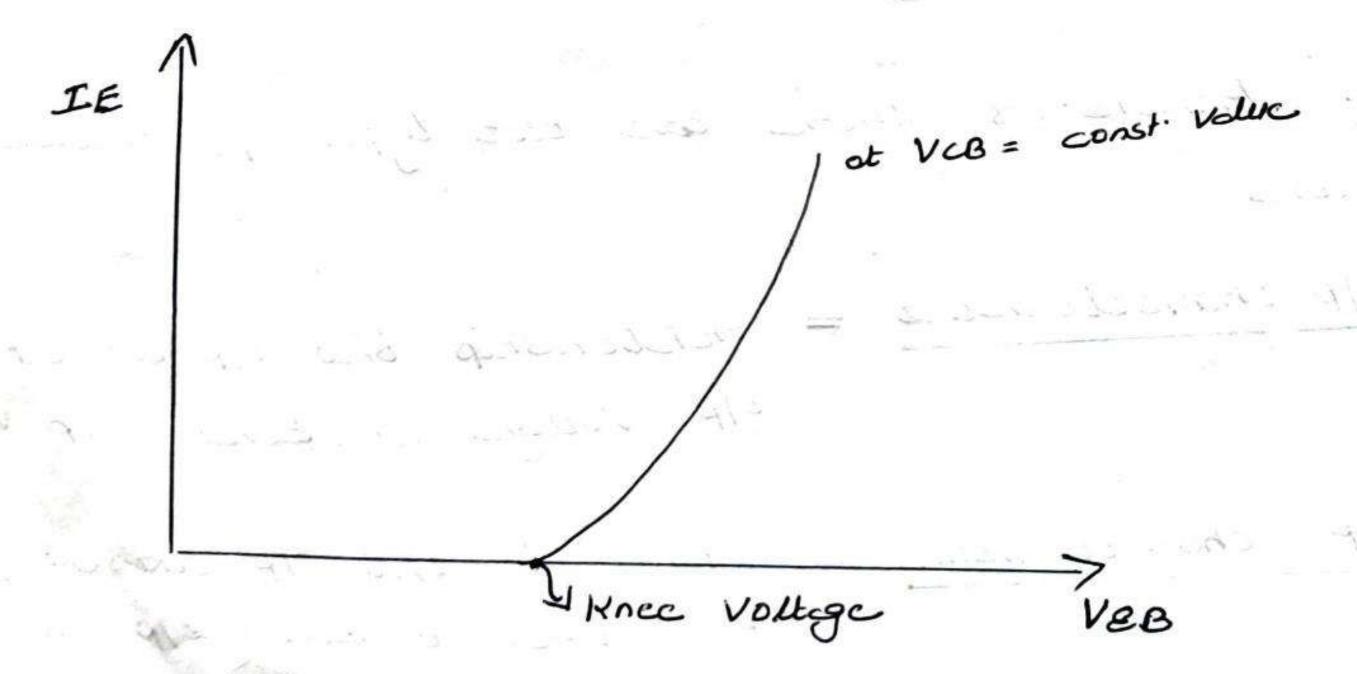

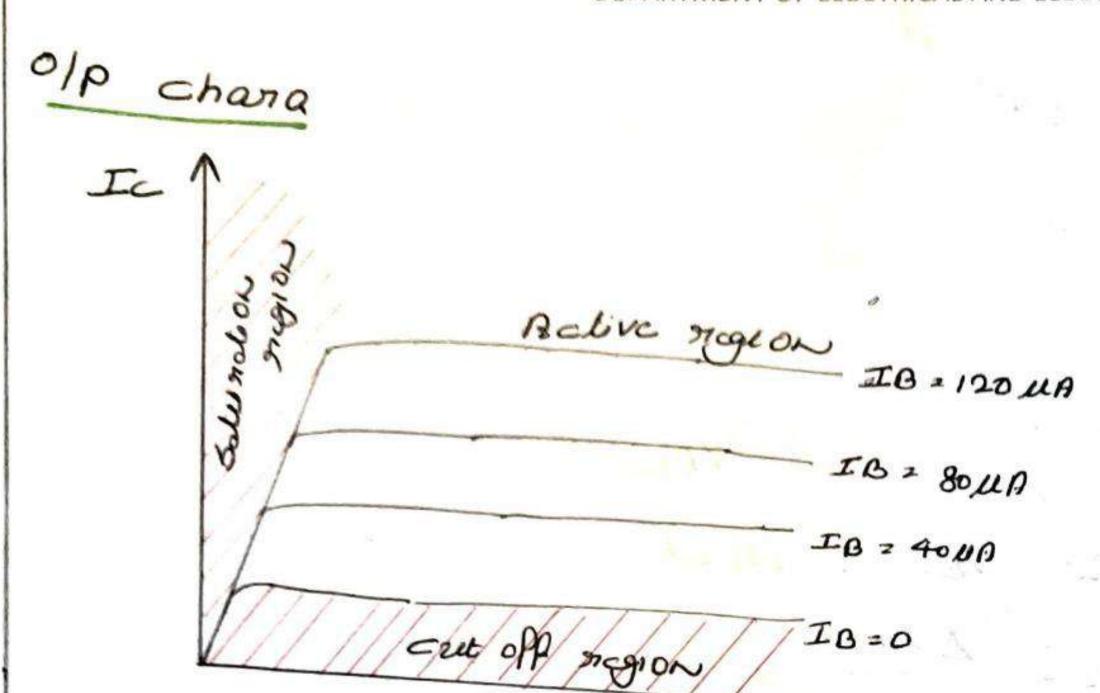

## Olp chang

Recping IE Cilp avancent) at constant value, increase VCB & conscapending Ie is measured. Plat a graph Earth VCB along X-axis & Ic along Y-axis.

The curve may be divided into 3 main organos.

De Solvation organ

It is on left of Vertical line. In this region a small charge in VCB cause large Variation in Ic

b) Active origion the son ought of vertical line.

E Cut off majon

It is the shaded partion. In this region both Junctions are neverse blooked.

Ofp nowstance Ro. AVCB

Crossort amplification Pactor (d) = DIC DIE

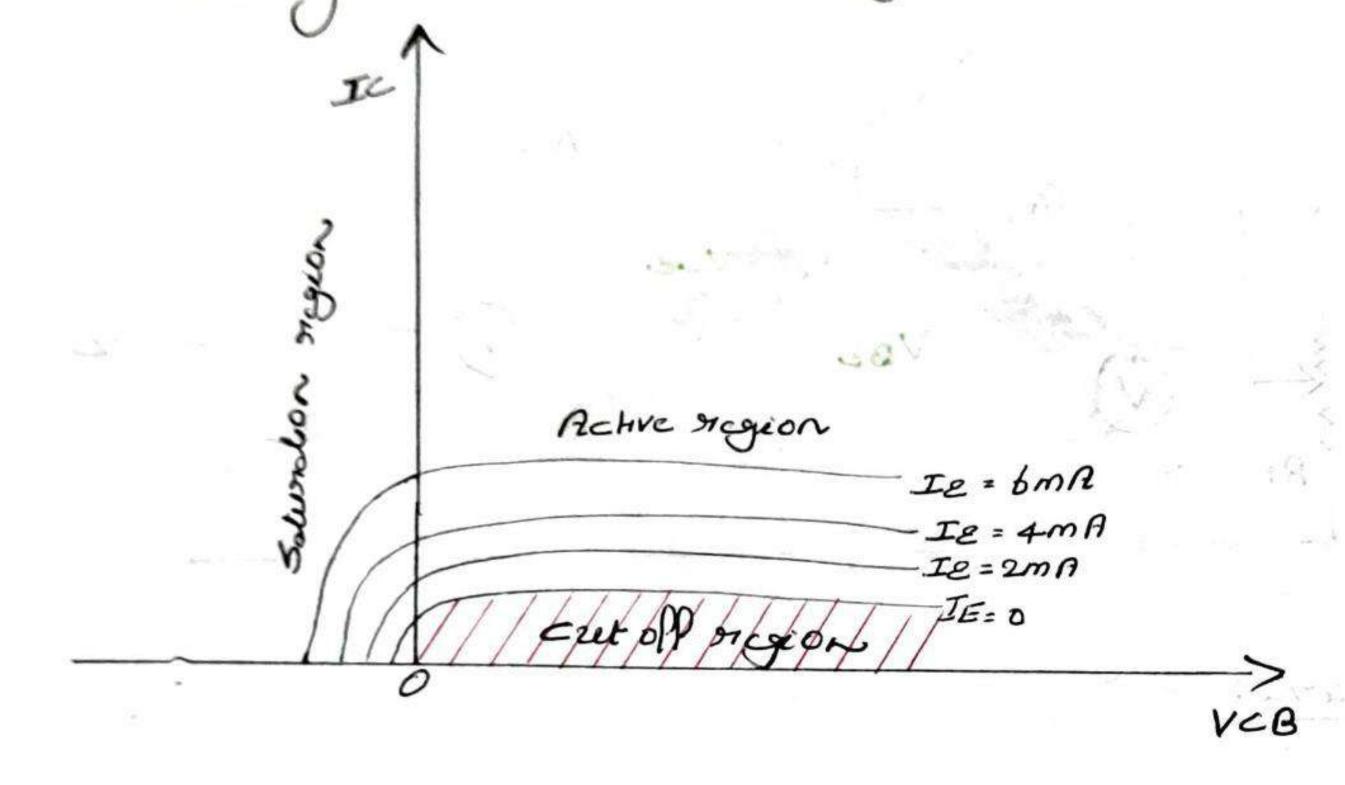

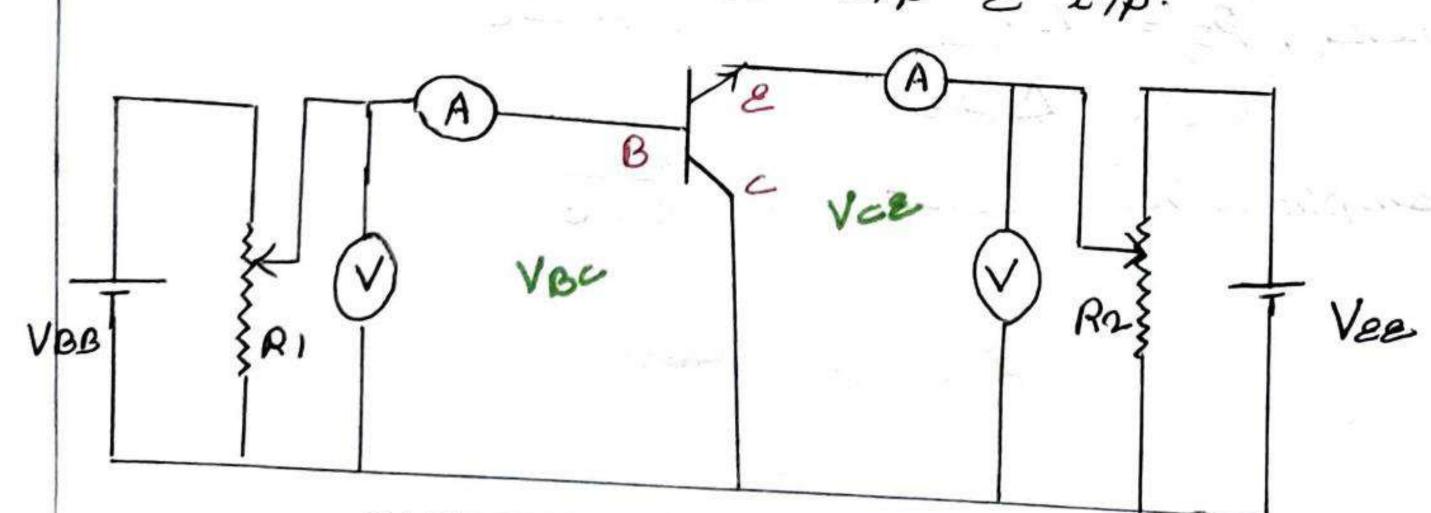

Common Emittos Configuration

Hore comittor is common to 0/P & ilp

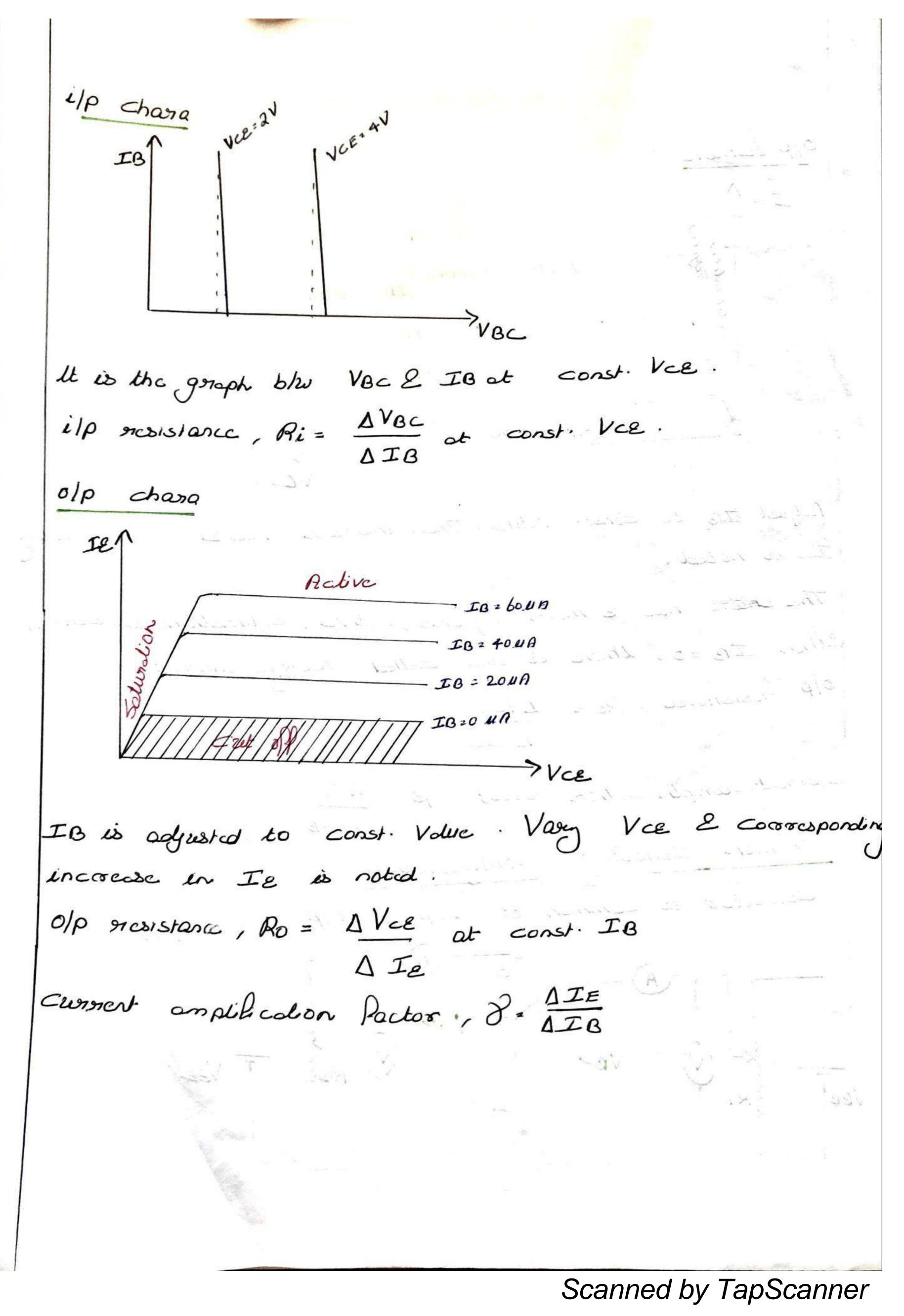

## ilp chara:

Vce is Kept const, Then encoresse VBE & IB is noted.

Plot graph with VBE dong X. axis & IB dong Y. axis.

ilp nosistance Riz AVBE at const Vce

Adjust IB to const. Volue. Then incoresse Vee 2. Coascobonding

The chara has 3 main regions, active, saturation & cut-off Euthor IB = 0, there is Ic colled leaking work. Olp mosistance, Ro = DVCE

current amplification factor, B = AIC

Common Collector Configuration Collector is common so olp & ilp.

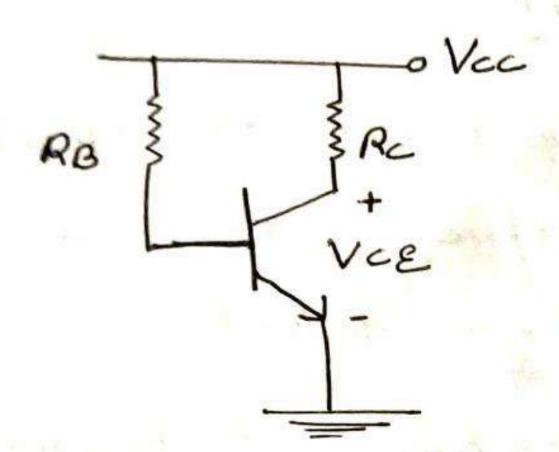

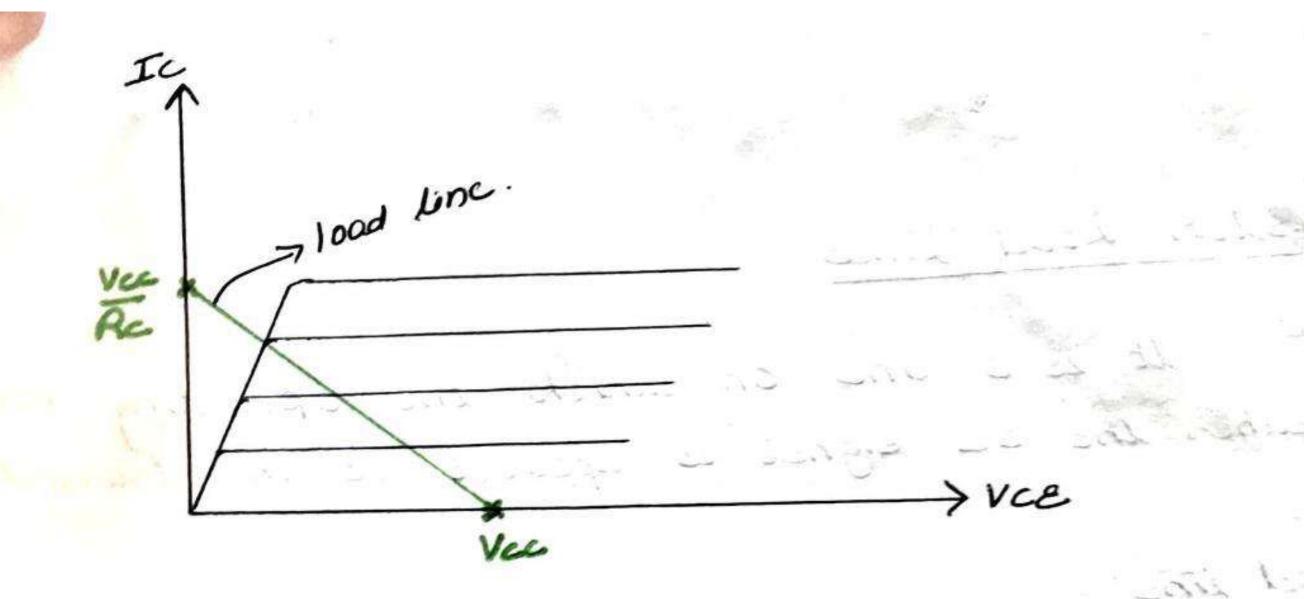

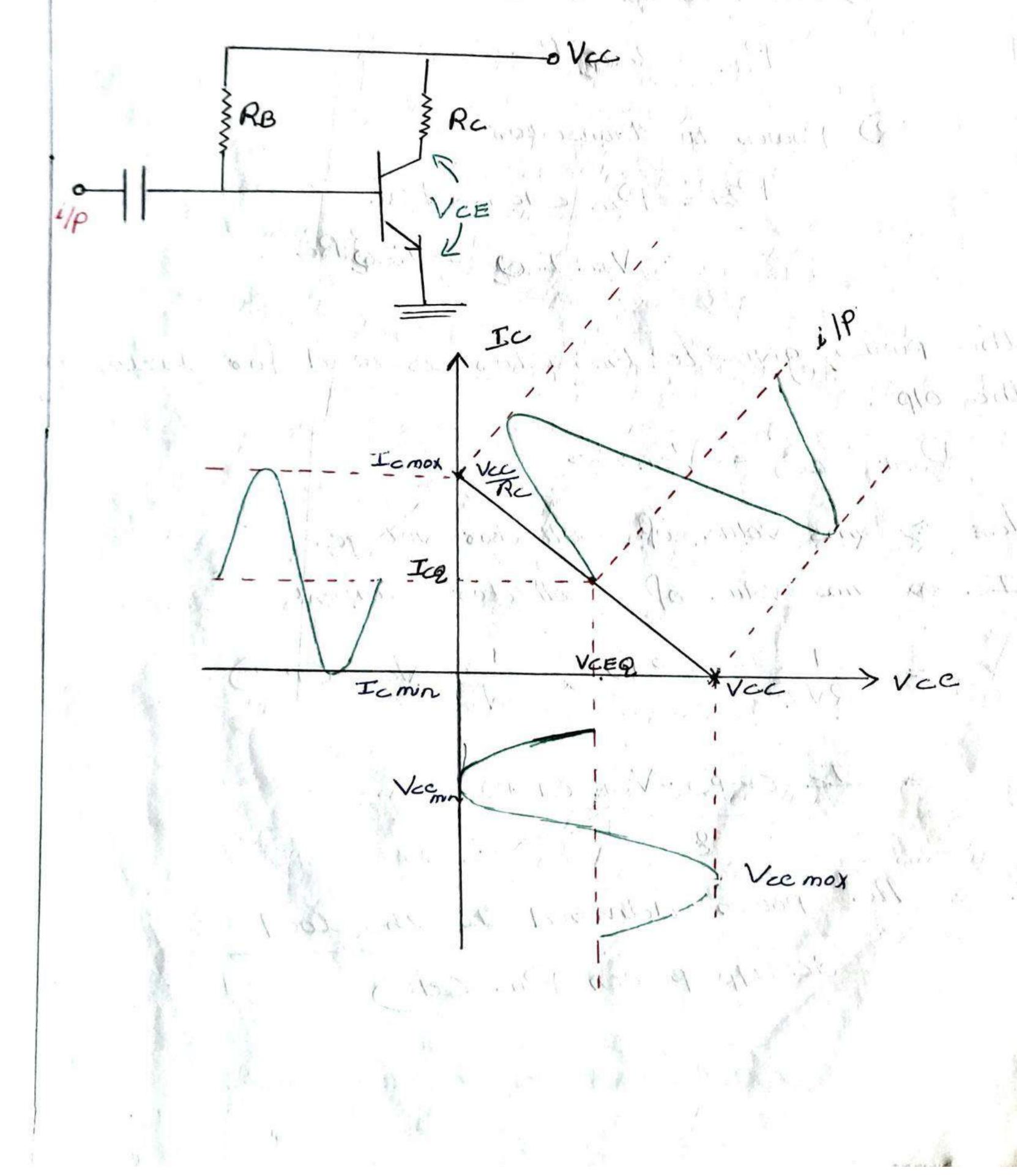

## Transiston Load Lines

It is a line on which the operating point moves euter the ac signal is applied to the transistor

DC Load line: -

It is drawn ruithout any ac ilp signal.

Vac = ICRC + VCE

Vce = Vcc - ICRC - C)

Pert Vae = 0 in courci)

Vcc z IcRc

.: Ic = Vcc/Rc

Put Iczo in esuci)

VCE = Vcc

by Joining those points, a stronget line is observed, the newling line on graph is collect load line.

ILAHIA COLLEGE OF ENGINEERING AND TECHNOLOGY

26 23 33

2567.20 166. 279.00

J. 11.39

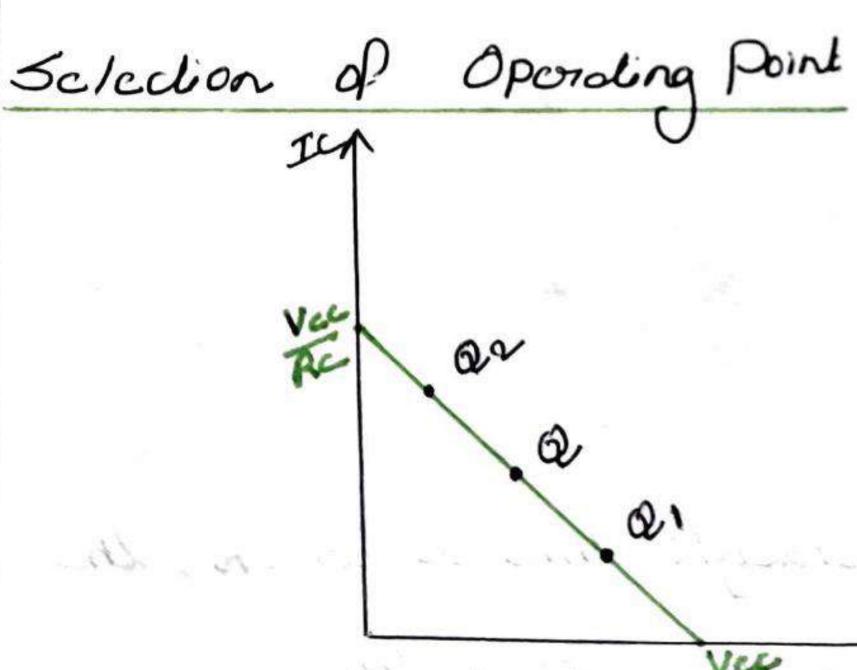

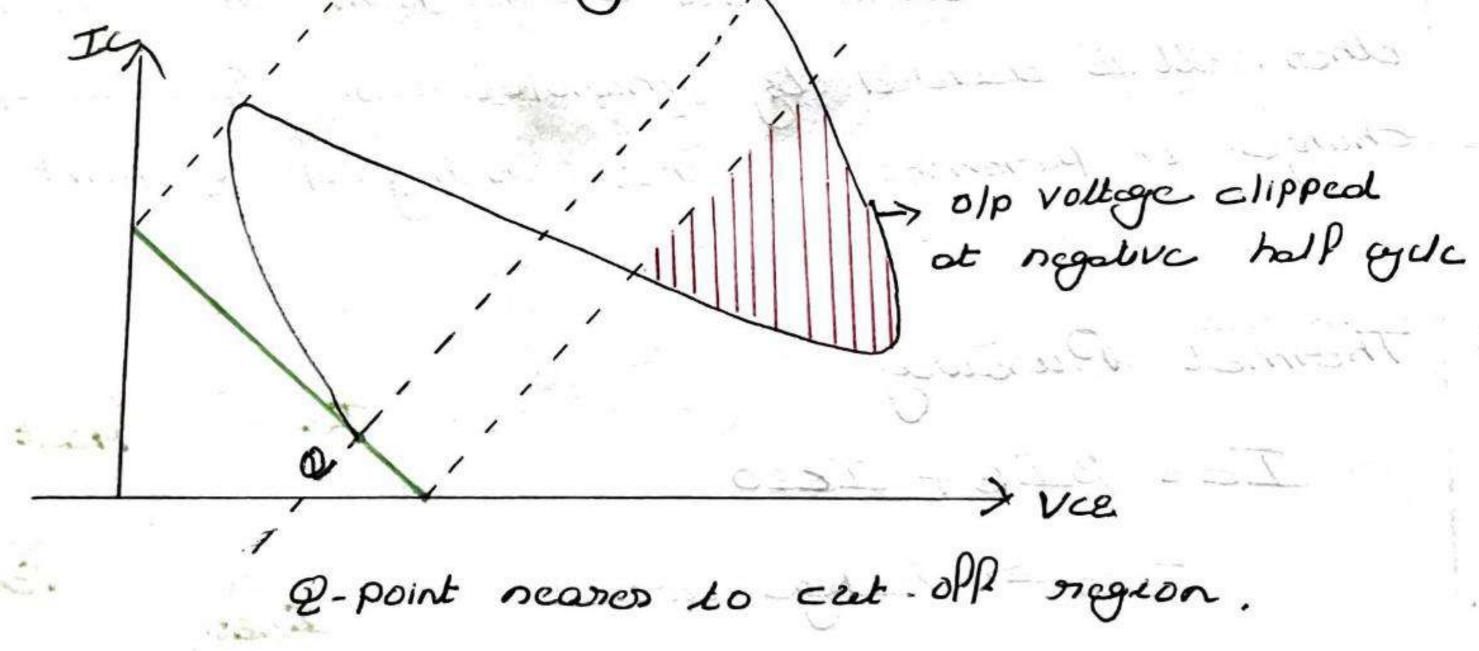

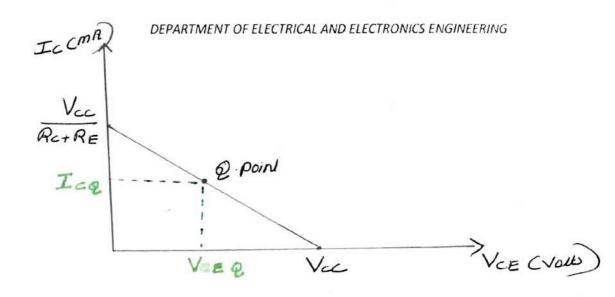

## Operating Point on Q-point

Q-point is collect quiescent point or operating point.

It specifics the collectors considert Ic & Vce that

exist ruber no ilp signal is applical.

It is also called operating point because the Variation in Vee 2 Ic takes place about this point ewhen the signal is applied. The best position for this point is the midway b/2 the cut off 2 saturation point exhere Vee = 1/2 Vec.

For the proper amplification of ilp signal, the selection of operating point is emported.

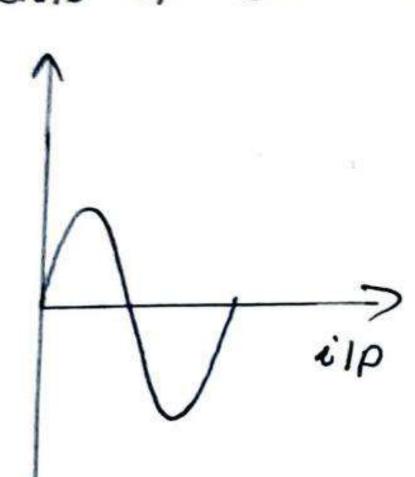

At the point Qi, it is nearer to cut-off region, the old word & vollege would be allowed to vow but it will cupped at the negative Peak of the ilp signal.

At the point Q2, it is nearer to solvention rigion, the olp agnot would be clipped at positive peak of ilp signal.

The point of located at the centre of load line seem to be the best operating point.

We have to fix operating point at a particular point.

This process is called biasing.

During amplification, operating point is shifting because, the reasons are given below.

# Meed for bios Stabilization

1) The transistor parameters are temp. dependent ilp emp, olp emp, current gain, vollage gain are the four transistor parameters. Lether temp. Varies above parameters are charged. So proper amplification does not battes place.

2) Transistor parameter B' eul charge hom onit to onil. The parameters will charge from one transistor to

other. It is decided by manufactures. Because of this change in parameters, the stilling of Q-point occurs.

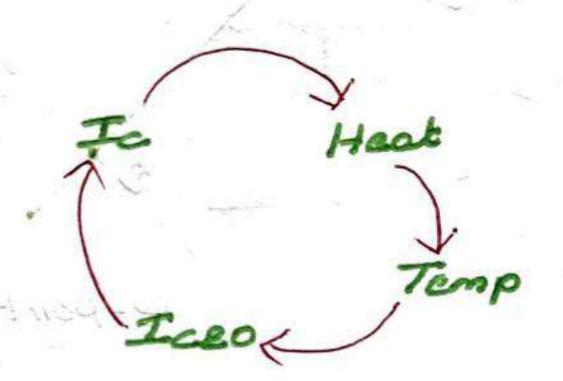

3) Thornal Rusaway. Icz BIB+ ICEO ICEO => leatage current. Iceo Temp

Consider a C.E configuration. It is a phenomenon in Ce configuration. During amplification Ic incorcors heat incorected, temp. incorected covalent bonds are booker 2 more electrons are produced, Iceo incorede ¿ again Ic incoreixe, it will repeat. This is a Comulative process. It continues until toansistor burn away. This is called thornal man away

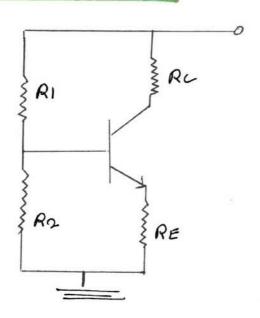

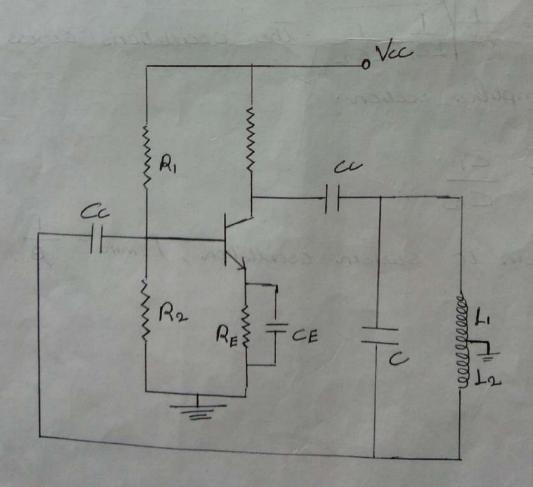

RIER2 => rused for biosing 2 stabilization CHUS

Re => Emittes bypass

Cc => coupling capacitors.

Potential divides biosing is used an class because it provides good subilization of the opening point.

Cin => ilp capactors of about 10 Ml is used to couple the signal to the base of tan. It allows only as signal to flow. In the absence of cin, the signal source resistance suit come across R2 2 this changes the bios.

CE = Emittor bypess capoutor (10011) is used to

Provide a low reluctorice path In the absorce

of this capoutor, amplified ac signeds Planing

through RE, will cause voltage drop occases it

Which inlumn will feedback the elp side &

reduce the olp Voltage.

CC => Coupling copoutor on blocking copoutors (1011).

It blocks dc. component of olp signal In

the absence of cc, the newistor Re will

come in parallel to RI of second stage,

thereby changing the bloomy condition of

next stage.

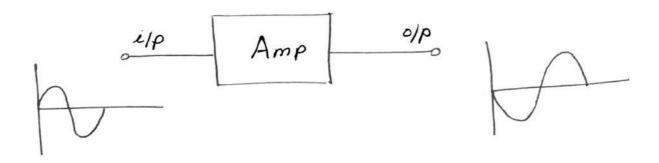

### Amplifying Action

When a signal is applied blow the base & the comitter terminals of a property blowed transistor, a small base current starts Placeting. Because of transistors action, a much larger ac current (Almes base current) Places through the Resistance the value of collectors reconstruct is high larger vallege appears across Re.

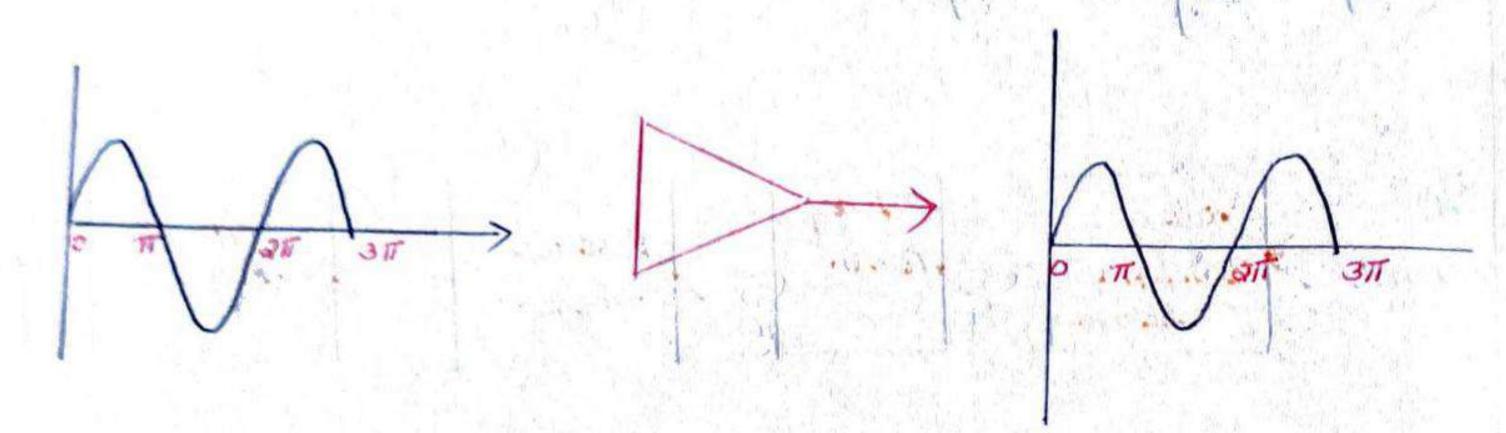

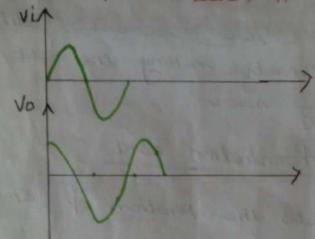

#### PHASE REVERSAL

There is 180° phase diff 6/2 elp 2 0/p

Olp VCE = VCC - icRc

Ellith incoresse in signal voltage in the positive half cycle, the bee current incoress cousing incoresse in the adjector augment, so the drop ocross RC is, icho incoresse. So the olp voltage decreases. So the signal voltage incoresses in positive direction, the olp voltage incoresses in positive direction, the olp voltage incoresses in regalive direction.

#### Load Line Analysis

The relationship 6/w the collector emitter 0/p

Voltage & the collector current Ic is linear.

Apply XVI to 0/p side of amplifier.

Vcc = IcRc + VcE + IcRE - CI)

Vcc = VcE + Ic CRC+RE

· · IE &Ic

Ic CRC+RE) = VCC - VCE

Ic = Vcc - VcE

RC+RE

Droving cret off, IC=IE=O, Substitut it in QUICI)

Vec = Vet

Draine Saturation VCEND, 526. It in con (1)

Vec = I cRc + IERE

= Ic CRC+RE)

$T_{C} = \frac{V_{CC}}{R_{C} + R_{E}}$

#### DC Equivalent Cincuit

It can be drawn by neducing all the ac. .

Sources to zero & opening all the copacitors

because the copocitors do not allow the flow of the

DC current & act as open.

#### AC Equivalent Circuit

If AC is applied, de supplies need not be considered. AC equivalent cincuit can be drawn by reducing all the de sources to zero & short circuiting all capacitors.

200

The CHT explains the behaviour ruher viewed in the ac conditions. The collectors resistance Rc comes in parallel with RL.

#### **⊥** GND

operating point is  $V_{CE}$  =5V and  $I_C$  = 1 mA;  $h_{ie}$  =1700  $\Omega$ ;  $h_{re}$  =1.3 ×10-4;  $h_{fe}$  = 38;  $h_{oe}$  = 6 × 10 <sup>-6</sup>  $\mho$ . If the a.c. load  $r_L$  seen by the transistor is 2 K $\Omega$ , find (i) the input impedance (ii) current gain (iii) voltage gain (5)

Page 2 of 4

10@ Zin = hie - hore hee

hoe + 1

51L.

1) Zin = 1400 DEPARTMENT OF 4 ESTBICAL AND ELECTRONICS ENGINEERING 6x10-6+1 11) Current gain Ai = hfe = 38 1+ hoe 91L 1+6x10-6x2000 111) Voltage gair Av = - hte 1690 (6 ×10-6+1 2000) b) Width of depletion layer controlled Effective coross section decreated with incleaning vevere bias. In it a junction of VG13. gate-to Source Voltage. \* FET Woltage Controlled device, do not need 2.5)

binsing current By applying reverse bias

Voltage to gate terminal, Channel is pinched,

so that current is switched of completely Duain organistance ord. Transconductance, gm 2.5) Amplification factor, M. Write down exporessions also.

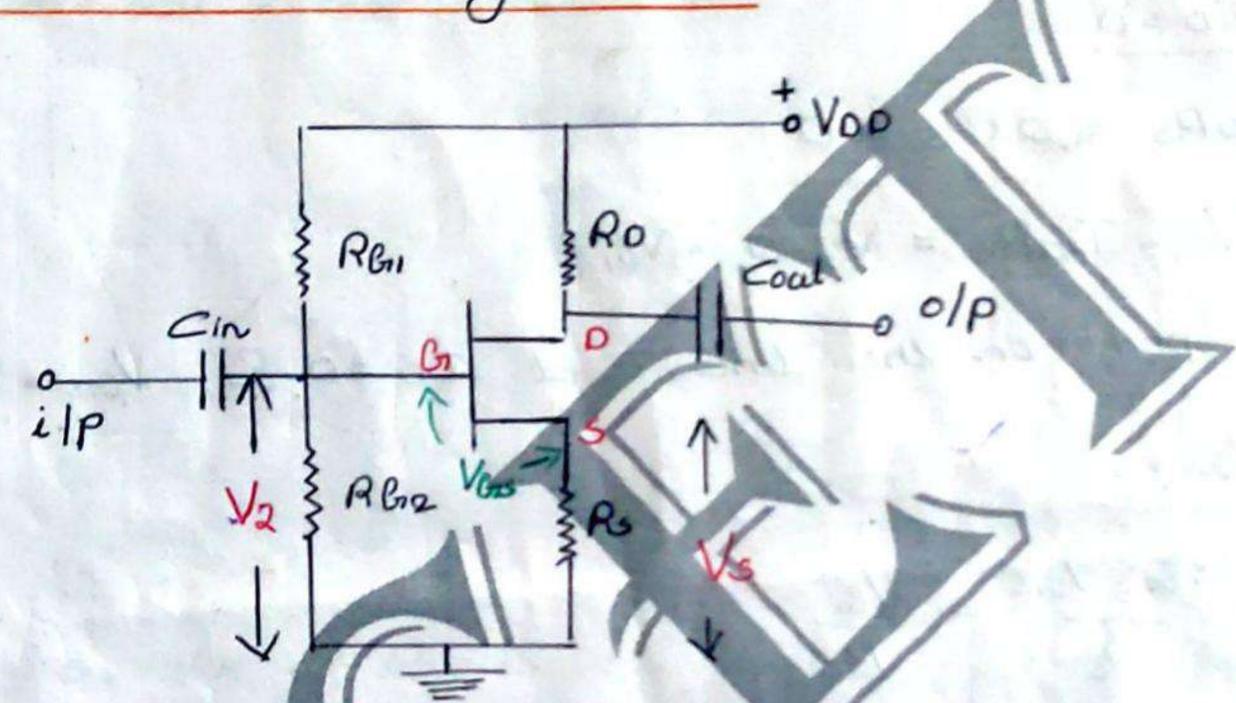

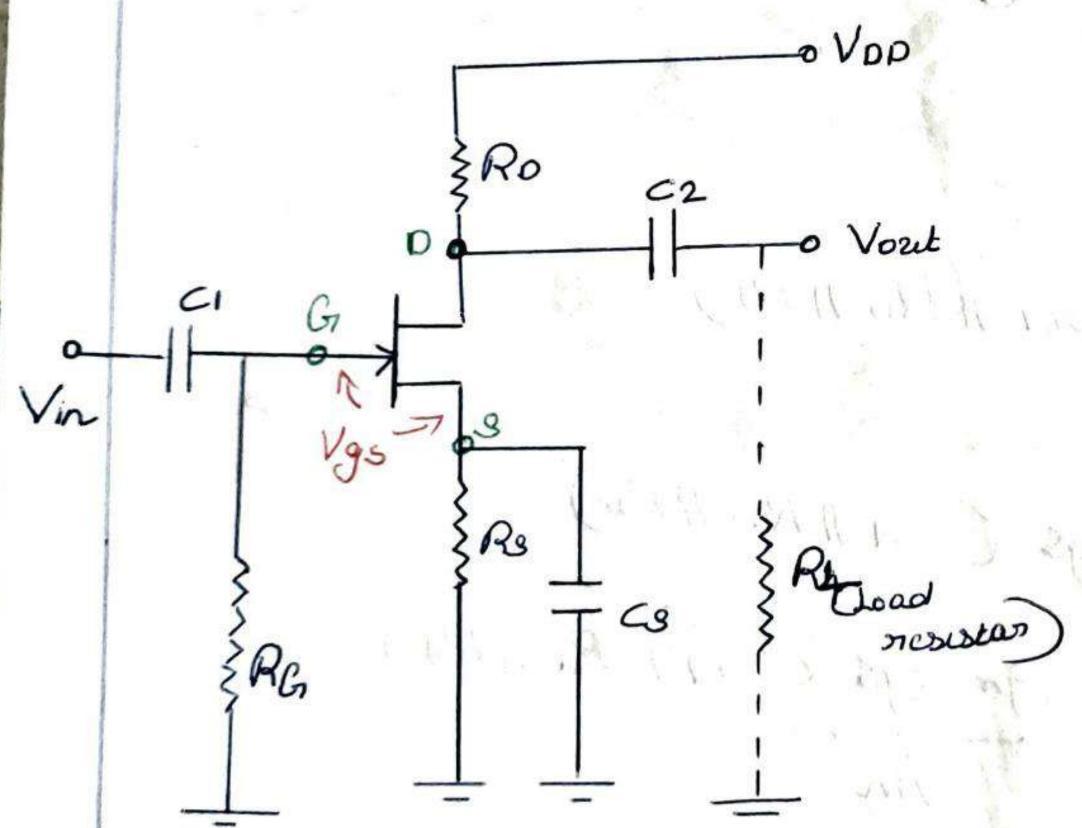

# FET Biosing

Unlike the BJT the thermal monaway docen't occur evith FET's.

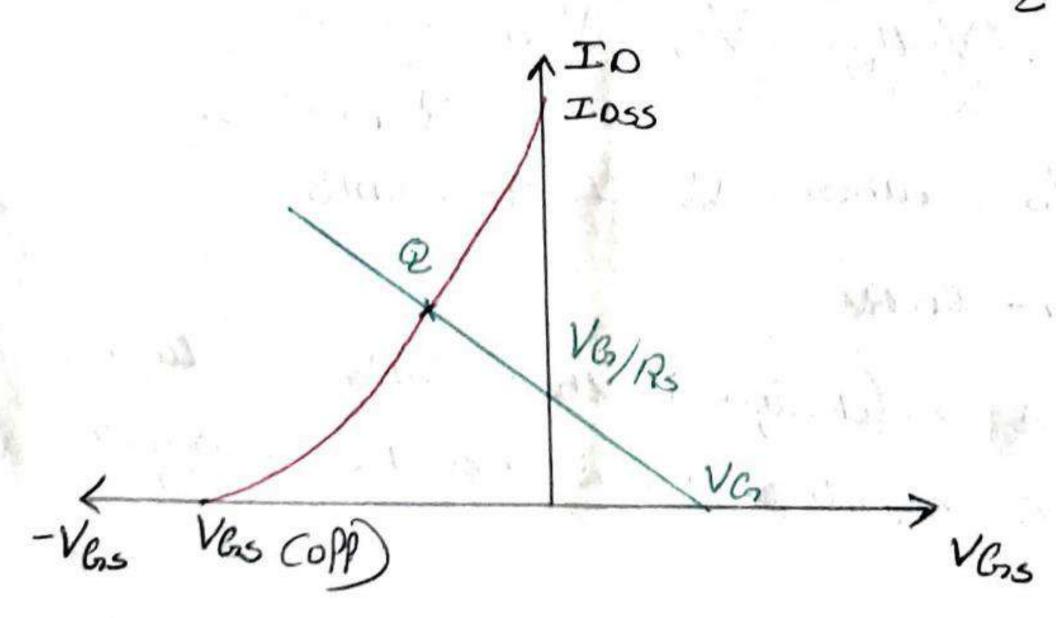

Potential Divides biosing of FET

The nexisters Ray 2 Rena poortales a potential divider across the necessary was. The vollage across Renz provides

Gote Voltge VG = VDD \* REnz

2 VGs = Ven - Vs , where Vs = Is Rs = IORS

VBns = VBn - IDRs.

The CHI is so designed that IORS is larger than Ven so the VGs is negative. This provides a negative gate Vallage.

$$V_2 = V_{GS} + I_D R_S$$

$$I_D = V_Q - V_{GS}$$

$$R_S$$

then Vos = VDD - ID (ROTRS)

The value of ID & Vos determines the operating igned In Vallage divider biosing cuter ID=0, Vers 70

. One point on the line is at ID = 0 2 Vons = Vos

The second point on the line is at  $Io = \frac{VB}{Rs}$  2  $V_{GS} = 0$ . The point of which the load line intersects the transistors characteristic cause is Q point.

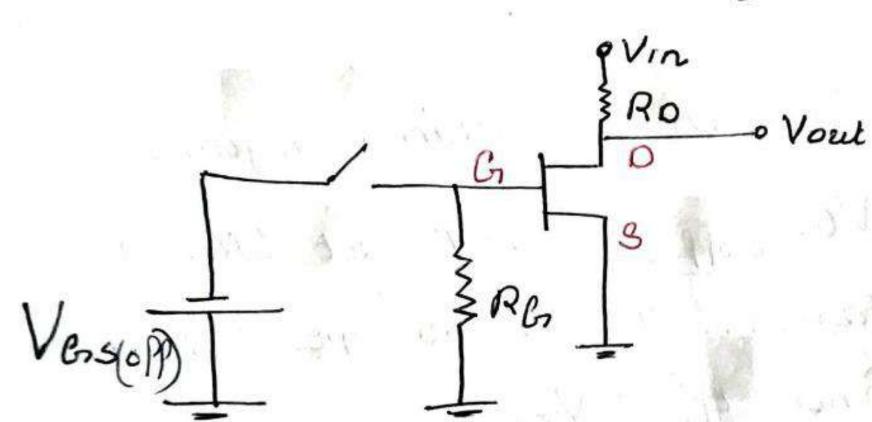

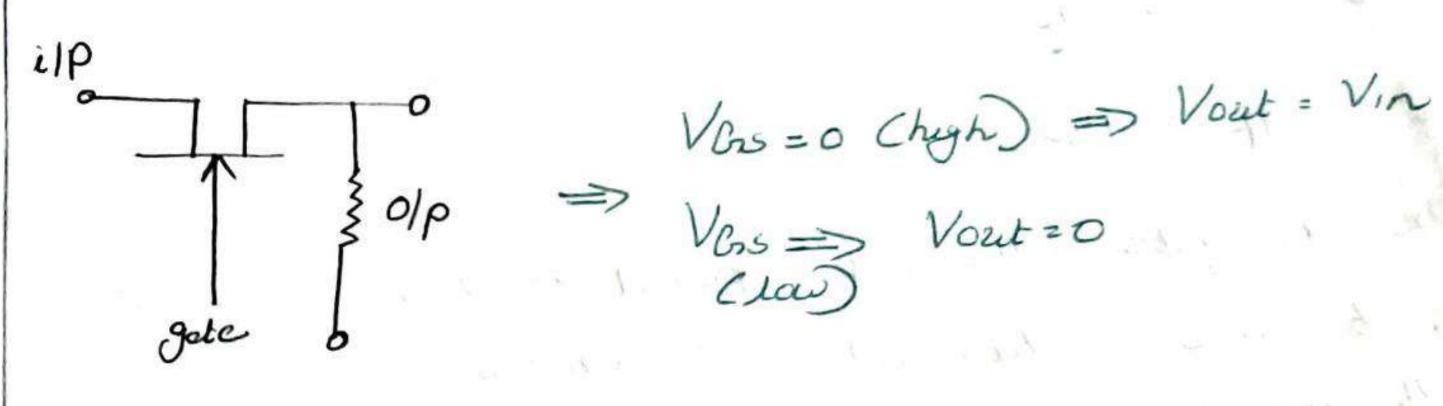

## ET as a secutch

Vin = ilp Vallage

Euther no gate vallage is applied to FET. VGs=0, FET becomes saturated 2 it behaves like a small resistance.

then Olp = Vout = Vin x Ros

ROSCOD + RO

i the value of RD is very large, the old Vout = 0

Either a negative Voltage Vers coff is applied, the FET operates in the cent off region, it act as Very high resistance - hence the old nearly equal to its

Ros cold >> Ro, so Vout = Vin

Vons

Shurt Szudd

Series Szeutch

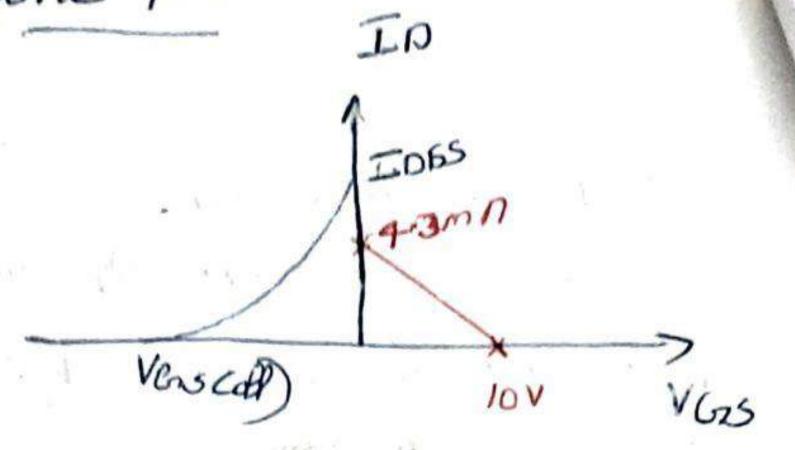

# FET as Voltage controlled Rossstance

21hor JFET operates in the Ohmic region with Vos 6/2 0 & Vos coff, JFET act like a Voltage controlled resistance. It can be operated in the region prior to pinch off (Vp).

In this region drain to

source orcsistance can be

controlled by VBS.

$$y_{ds} = \frac{V_{D8}}{T_D}$$

Nos

nas depends on the value of Vas.

Vors=0, ords is minimum

Vers = more regetive, ords increases

Elhar Vos becomes regative, ID on the drain avant

## DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

$$91dS = \frac{100 \, \text{mV}}{0.4 \, \text{mB}} = 250 \, \Omega$$

when  $V_{GS} = -2V$ .

So JFET act as the VCR in ohmic region

A JFET amplifier 2 with shotlized biosing cut is shown. Vp = -2V, I ass = 5 mA,  $R_{\perp} = 910 \, \Omega$ ,  $R_{\rm B} = 2.29 \, k\Omega$ ,  $R_{\rm G} = 12 \, m\Omega$ .  $R_{\rm M_2} = 8$  57 mr 2 V DD = 24 V. Find the volue of drain

$$\int_{0}^{\infty} V_{GI} = V_{GS} + I_{O}$$

$$T_{D} = T_{DSS} \left[ 1 - \frac{V_{CS}}{V_{P}} \right]^{2} = 5 \times 10^{3} \left[ 1 - \left( \frac{V_{CS} - I_{DRS}}{-2} \right) \right]$$

$$T_{0}^{2} = 5 \times 10^{3} \left[ 1 + \left( 10 - F_{0} \times 2.29 \times 10^{3} \right) - G \right]$$

ILAHIA COLLEGE OF ENGINEERING AND TECHNOLOGY

the till with the terms of the plant of the first

M. All in.

2. The gm of FET. Valtage amplifier cht is

2500 microssemers & load resistance is 12 H.J.

Determine valtage gain of amplifier che.

Bessume na & RD>>> RL.

$$gm = 2500 \times 10^{-6} \text{s}$$

912 RD SORL

$$P_{Vz-gm}R_{L} = -2500 \times 10^{6} \times 12 \times 10^{3}$$

= -30

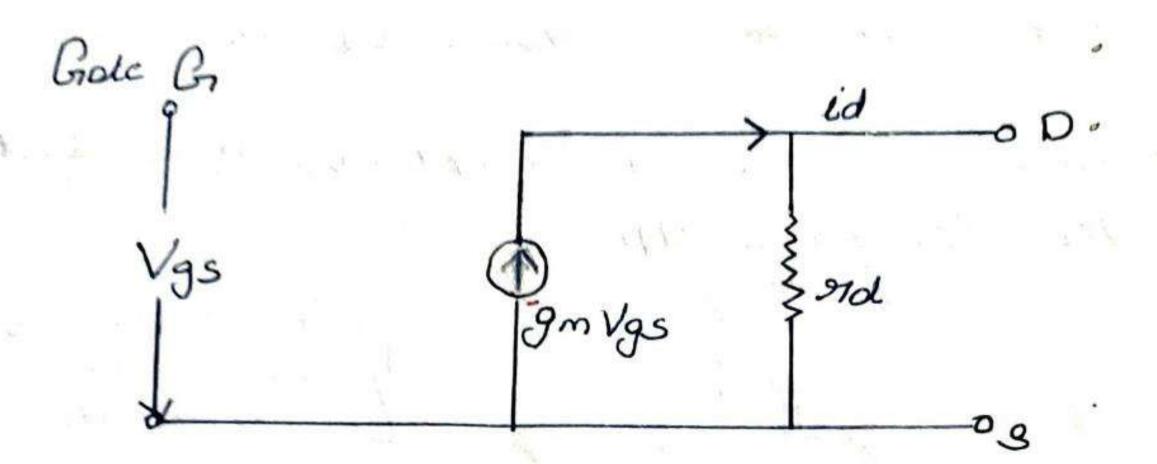

# FET small signal model (Low Pricquescy)

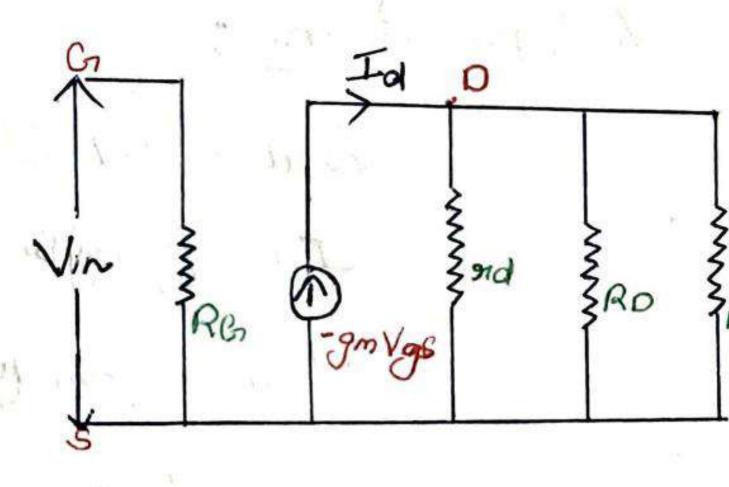

Common Source JFET amplifics

AC ESUVOLON CHI

VD = VDD - IDRD

=> Deving +ve half upde of ilp, Vgs increases

.: ID also increeases. Hence VD decreases

=> Deving - Ve half eyeld of ilp, Vgs decordeds. ... ID also decordeds. Hence VD incordeds.

In common. Source JFET amplifies, there exist a phase shift of 180° blew ilp 2 olp

Por drawing accepuisated

Cht

Dend all De source

2) se the copoulonce

3) Ren, nd, RD, RL are

Olp. grounded y.

Voltage Grain:

Vout = Id (910 11 RD 11 RL)

Id = -9m 198

Voul = - 9m ygs (nd 11 RD 11 RL)

Pev= Voset = -gm /gs Cod 11 Roll Rt)

Vin Vin

Per= -gm (nd 11 Roll RL)

Usually nd >> ROERL

Rv2-gm (RD11RL)

Vgs ~ Vin

works at the

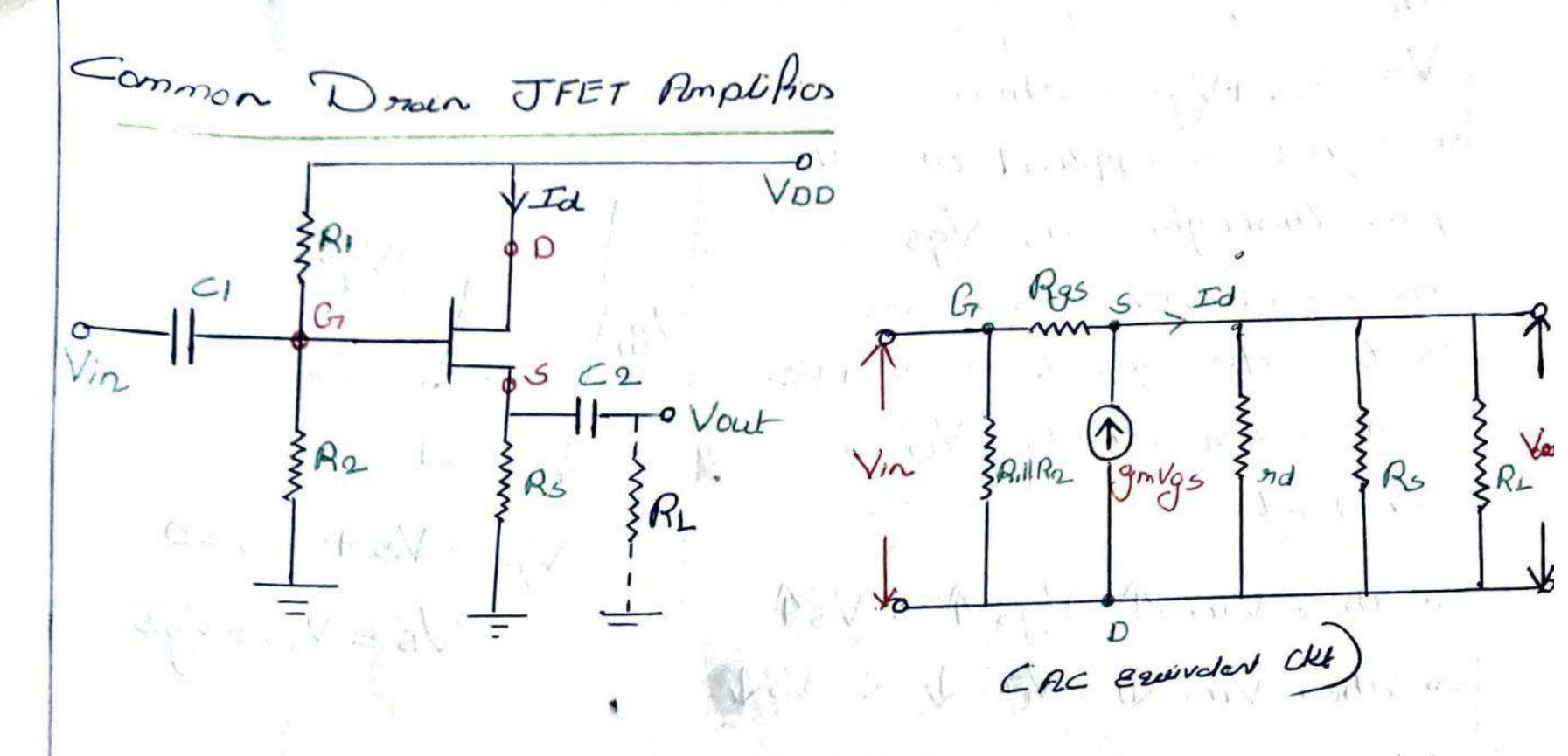

CI, C2 => Coupling capocitors

RI, R2 => biosing resistors ( potential divides)

No bipers capocitors are used.

Vs => O/P Voltage

- => During +ve half cycle of ilp, Us is high

- => Drung -ve half ande of ilp. Vs is low.

- Because the olp voltage at FET source terminal

follows variotions in signal voltage applied to gate

the common drain that is also called

Source follower

Caradelan and the first

ILAHIA COLLEGE OF ENGINEERING AND TECHNOLOGY

De a Viligha , acres

Explanation

S3, EEE, Module-II, Ohange Ansloypa

the source Vallage Vs = VB+Vgs · Euchon

a signal is appliced to FET gote thoough Ci, Vgs

uncorcoses on decreoses

as the ilp signal goes +ve

2 - VC respectively. Vis is

constant.

=> Euther Vin 1 Vgs 1 & Vs1

=> Euser Vin J Vgs J & VsJ

Vgs-Vs+VG=0 Vs = VB+Vgs

Vs is the orthpret vollage.

fullous the ilp, .: it is colled The old Vollege Vs Source Pollower. Vocat = '11.

Rv = Valtage gain = Vin

Vout = Id (na 11 Rs 11 RL) = gm Vgs (na 11 Rs/11 RL)

Vin = Vgs + Vout = Vgs + gm Vgs Crall Rs 11 Rs). = Vgs C1+gm Cnd11Rs11Rs)

gm (mill RSIIR) Per = Vout = gm Vgs (na IIRs II RI) 1+gm (mall Rs 11Rs) Vgs (1+gm Cnall RslIRL))

usually and >>> RSIIRI

gm (Rs 11 RL) 1+,9m (Rs 11 RL)

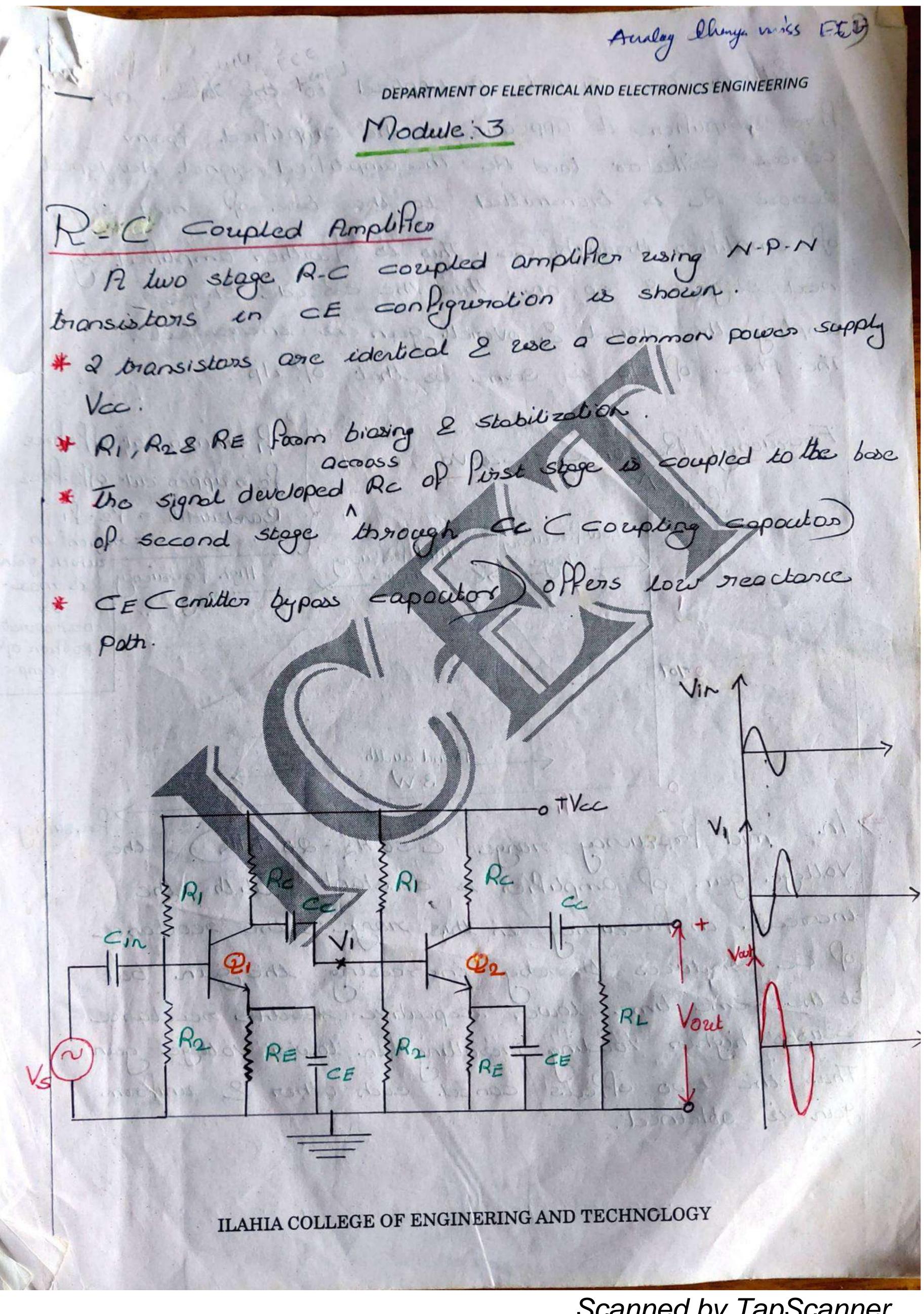

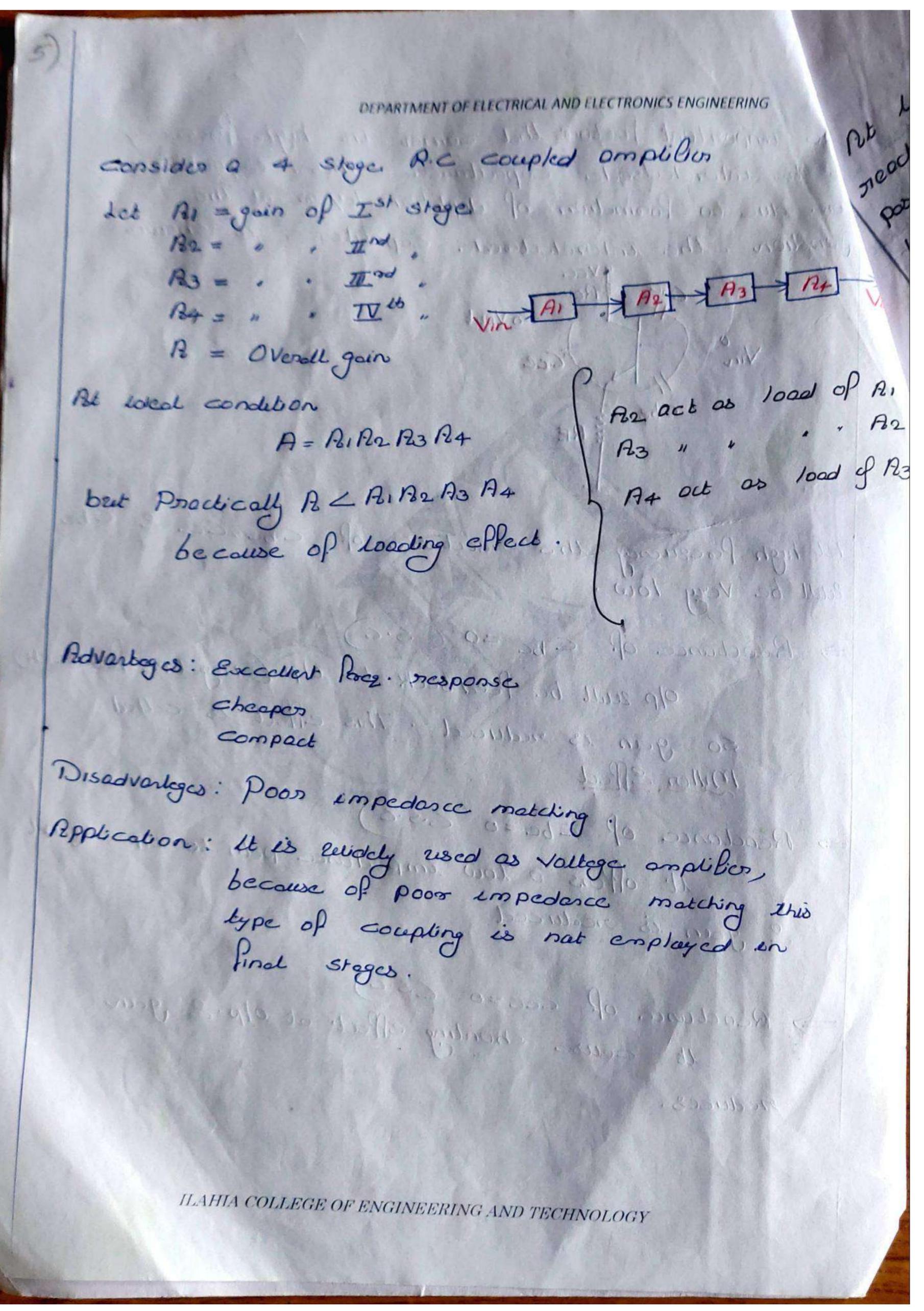

Eutron ac signal is applied to the boxe Parst ampufier, it appears in the amplified form, across collector load Rc. The amplified signal devi, no across Re is bransmitted to the bose of next six of amplifier through a. This is further amplified by next stage 2 so on. Thus the cookede stages amplify the signal & overall gain is increased. The Phase of olp is some as that of ilp. Pi => lower cut off face Pa => ruppes out off Prace Frequency Response Curve Bardewalls = P2-P1 High Poerucia \_ Band width In mid Processey marge (50 Hz - 20 HHz) - the Voltage gain of amplifies is donstant. Ealth, the increese in focquercy in this marge the meachance of Cc neduces thereby increasing the gain best at the same time lower capacitive reactive reactance couses higher loading nosalting en lower vollege gain There the two effects cancel each other & uniform goin is obtained.

Michael Committee of the Committee of th

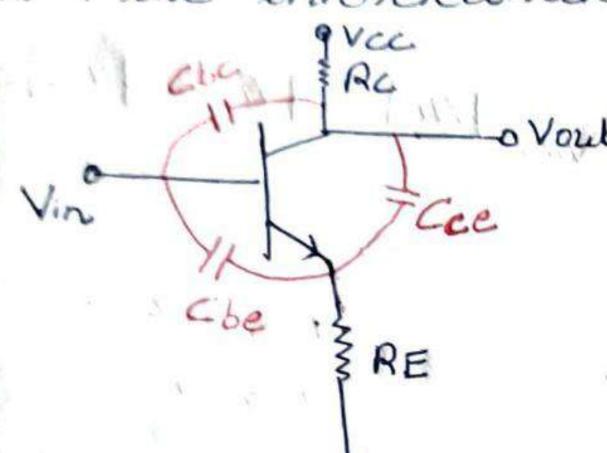

the important foctor that comes in high foreguescy is the interdectioned copacitances. These capocitances are due to formation of depletion layers at the junction. The interdectorade capocitance is shown,

But high Paresuesay this preoctance of Gbc, Gcc 2 Gbe will be very 10w.

=> Reactance of Cbc =0 (5.2)

Olp enul be feed bock to ilp (negative feed beck)

so gain is reduced. This effect is colled

miller Effect

=> Readonce of Cbe=0 (5.0)

It offers a low impedance path to ilp signal.

2 gain is reduced

=> Reactance of cee=0 Cs.c)

It course shorting effect at olp. 2 gain

neduces.

Petively shunted. Thus Voltage gain Palls of at Low Passuencies

the amplifier decreences with the encourage in Processery.

Several Pactors are responsible for this reduction in gain. At high Processers, the reactance of Ca becomes very small & a behaves as short-circuit.

This encocase the roading of next stage & reduces the Vallage gain. At high Processers, capacitive reactance of base emitter junction is low & so the base current is encocased & current goes factor B is reduced. At high Processed & current goes factor B is reduced. At high Processers, the interelectnode capacitance Coa cornects the Olp and to ilp att. Thus regalive P.b takes place & gain is reduced.

enabon. The event signal is applied to the boxe of the transistors. Due to transistors action, an amplified output is obtained across the collectors load Rai of the Purity transistors. The amplified signal developed across Rai supplied to the boxe of next transistors. This is further amplified by next stage 2 so on.

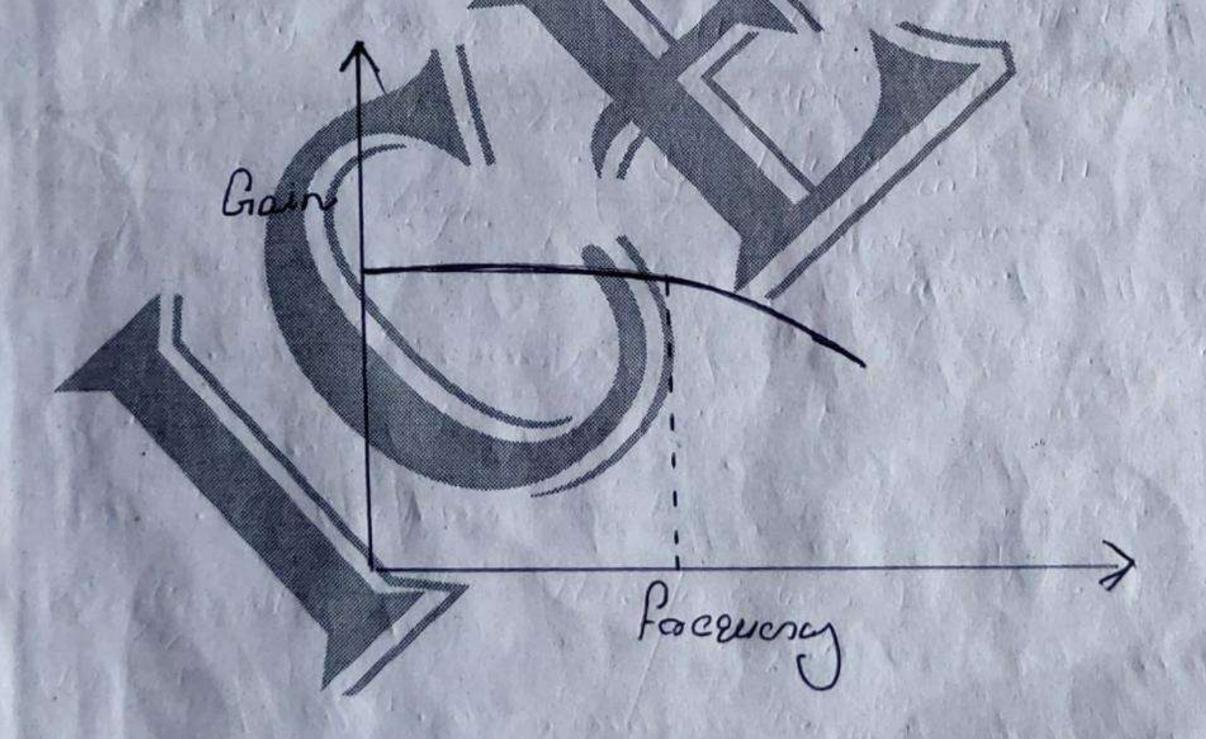

Freewerry Response.

It has no coupling 2 bypose capacitors to cause a drop at low forevery. The Possessery response curve is flat upto upper cut-off forevery f2. Above this gain decreases due to inter-electrode capacitance of device

Scanned by TapScanner

Scanned by TapScanner

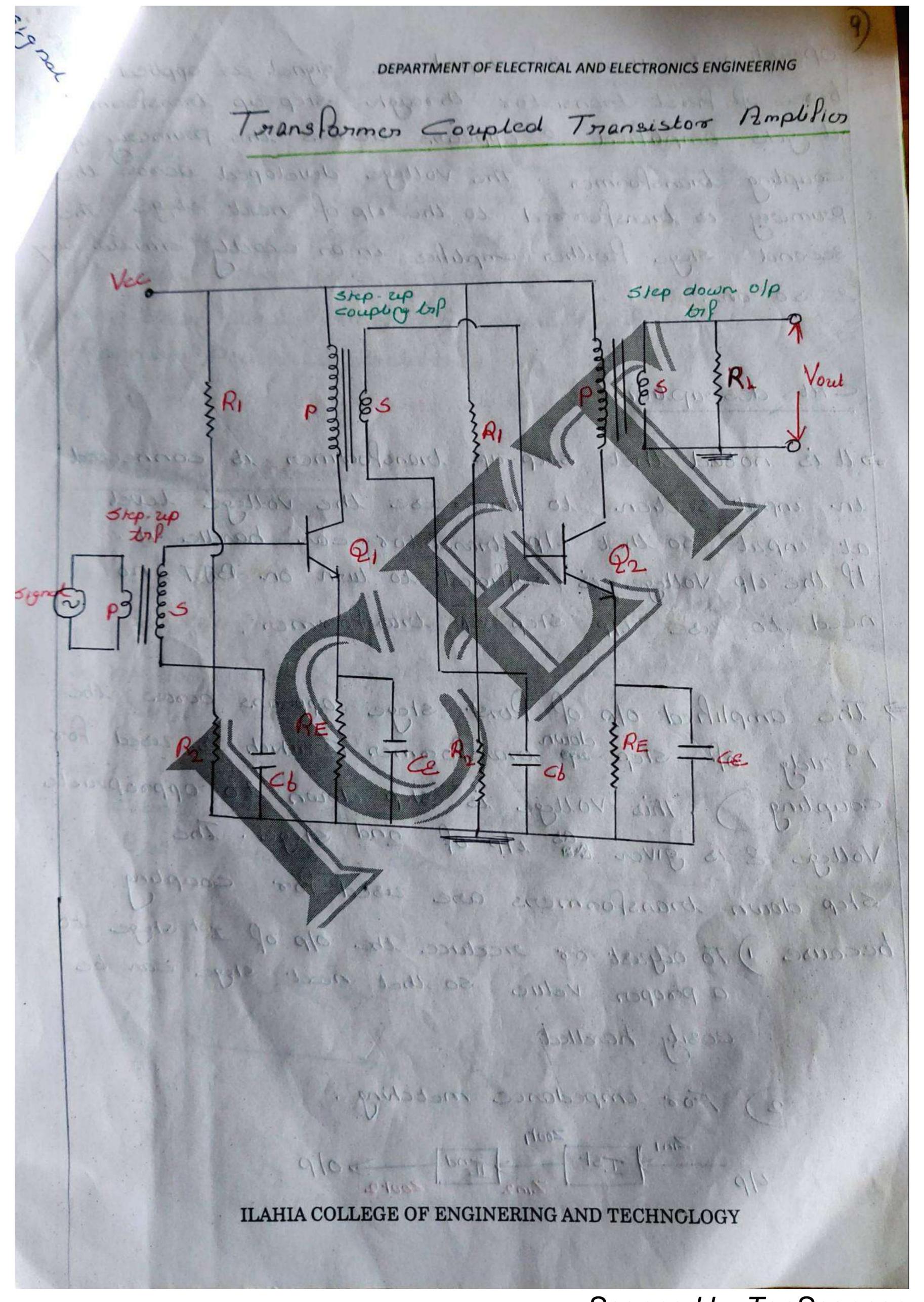

operation: Either the input ac signal is applical base of Anst bransistors through step up transform, it gets amplified & appears across the primary of coupling transformer. The voltage developed across in the primary is transformed to the ilp of next stage. The primary is transferred to the ilp of next similar way second stage Purther amplifies in an exactly similar way

#### Crit descuption

in input section, to increase the voltage level at input, so that ilp mansistors can hardle it.

If the ilp voltage is sufficient to turn on BIT, no need to ruse ilp step up bransformer.

The amplified of post stage appears ocross the 1° widy of step down transformer (entire is used for coupling). This voltage is step down to appropriate Voltage & is given has if p of and stage. The step down transformers are used for coupling because ) To adjust or reduce the of Ist stage for a proper value so that next stage can be casily hardled

2) For impedance metching.

Zini Zouti

Zini Ist Ind Zout 2 0/P

Zin 2 Zout 2

Impedance matching means, suher suc catedos

different stages toe 10/p emp. of a stage should

match enits ilp imp of next stage.

We can achieve this empedance matching by

step down transformers by adjusting its turn's ratio.

Maximum power is transfered if Zout, = Zinn

Maximum power transfer theoremy

### Forceway Response.

The Presuescy response of Lift-coupled amplifier is very poor.

The old Vollage = Ic x Xi way.

- gain is reduced.

- But at resonance condition the gain will be maximinan

90in M

Advantages : D low ok nesistance at collector 2) best impedance matching. 3) coupling is affective Disadvantages: 1) Poor Pacquescy mesponse. 2) Bruky 2 . cosky. (11) Repulsions: It is not used for amplifying low Processer ( 20 KH2 ( ) amplification. The second of the second The second second second Maybe Pourse III. with long on him or produce in 1. 11.11 11. 11. 11. the first terms of the second of the second

#### DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

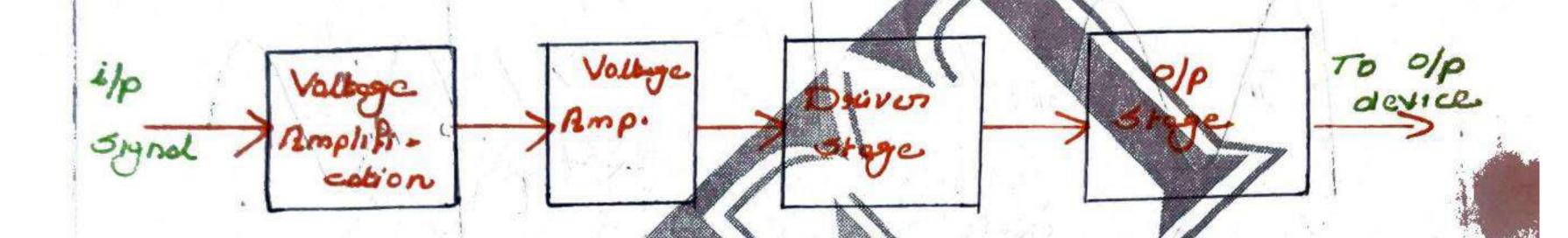

#### Power Remplifier Stages

Power amplifier is meant to amplify a weak signal until sufficient power is available to operate an output device such as a loudspeaker, a solenoid on a relay. Power amplifier, to provide the desired power amplification has generally 3 stages

1. Vallege Pemplification Stage

For raising the level of lycak ilp signal, it is amplified in two or more stages, R-C coupling is usually employed.

2) Douver Stoge

The stage that proceedes the olp stage is called the driver stage. The driver stage renders power amplification.

3) Output Stoge

The old stage assentially consists of a power amplifier & is meant for bransferoung maximum power to old device.

March & School Company (C)

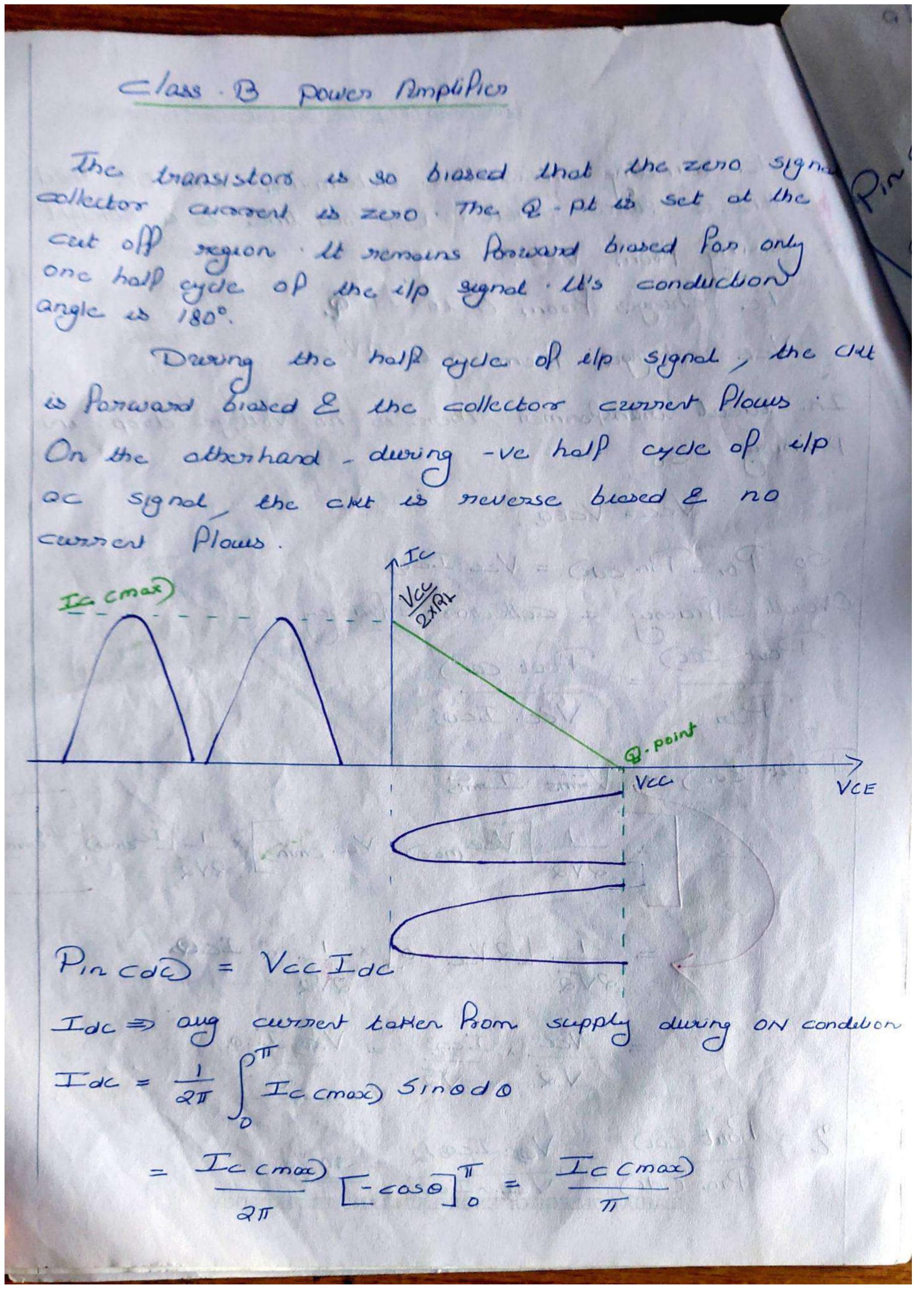

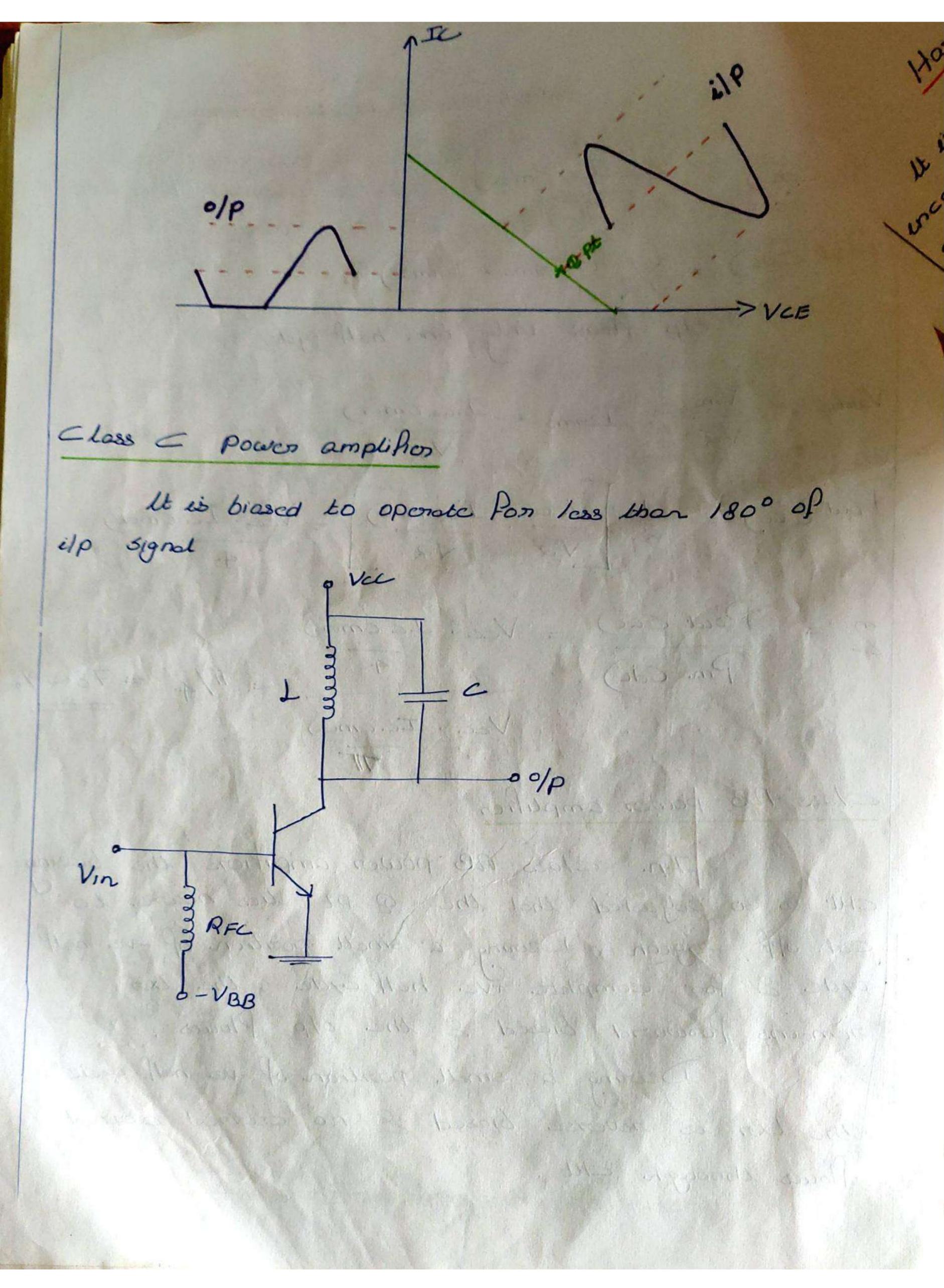

A closs A power amplifier is defined as a power amplifier is defined for the full-your countries, the (360°) of the elp signal. In other evones, the transistors remains forward biased throughout the ilp cycle.

- => 0/p conner Places for entire 360° of ilp Eyelc

- => bransiston renains fooward biased throough out

- => The Q-pt is located at middle of load line

- => 0/p contains less distantion.

Two spes of class A power amplifier.

1) Series Ped class A power amplifies

The state of the s

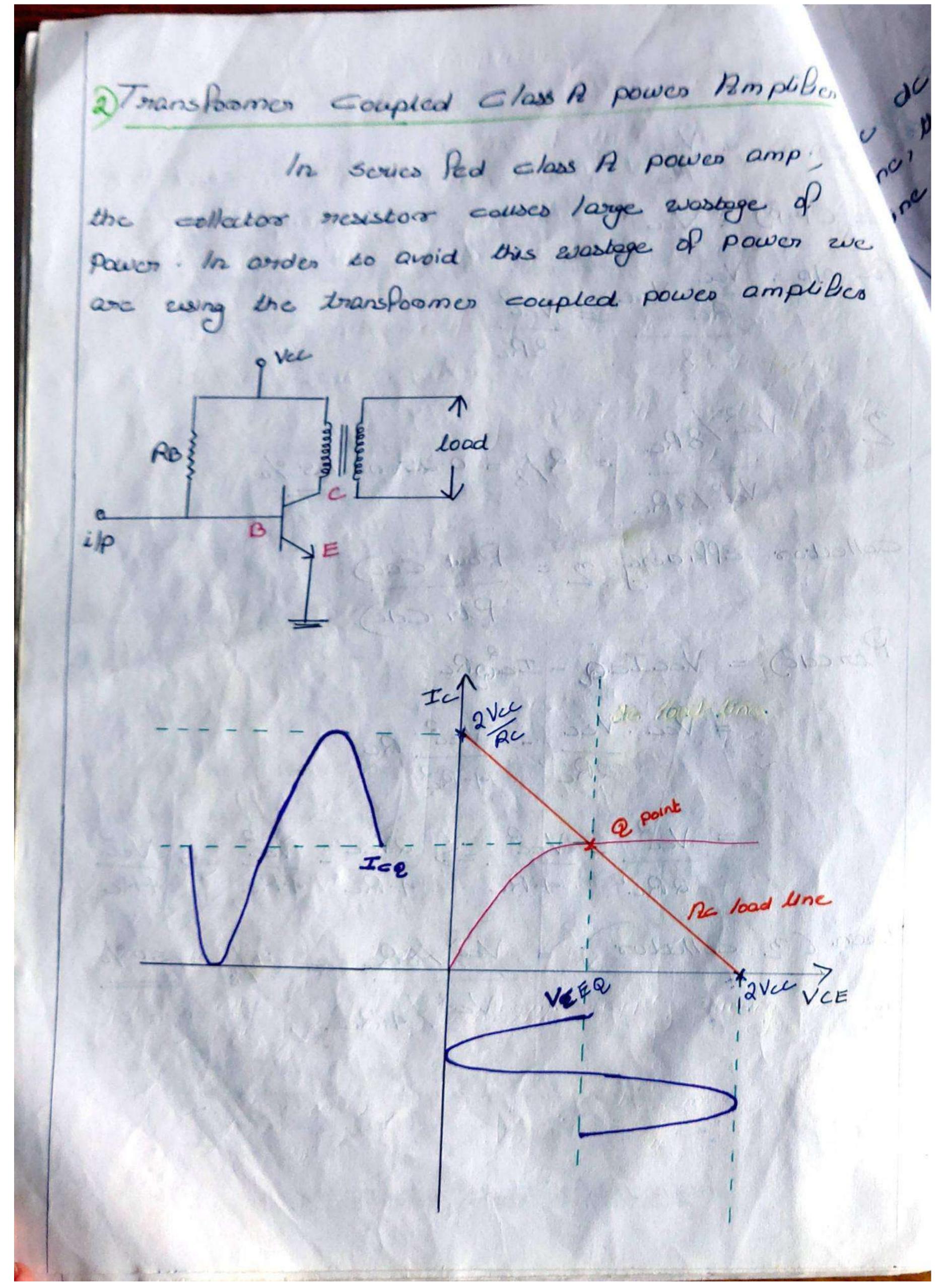

2) Transformer coupled class A power amplifier

The state of the s

The load resistance Re is connected in Series eith the bransistors of The elp signal eised is in the range of valls & the transistors and is power transistors.

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING enpeut power from the supply. Pin cdo) = Vac Ica. this power is used in the Pollowing components D Power dissipated across collector PRC = Ice RC 2) Power to transistor Por = Pin Cde) - Pac = Vac Ico - Ico Rc The power giver to bransistor is used for developing Post cao = VCE Ic VCE => 91ms volue of collector voltage Ic => rms volve of collector current = TCCP-D x TV CFCP-D = IC (P-P) · VCE (P-P) Ac power delivered to the load de ilp power Pin Cdo) ILAHIA COLLEGE OF ENGINEERING AND TECHNOLOGY

Scanned by TapScanner

conto freel + speciel - of some DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING he de aunding masistance determines the De load line, this is suite small. De load line is a straight line susing Room Vec. Ic changes from 0 to 2 Ica Ver charges from 0 to 2 Vcc. In edeal transformer, there is no voltage drop in VCC = VCEQ. 50 Por = Pin coo = Veg. Troo Overall Efficiency = Collection afficience ILAHIA COLLEGE OF ENGINERING AND TECHNOLOGY

Min coo = Vec Iccmas) Pout cao) = 1/2 (Vinns x Inms) of Places only one half goe Voms = Vm ; Irms = Ic cmex) Pow cas = 1 Vcc Icomas) = Vcc Icomas) = Vcc Icomas) 2 = Pout Cac) = Vcc. Ic cma) Pin Cdi) = T/4 = 78.5% Vec Ic cmed

Class AB power amplifier

The class AB power amplifiers the biasing CHT is so adjusted that the Q. Pt lies nearer to critical off megeon. Driving a small portion of -ve half cycle & for complete the half cycle, the text memains forward blased & the olp flows.

During a small portion of -ve half cycle the text is neverse blased & no current current flows through CHL.

HAHLA COLLEGE OF ENGINEERING AND TECHNOLOGY

Scanned by TapScanner

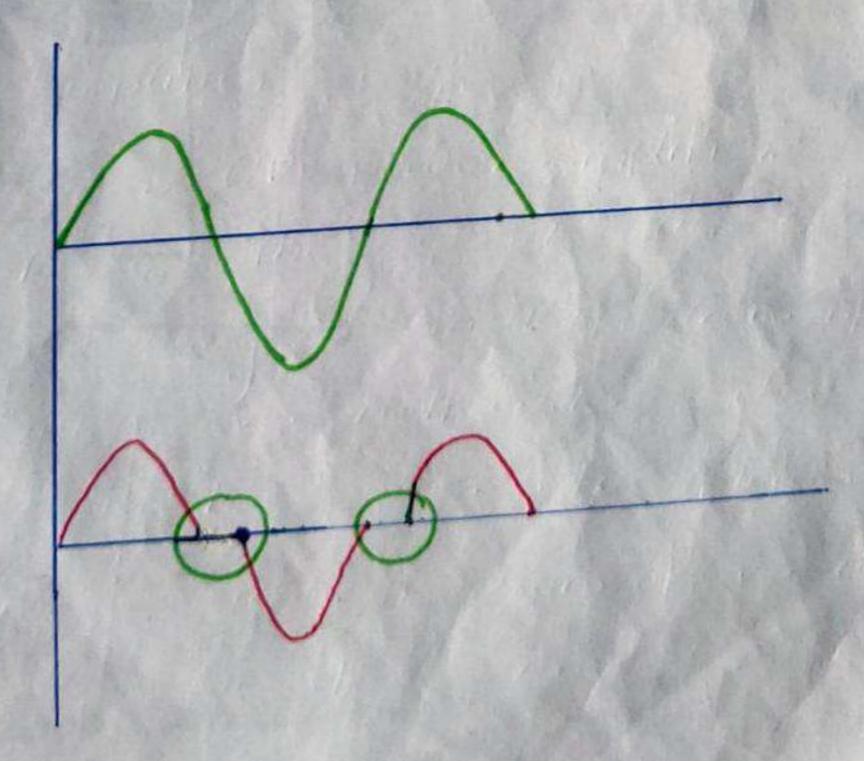

### Hammonic Distortion

the same to the non linearity of txn. It encoreases as we go from class R to class C. When non linear distortion is present, the dip above form contains components of foreversites which are harmonics of ilp signal foreversey.

## Caass Over distortion

In solicon Exa, at least 0.60 is nequired for conduction. In prush pull amplifiers, the forward bies is produced by the ilp & both of the texa will be in off condition, ruber the i/p is less than the in off condition, ruber the i/p is less than the off. This introduces the crossover distortion in the olp.

#### Feed Back Amplifiers

The Voltage gain, i/p impedance of impedance, B.W etc are some of the important characteristic of an amplifier. These parameters can be controlled by using the f.b technique

Process of combining a fraction of o/p

back to the ilp is called the feedback; ruber the

fib voltage is applied in phase ruit the ilp signal, it

is called positive or regenerative fib. When the fib

signal is applied in phase opposite to the ilp signal

is called negative or degenerative fib.

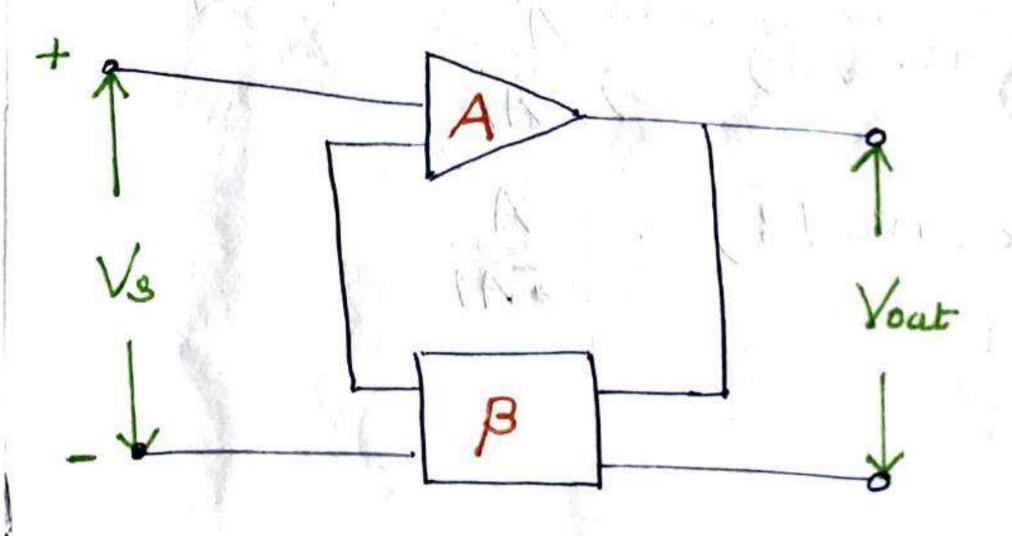

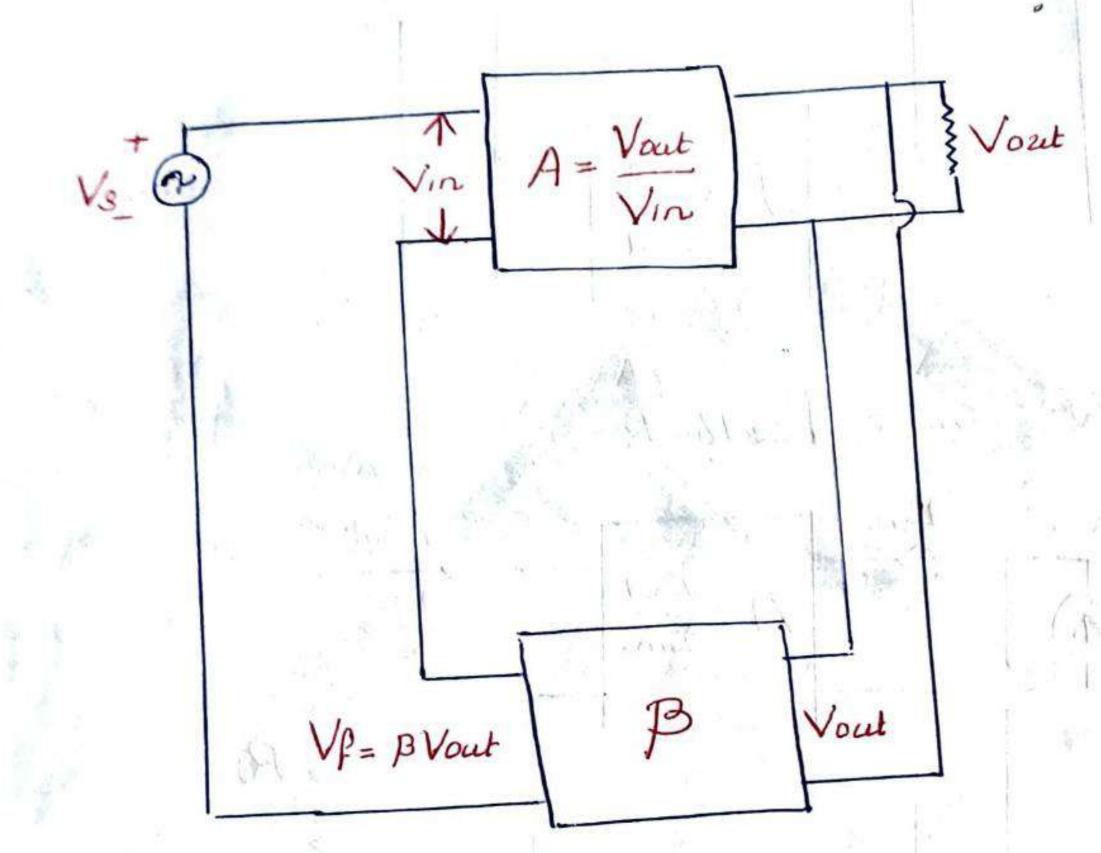

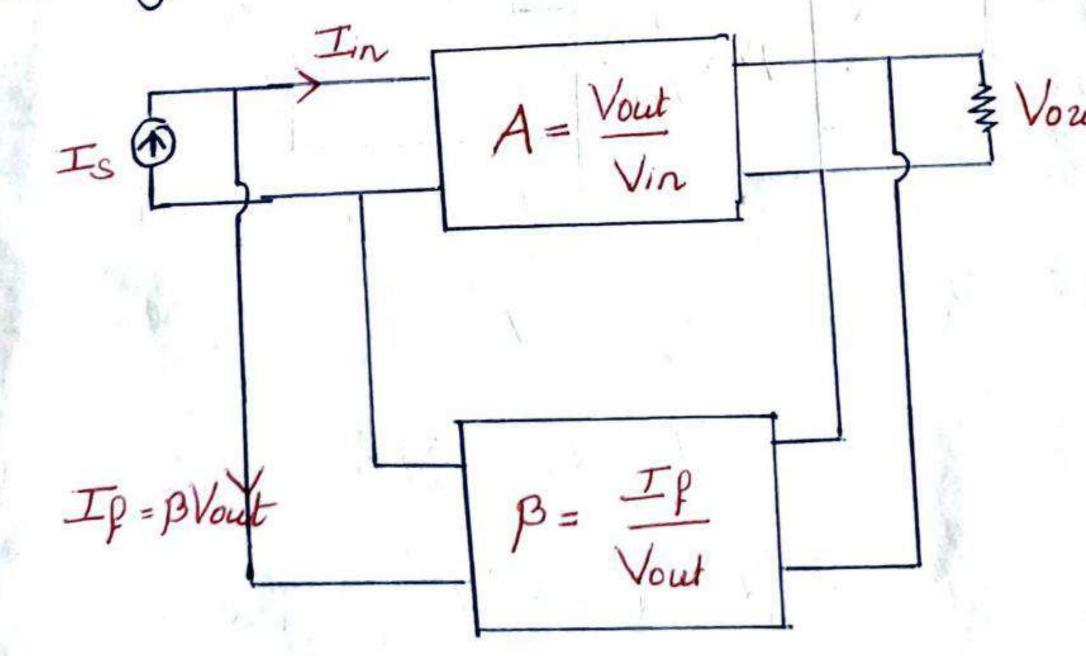

A => gan of open. Loop o

B => feedback natio

Vp => feedback Voltage

Vs => i/p signal

AB => feedback Portor

For positive f.b; Vin = Vs+Vp negative f.b., Vin = Vs-Vf

Grain of openloop amplifier A = Voul

Vin

the f.b Poutor B = VP Vout then Vp = BVout For negative Reedback, Vin = Vs-Vf Vin = Vs-B Vout = A [V8-BVout] Vozet [1+ AB] = AV8 the overall valtage gain = From the above equation Vout Overall voltage gain (-ve f.b) = Overall voltage gain (+ve PB) = A a paid a root to be self

Scanned by TapScanner

a compain and be

# Types of Pacedback Connection

a) Voltage sovies Recorback

b) Voltage short feed bock.

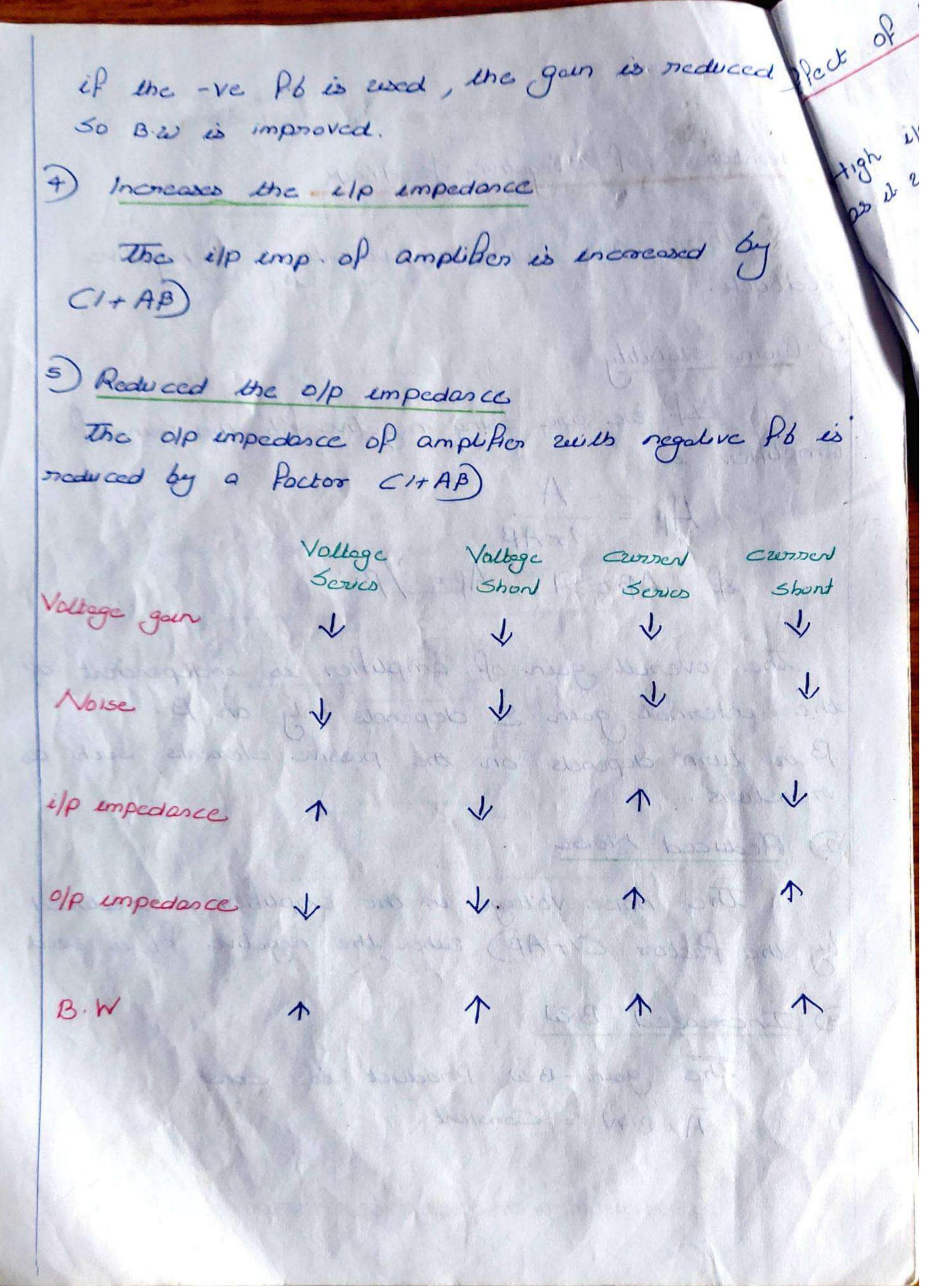

### Advantages Of Negative Readbook

There are numerous advantages of negative

( Grown stability

If we are using regalive P.b., the gain of

Ap = AAB

if AB>>1; AF= /B

The overall gain of amplifier is independent of the internal gain 2 depends only on B. B is turn depends on the possive elements such as resistors.

# 2) Reduced Noise

The noise voltage in the amplifier is reduced by the factor (1+ AB) when the negative fib is used

# 3) Increased B.W

The gain - BW Product is const.

A x B.W = Constant.

of Negative Feedback On input impedance: ilp impedance is always desinable in an ampliber as it swill not lood proceeding stage In = Vin = Vs - Vp July Vs - B Vout = Vs - BAVin 1200 1300 1 190 155 1099 8 InZin = Vs - BAVin => Vs = Inzin+ ABVin = InZin+ ABIInZin = Zin [Iin] fit AB? Vs = Zin C1+ AB) In . Thus ilp impedance is Zinf=Zin (1+AB) =>

Effect of Regalize feedback on output impedial

The old impedance should be low.

Vout = I out Zout + AVin

Vin = Vf

= I out Zout - AVF

= I out Zout - A (BVout)

Vout + AB Vout = Iout Zout Vout (1+ AB) = Iout Zout

Vout = Zout \( \beta = \frac{\text{Zout}}{(1+AB)} = \frac{\text{Olp impedance is reduced}}{\text{500}} \)

Tout \( \text{O' to AB} \)

Effect of negative Reedbock on Bandwidll

The lower cut off focusery is reduced & exper-cut off focusing is incoressed. Thus band-walls is incoressed. The gain is reduced but it remain stable.

B. W with feed book = (1+ AB) B. W without feed book.

( MA ) I ME

amplifier has an up impodance of this & old ump 10 Kr 80 voltage gain of 10,000. If a negative ecosbock of B = 0.02 is applied to it determine the Up & olp impedances of amplifier. Open 1000 gain, A = 10.000 B = 0.02 Zin = 1 K Zout = 10 K Zinf= CI+ AB) Zin = (1+10.000×0.02) 1×10 Zout Pz Zout: 1+AB 1+0.02×10,000 = 49.752 2. An amplifier such negative feed back has a vallege gain of 100. It is found that southout feedback an ilp signal of 50 mV is orequired to produce a given olp whereas such feedback, the ilp signal must be 0.6 V For some olp. Calculate A&B. Ap = 100 Voret = 2 Vin = 50 mV Voutp = 9 Vinp = 0-6 V

Vout = VoutP

Scanned by TapScanner

$$A = \frac{Vout}{V/n} = \frac{Vout}{0.05}$$

$$A\beta = \frac{Vout}{Vin} \beta = \frac{Vout}{0.6}$$

$$Vout \beta = Ioo \times ob = \frac{bo}{0.6}$$

$$Vout \beta = Vout = \frac{bo}{0.05}$$

$$Vout \beta = \frac{Vout}{Vin} = \frac{60}{0.05} = \frac{1200}{0.05}$$

$$A\beta = \frac{A}{I + A\beta}$$

$$Ioo = \frac{1200}{I + 1200 \times \beta}$$

$$\beta = \frac{916 \times 163}{0.05}$$

$$Abd = \frac{1200}{0.05}$$

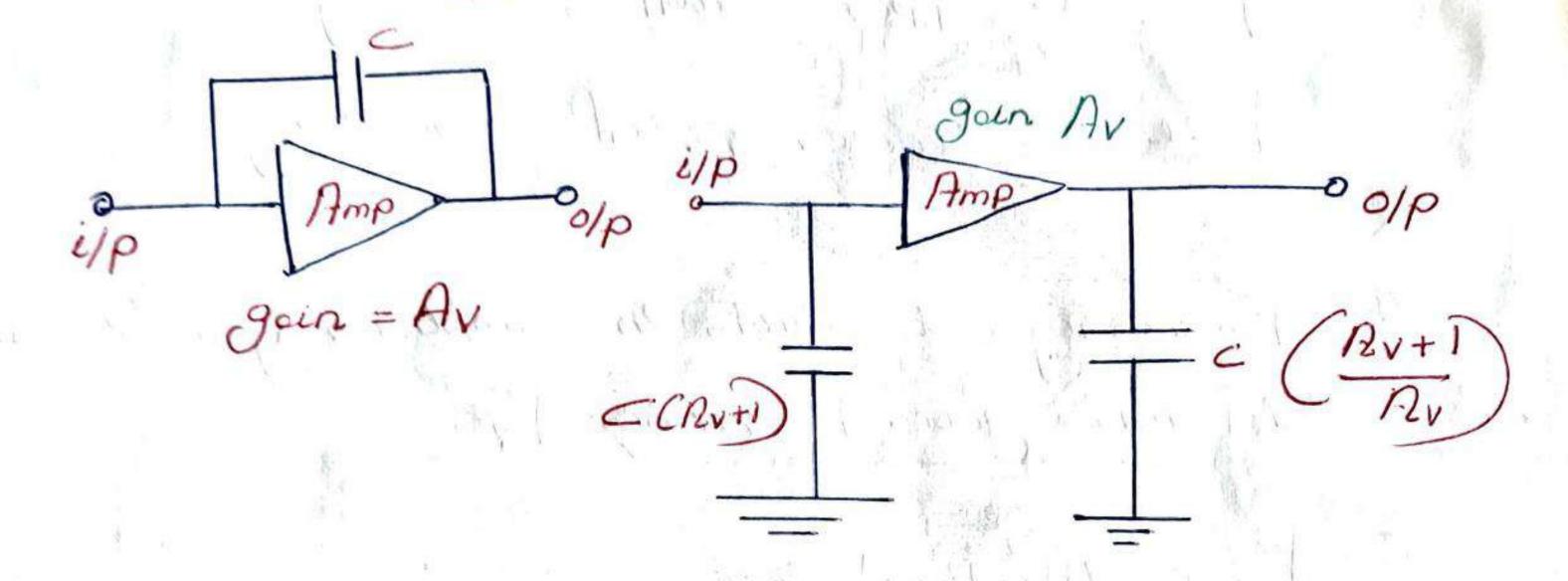

54g Miller's Theonem

Driving high Possesses the internal capacitance of amplifier is important. The capacitance Cbc (base & callectar) blow ilp & olp is shown

Millers theorem states that the capacitance Cappears as the capacitance from 11p to god.

It also states that the C'appears as the capacitance from O/P to gnd.

Grain Bandleboth Product The product of vollage goin & banden the always constant. Bw = Peu - Peu Par = repper critoff Pacquescy FCL => lower cutoff Prequescy The Poeruery at which the amplifier gain is 1 is colled unity gain Poeruercy PT. = Av. B.Zw Av => midrarge valtage gain. · m. Cimiler) ····· Jani. CA. MILITER COUNTY PROPERTY

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEEMING

#### Oscillators

Oscillator is a device used to generate oscillations authorit providing any ilp signals.

Oscillators

Non-Sinusoidal

D Rc oscillators

a) RC Phase Shift Oscillator

b) Wan Bridge Oxillator

2) Le oscillators

a) Hartley Oscillator

b) collapits oscillator

3) Crystal Oscillators

DRC-oscillators

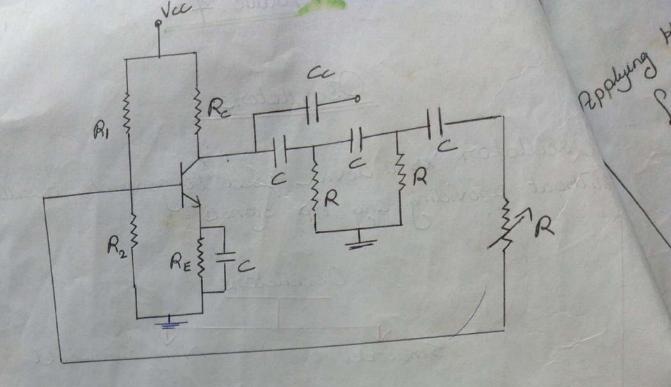

a) RC- phase Shift Oscillator

Borkhausen Criterian = Basic Principle

behind working of

all asolletors.

D/AB/21

P = gain of amplifier

B = Pecdbook Poctor

2) Phase still is 0°0,360°

The circuit is set into oscillations by any mandom on variation caused in the base current, that may be either due to noise inherent in the bransistan. This variation in base current is amplified in collectors Chit. The olp of the amplifier is supplied to an R-c feedback n/w.

The RC - n/w produces a phase shift of 180° 6/w 0/p & i/p voltages. Since CE amplifier produces a phase reversal of i/p signal, total phase shift becomes 0° on 360°. The o/p of this n/w is thus in same phase as that of i/p.

The equivalent CHL is shown

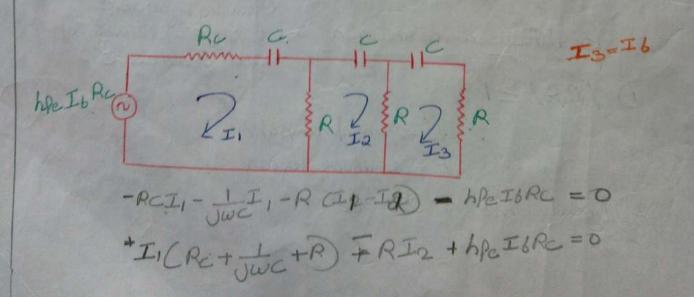

Replying Kinchoffs Vollage low

$$\begin{cases}

R + Rc + \frac{1}{jwc} \Im I_i - RI_2 + hpeI_bRc = 0 - cI

\end{cases}$$

$$-RI_1 + \left[2R + \frac{1}{jwc}\Im I_2 - RI_b = 0 - c2\right]$$

$$0 - RI_2 + \left[2R + \frac{1}{jwc}\Im I_2 - RI_b = 0 - c3\right]$$

$$\begin{vmatrix}

R + Rc + \frac{1}{jwc} & -R & hPeRc

\end{vmatrix}$$

$$R+Rc+Jwc -R hAeRc$$

$$-R 2R-JXc -R = 0$$

$$0 -R 2R-JXC$$

R+Rc-JXc[(2R-JXc)^2-R^2]+R[-R(2R-JXc)]+hpeRcR=0

Equating emogenery components

$$bR^2X_c + 4RR_cX_c - X_c^3 = 0$$

or  $X_c = \sqrt{bR_+^2 + 4RR_c}$

VBR2+4RRC P = 2TIC VBR2+4RRC P= 2TRC V6+4RC if R=Rc, ther P= ZTRCVIO Wien Bridge Oscillaton

The cht diagram of Wien bridge Oscillator is shown.

It is essentially a two stage amplifier with

R-c bridge (Wien bridge) cht. If Wien bridge is not

employed ofp of an is feelback directly to ai this

direct coupling will result in poor facturing stability.

Thus by employing Wien bridge fib n/w facturing stability

is increased.

Ri is in Sexues routs G, R3, R4 & R2 parallel ruits C2 Porms 4 arms.

The bridge is bolosced only when  $R_3 \left[ \frac{R_2}{1 + j w c_2 R_2} \right] = R_4 \left( \frac{R_1 - j}{w c_1} \right)$

on R2R3 = R4 C1+jw C2R2) CR1-j/wcj

R2R3-R4R1- 62 R2R4 + JR4 - JWC2R2R1R4 = 0

Seperating neal & imaginary terms

R2R3 - R4R1 - C2 R2R4 = 0

on  $\frac{C_2}{C_1} = \frac{R_3}{R_4} - \frac{R_1}{R_2}$

$\frac{2}{2UCI} \frac{R_4}{2UCI} - 2UC_2R_2R_1R_4 = 0$ or  $2U^2 = \frac{1}{C_1C_2R_1R_2}$

on

$$w = \sqrt{c_1 c_2 R_1 R_2}$$

$$P = \frac{1}{2\pi \sqrt{R_1 R_2 c_1 c_2}}$$

if

$$C_1 = C_2 = C$$

&  $R_1 = R_2 = R$ , then

$$f = \frac{1}{2\pi cR} 2 R_3 = 2 R_4$$

Thus in bridge clut of peull be in phase enth ilp, only ruher bridge is belanced. So this bridge cht can be used as feedback n/w for an oscillator, provided that the phase shift through amplifier is zero.

The olp of second stage is supplied book to fib n/w & Vollege across parallel combination R2C2 is fed to ilp of first stage. Q, act as oxillators & amplifier, Q2 act as inverter to cause a phase shift of 180°.

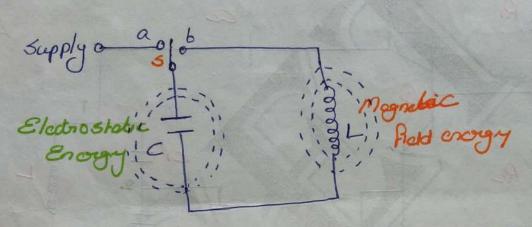

#### L-C oscillators

LC oscillators are used for high Poresucry generation. Hartley 2 colpits oscillators are two Prodically used IC oscillators.

The basic component of two L-c oscillators is a tank circleit.

The tank circuit consists of an inductive coil having inductance 'L' connected in parallel enith a copoulor hoving capacillance c'. The Pacquercy of oscillation depends on the volue of LEC.

If the switch is in position 'a', the current flows through capocitors. The capocitors begins to charge. It stores enough in the form of declarastatic. Thus there is electrostatic energy around the capoutors.

Pelher the copocitor is fully charged, it begins to discharge, ie, smitch will be en position b'.

Ther current begins to Plow Con the copocitors discharges through inductors. The inductors now stores energy in the form of magnetic field

That in Long out the alectrostate convented into magnetic Pield energy Calpiti's Oscillator

oscillator cut has an amplifier, 2 a book circuit he tank chit has two capocitors CI-C2 in parallel with an inductor L. The olp of tank cut is fed bock to ilp through coupling capacitors. Transistors itself. produces a phase shift of 180° 2 another phase shift of 180° is proovided by copacitive feed back. Thus a total Phose shift of 360° is obtained.

Elhan Vac is given, C18 C2 are changed. These Ci 2 c2 discharge through I, setting up oscillations of Prequercy  $f = \frac{1}{2\pi} \sqrt{\frac{1}{1c_1}} \frac{1}{1c_2}$ . The oscillations across  $c_2$  are applied to amplifier section.

β= C1 C2

Minimum gain to sustain oscillation, Amin = 1

#### Haritley Oscillator

Hartley Oscillator CKI is similar to Calpilla except that phase shift n/w consists of two inductors accept that phase shift n/w consists of two capoutors & 1,2 L2 & capoutors C, instead of two capoutors & one inductors. The operation of CKI is similar to corpitals Oscillators.

Pocquescy of Oscillation

$$F = \frac{1}{2\pi\sqrt{\left[C(L_1+L_2+2M)\right]}}$$

#### Desiration of Oscillators Processery of 6 Colpits & Harry Oscillators

(10 marks)

The hybrid equivolent model is drawn with following assumptions.

- \* hre is small, . hore Vout is negligible.

- Khoe is small, ... hoe is omitted

$$I = \frac{1}{Z1} + \frac{Z_0 + hic}{hic}$$

$$= hie (Z_0 + Z_3) + Z_0 Z_3$$

$$= hie (Z_0 + Z_3) + Z_0 Z_3$$

$$Z_1 \left[ hie (Z_0 + Z_3) + Z_0 Z_3 \right]$$

$$Z_1 = \frac{1}{hic} \left( \frac{Z_0 + Z_3}{Z_0 + Z_0 Z_3} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_3}{Z_0 + hic} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_3}{Z_0 + hic} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_3}{Z_0 + hic} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_0}{Z_0 + Z_0} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_0}{Z_0 + Z_0} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_0}{Z_0 + Z_0} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_0}{Z_0 + Z_0} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

$$= \frac{1}{hic} \left( \frac{Z_0 + Z_0}{Z_0 + Z_0} \right) + \frac{1}{2} \left( \frac{Z_0}{Z_0} \right)$$

Eastilute the volue of ZL in ca) in ci) ] hie (z1+z2+z3) + z1z2 (1+hpe) + z2z3 =0-0 The above is the general equation for LC asullator  $Z_{1} = \frac{1}{\int 2\omega C_{1}}, Z_{2} = \frac{1}{\int 2\omega C_{2}}, Z_{3} = 0$ Substitute  $Z_{1}, Z_{2} = Z_{3}$  in Equ. (2) \* For calputs. hie 1 + 1 + JWL + 1 (1+hfc)  $+ \frac{1 - \times 0201}{0000} = 0$ ナージ After sepending ned & emogenam parts -j'hic  $\left[\frac{1}{2\nu c_1} + \frac{1}{2\nu c_2} - 2\nu L\right] - \frac{1+hfe}{2\nu^2 c_1 c_2} + \frac{L}{c_2} = 0$ Equality emiginary part to zero 20C1 + 1 = 20L  $\frac{C_1 + C_2}{2UC_1C_2} = 2UL \quad \text{on } 2U^2 = \frac{C_1 + C_2}{LC_1C_2}$  $2v = \sqrt{\frac{C_1 + C_2}{LC_1 + C_2}} = \sqrt{\frac{1}{LC_1} + \frac{1}{LC_2}}$

$$Z_1 = J2(L1HD)$$

$Z_2 = J2(L2HD)$ ,  $Z_3 = \frac{1}{J2UC}$

Substituc  $Z_1$ ,  $Z_2$  &  $Z_3$  en  $E_{2U}$   $C_2$ )

& Equating emaginary parts to  $Z_{2D}$

whice  $\begin{bmatrix} L_1 + L_2 + 2M - \frac{1}{2U^2C} \end{bmatrix} = 0$

Z1 = JW (L1+m) Z2 = JW (L2+m) Z3 = 1

$$L_{1}+L_{2}+2m=\frac{1}{2v^{2}C}$$

$$C = \frac{1}{2u^2}$$

$= \frac{1}{2u+2m}$

$= \frac{1}{\sqrt{2c(2u+2m)}}$

$$2U=2\pi P$$

$$\therefore P = \frac{2U}{2\pi} = \frac{1}{2\pi \sqrt{c(L_1+L_2+2m)}}$$

800

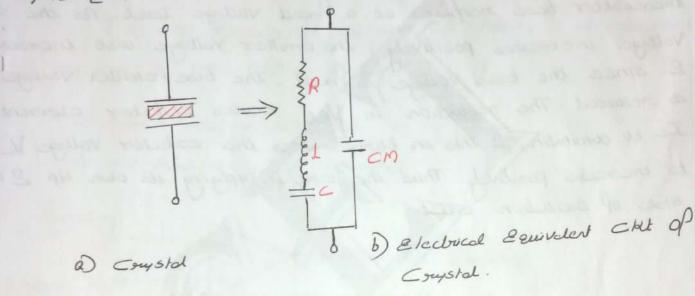

#### 3) Coustal Oscillators

5 marks

A quartz constal exhibits a very important property

Hnown as prezo-electric effect. When a mechanical processure

is applied across the faces of the crystal, a voltage

Proportional to mechanical processure appears across the

Constal 2 vice Versa

The constal actually behaves as a series RIC CHI in parallel with Cm. The constal has two resonant Porcenercies.

Series resonance Porcenercy for the which, 211fl = 1

& in this case constal impedance is low.

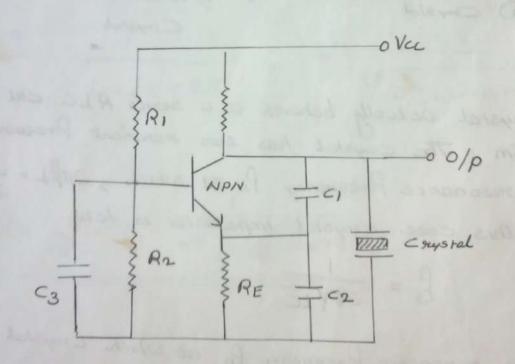

To stabilize the Procency of Oscillator, a competal most be operated at either its series on parallel mesonant Processery

Since parallel resonant impedance of crystal is maximum, it is connected in parallel. CI 2 Cr form a capacitor voltage divider which returns a partion of Olp voltage to the bransistors emitter. Capacitors C3 Provides an ac short cité across R2 to ensure that the bransistors base remains at a fixed voltage level. As the o/p voltage increases positively, the emitter voltage also increases 2 since the base voltage is fixed, the base-emitter voltage is reduced. The reduction in VBE causes collectors current Ic to diminish, 2 this in turn causes the collectors voltage Vc to increase positivel. Thus the cite is applying its own ilp 2 9 state of ascillation exist.

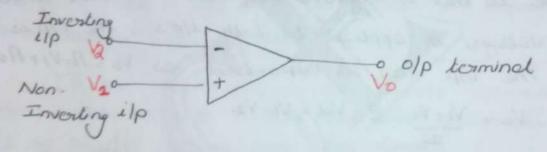

#### Operational Pumplifier

The op-emp is a multiterminal device which internally is quite complex. The op-amp's performance can be completely described by its terminal characteristics & those of external components that are connected to it.

The chit diagram of openp is shown. It has two ilp terminals & one of pterminal

-Ve => Inverting terminal

+Ve => Non inverting terminal

consider the op-amp shown in by This op-amp is said to be ideal if it has following characteristics

- D Open Loop vollage gain, ROL = d

- 2) Input impedance, Ri = L

- 3) olp impedance, Ro = 0

- 4) Bardwidth = do

- E) Zero Offset 10, Vo=0 ruhar V1= V2=0

The openp amplifies the diff. ilp Vd=V1-Va.

# Characteristics of Op-amp.

## 1) Common Mode Configuration

In the case of ideal op-amp, when the two ilp's are equal, there is no olp voltage. In practical case, the olp voltage depends not only upon the difference, the olp voltage depends not only upon the difference of the also depends upon the ava of ilp signal colled the common-mode signal; Vc = V1 + V2

For the differential amplifier, though the CHT 18

Symmetric, but because of the mismatch, the gain at

the old wint the positive terminal is slightly different

in magnitude to that of negative terminal. So ever when

the same voltage is applied to both i/p's, the old is

not zero. The old can be expressed as  $Vo = RiVI + ReVe^{-0}$

Since, Vc = V1+V2 & Vd = V1-V2

VI = Vc + Vd

V2 = Vc - Vd

substituting VI & V2 in (1)

Vo = Rd Vd + RcVc

Eutrere Rd = 1/2 (R1-R2)

Rc = RI+ R2

Rd => Vollage gain for diff signal

Ac => Vollage gain for common mode stynd.

The common made voltage gain, Rem = Vo

Common Mode Rejection Ratio (CMRR) is defined as rate of differential voltage gain to common made Voltage gain.

$CMRR = \frac{Rd}{Rcm}$

The value of Rem is very small compared to Rd.

... CMRR is very large.

Higher the Value of cmrr, better is the metching blew 2 ilp's terminals 2 smaller is the olp common-mode Voltage. Thus it has a better ability to reject common mode Voltages such as noise

If an emolesimable signal oppears common to both ilpis such as both noise, then the external to which it get rejected depends upon the CMRR

#### 2) Large Signal Vollage Grain

Since the op-amp, amplifies difference vallage blu two ilp terminals, the vallage gain of the amplifies is defined as

Vollage gain = O/P Vollage

differential e/P

12 = Vo/Viol

Since the old signal amplitude is much larger than ill's the vollage gain is commonly called large signal Vollage gain.

# 3) Slew Rote CSR)

It is defined as the maximum note of change of olp Voltage per unit of time

- The S.R indicates how napidly the Olp of an op-amp can charges in nesponse to charge in ilp forequescy.

- For ac application, particularly at relatively high foreguescy

SR of 10741 = 0.5V/Msec

the two sto temmet , we writer gon of the employed

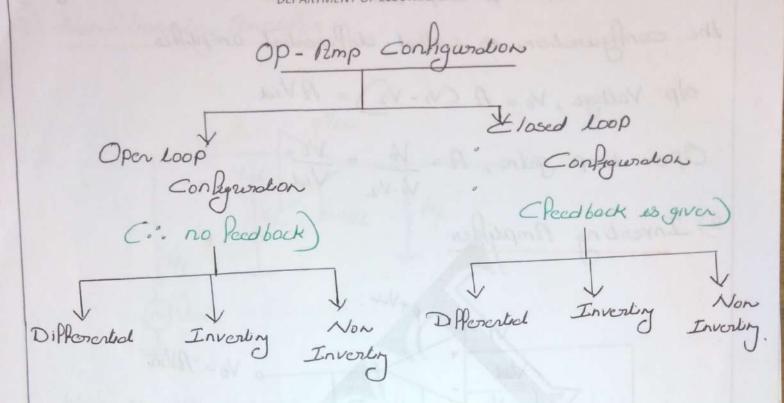

#### Open loop configuration

In the open loop configuration of op-emp, there is no connection exists blew old & ilp terminals, we the old signal is not feedback in any form as part of elp signal.

#### 1) Differential Amplifies

Here  $V_1$  &  $V_2$  are applied to +ve & -ve ilp terminals., Since the op-amp amplifies the diff blue two ilp signals. The configuration is called differential amplifies of Vallege,  $V_0 = A(V_1 - V_2) = AV_{id}$ .

Open loop gain,  $A = \frac{V_0}{V_1 - V_2} = \frac{V_0}{V_{id}}$ .

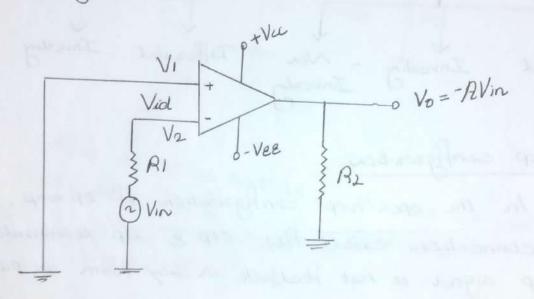

## 2) Inventing Rapifier

01

Only one ilp is applied ie, to the inverting ilp terminal. The non-inverting ilp terminal is grounded.

Since  $V_1=0$  &  $V_2=V_1$

$$V_0 = A (V_1 - V_2) = A (C - V_2)$$

$$V_0 = -A V_{in}$$

The negative sign indicates that old Vallage is out of phase 20-20 tip by 180°. There in the inventing amplifier the ilp signal is amplified by gain A 2 is also invented at old Vin

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

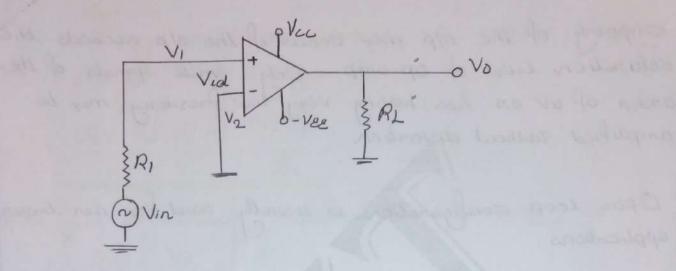

#### 3) Non-Inverting Bomplifics

Here the ilp is applied to the non-inverting ilp terminal & the inverting terminal is grounded.

$$V_{i} = V_{in} \quad 2 \quad V_{2} = 0$$

$$V_{0} = A \quad (V_{i} - V_{2}) = AV_{in}$$

$$A = V_{0} / V_{in}$$

This means that the old voltage is larger than the ilp Voltage by gain A & is in phase with the ilp signal.

Disadvantages Of Open Loop Configuration

- De Croin of amplifier may vary with temp 2 saturation

- DB-20 is very small & its almost zero . B. 20 refers to the range of Prequescies over rubich the gain rull remain constant ILAHLA COLLEGE OF ENGINEERING AND TECHNOLOGY

- 3) Open loop gain of op-amp is very high. So the olp is either the an -ve saturation an szuitches b/2 the on -ve saturation an szuitches b/2 the on -ve saturation so open loop configuration is not used for linear application.

- Elipping of the olp may occur if the olp exceeds the solution level of op-amp. Only small signals of the order of UV on less, having very low frequency may be amplified rulbout distortion

- epplications.

Closed Loop op-amp configurations

=> there is Pb Room olp to elp.

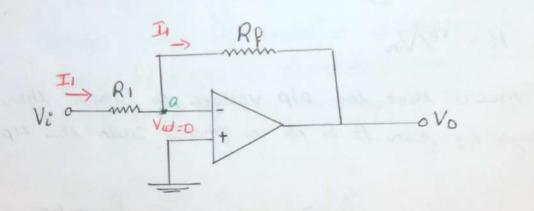

The Investing Pumplifier

The old voltage Vo is fib to the inverting ilp terminal through RP-R1 n/w, ruhere RP is the feedback resistors. ilp signal Vi is applied to inverting ilp terminal through R1 & non inverting ilp terminal of Op-amp is grounded. For simplicity, assume edeal op-amp

Pes Vid = 0, node 'a' at ground potential &

Since op-amp draws no current, all current Placeing through RR RI, Places through RR

$$V_0 = -I_1Rp = -V_1Rp$$

$$R_1$$

Hence gain of inventing amplifier (closed Loop) is  $RCJ = \frac{Vo}{Vi} = -\frac{Rp}{Ri}$

The negative sign indicates a phase shift of 180° b/w Vi & Vo.

### 2) Non Inventing Pamplifier

Notlege somes fib amplifier is also known as non-inventing fib amplifier because it uses fib & the ilp signal is applied to non-inventing ilp terminal of Op-amp.

Closed loop voltage gain, ACL = Vo = RI+RP = 1+ RP

Vin RI

#### ILAHIA COLLEGE OF ENGINERING AND TECHNOLOGY

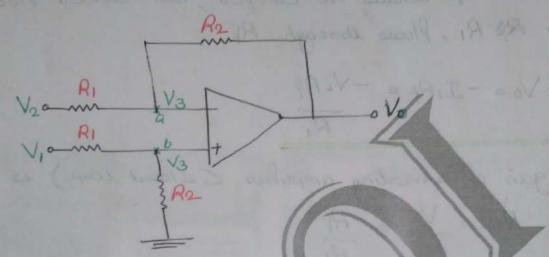

#### 3 Differential Amplifics

This amplifier amplifies the diff blu 1200 signals

Since the differential Noltege of ilp is zono

o' & b' are at some potential, w V3)

The nodel equation of a is

The nodel cruction at 'b' is

$$\frac{V_3-V_1}{R_1}+\frac{V_3}{R_2}=0$$

$$(\frac{1}{R_1} + \frac{1}{R_2}) V_3 - \frac{V_2}{R_1} = \frac{V_0}{R_2} - C_3$$

Vo = RQ (VI-VQ)

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

in detecting very small differences in signals.

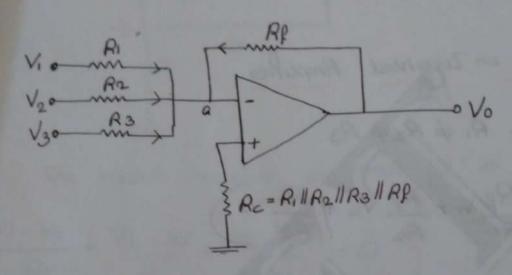

# Summing Ramplifics

Op amp may be used to design a cost whose olp is the sum of several up signals. Such a cat is called summing amplifier on a summer. The most ruseful application of op-amp is analog computer. This CHI can be used to add a dc signal on an ac Signal. This cast will produce an old Vollage which is proportional to on could to algebraic sum of all elp voltage 2 each multiplied by a constant gain foctors.

# a) Investing Summing Ramplifier

The inventing configuration consists of 3 ilp Voltages.

VI, V2 & V3 : 3 ilp resistors RI, R2, R3 & Rf. Assuming that the openp is ideal one (ie, Rol = & & RI=d & IB = 0). Since the ilp bias awarent is assumed to be zero there is no voltage drop across Re & hence the non-inventing ilp terminal is at ground potential.

The Voltage at node 'a' is zero as the non-invorting ilp terminal is grounded. The nodel equation by KCL at node 'a' is

$$\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}} + \frac{V_{0}}{RP} = 0$$

$$\frac{Rp}{R} = \frac{1}{n}$$

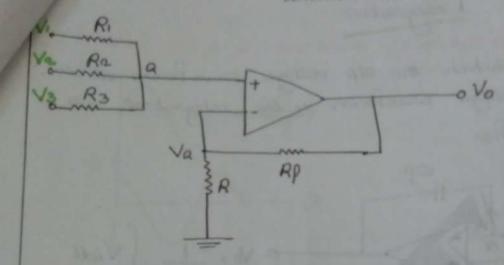

A summer that gives a non invented sum is the non inventing summing amplifier.

Tang Con

The nodal cevation at node '0' is

$$\frac{V_{1}-V_{0}}{R_{1}}+\frac{V_{2}-V_{0}}{R_{2}}+\frac{V_{3}-V_{0}}{R_{3}}=0$$

$$\sqrt{a} = \frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3}$$

The op-amp & two nexistors RP & R constitute

a non-investing amplifier with

No = (1+ RP) Va

: olp Vollage 10

$$V_0 = (1 + \frac{Rp}{R}) \frac{\frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3}}{\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}}$$

autich is a non-inverted weighted som of elp's

Let RI = R2 = R3 = R = RP/2

ILAHIA COLLEGE OF ENGINEERING IND TECHNOLOGY

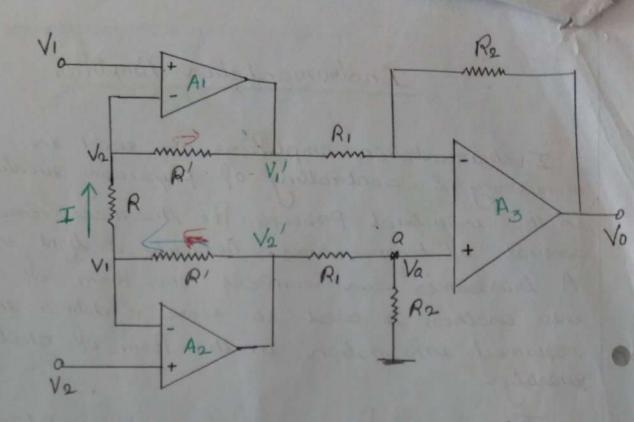

## Instrumentation PumplePier

Instrumentation amplifiers are used in monitoring & contractling of physical evanlibes, in the industrial Process for the measurement & contract of temperature, humidity & light intensity A transducer can convert one from of energy into another is used to sense & deliver the required information in the form of electrical quartity.

The major Purction of an instrumentation amplifiers is precise amplification of low level of.

Signal of toursducer.

-> AD 521, AD 524

Features

high gain accuracy

high CMAR

high gain stability

Low ofp impedance.

A, 2 A2 and Voltage Pollower on buffer akts acting as ilp stage for each of ilp's VI & V2.

Let  $V_1 = V_2 \implies$  The voltage across R is zero.

Since no avarants flows through R 2 R',  $V_1 = V_1$ ' 2  $V_2 = V_2$ '

If  $V_1 \neq V_2 \Rightarrow$  then crownert Plows throug R  $I = \frac{V_1 - V_2}{R}$

The Vollage at node a

$V_a = \frac{V_2' R_2}{R_1 + R_2}$

By supersposition theocras  $V_0 = \frac{-R_0}{R_1}V_1' + \left[\frac{1}{2} + \frac{R_0}{R_1}\right] \frac{R_2V_2'}{R_1 + R_0}$ Let  $R_1 \gg R_2$

Og

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

$$V_0 = \frac{R_2}{R_1} \left[ V_2 - V_1 - 2IR' \right] \longrightarrow C3$$

$$= \frac{R_2}{R_1} \left[ V_2 - V_1 - \frac{2R'}{R} V_1 + \frac{2R'}{R} V_2 \right]$$

$$V_0 = \frac{R_0}{R_1} \left[ 1 + \frac{2R'}{R} \right] \left( V_2 - V_1 \right)$$

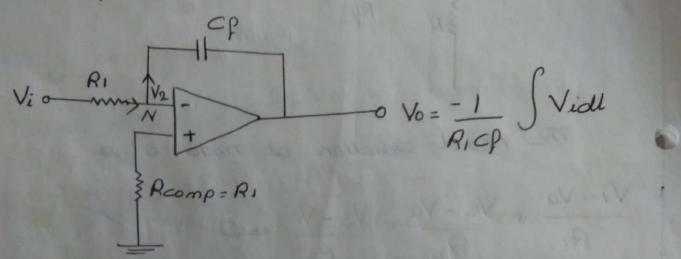

## Integrator

A clot in subject the old voltage waveform is the integrators on integrators amplifier

The nodal equation at node IN' is

$$\frac{V_{i-V_2}}{R_I} = C_F \frac{d}{dt} (V_2 - V_0)$$

N => Verteal goround.

$$\frac{Vi}{Ri} = -C\rho \frac{dVo}{dt}$$

$$\frac{dV_0}{dt} = \frac{-V_i}{R_i c \rho}$$

Rich = line const. I'mes the entogent of ilp.

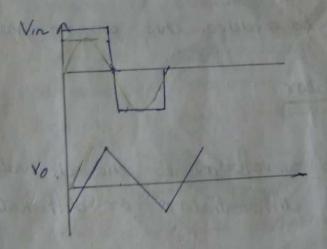

If the ip is a sine wave of paid be casine vin

\* If the up is a square wave, of is a briggular work

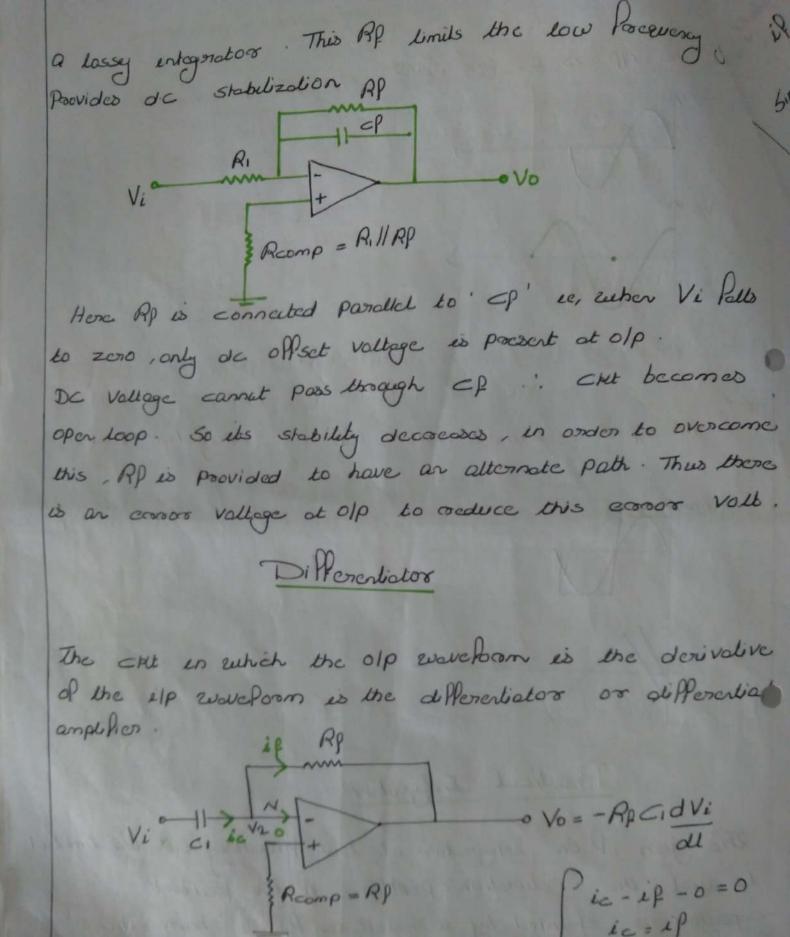

#### Producal Integrator

The gain of an integrator at low Processery can be limited to avoid the saturation problem if the Peedbock copacitors is shounted by a resistance RP as shown. The Parallel combination of RP & CP behaves like a Produced capacitors which abssipates power unlike an ideal capacitors For this reason, this city is also called MAHIA COLLEGE OF ENGINEERING AND TECHNOLOGY

the node N ic = if

ic = CId CVI-V2

Since V2 is the vertical ground

$$\frac{CidVi}{dt} = \frac{-V_0}{RP}$$

Thus the old voltage is - RPCI times derivative of ilp voltage.

The old is 180° oratof phase with ilp:

- 2 At high Poesuescy a differentiator may become , renstable 2 boeak into oscillations.

- Also the ilp impedance ( Vwc) decreases with the increase in Processery thereby making the cut sensitive to high Processery noise.

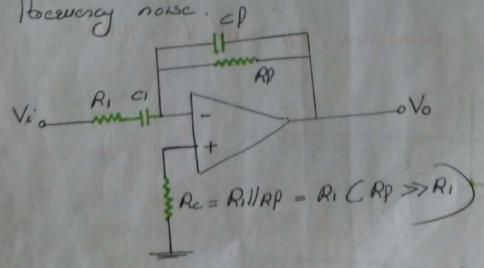

Bractical Differentiator EX

This can rull aliminate the problem of stability & high Posserior noise.

- To a capacitos 'Cp' is connected.

- Inorder to avoid noise disturbance RI is connected

The change in gain is caused by RICI 2 RPCP.

Thus the gain at high forevery is ordered - Significantly there by avoiding the high forevery noise 2 stability Problem

\* 49 the up sine river, 0/p will be cosine

\* if the up square move, of puill be spires

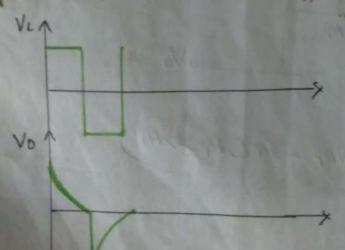

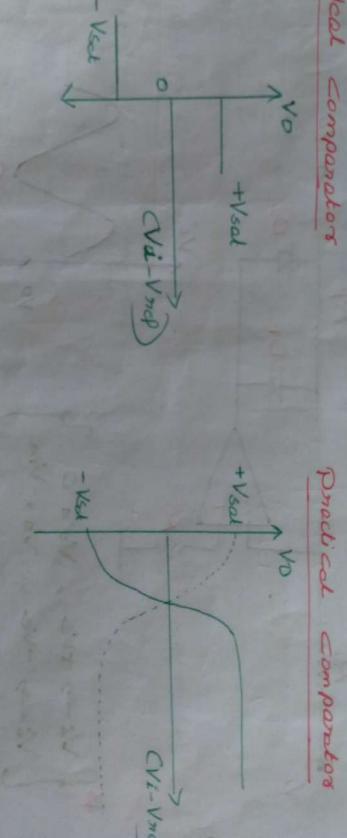

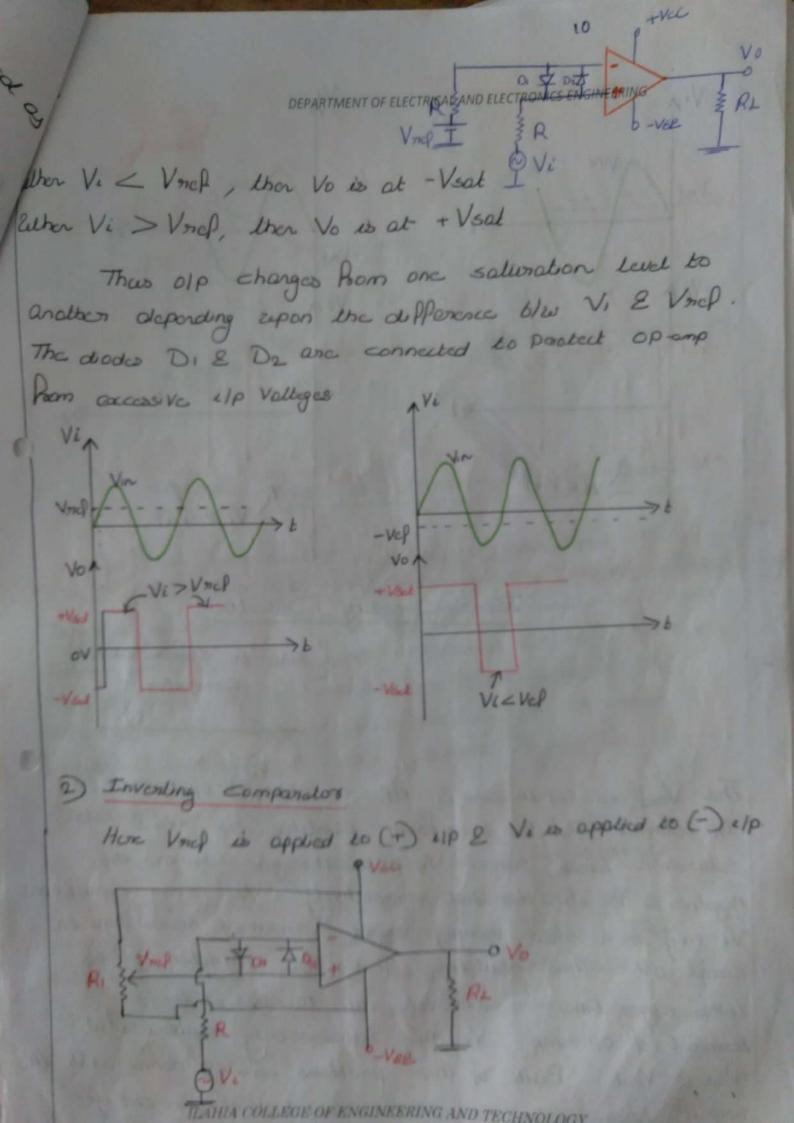

Companator

Known Inference Vallage at other ulp A comparator is a cut early compares a signal Voltage applied at one elp of an op-amp emits a

Ideal comparators

Two types of companators

I Non Inventing Comparators.

inventing all terminal & a time varying signal 'Vi' A hard inchence valtage Vinel is applied to the

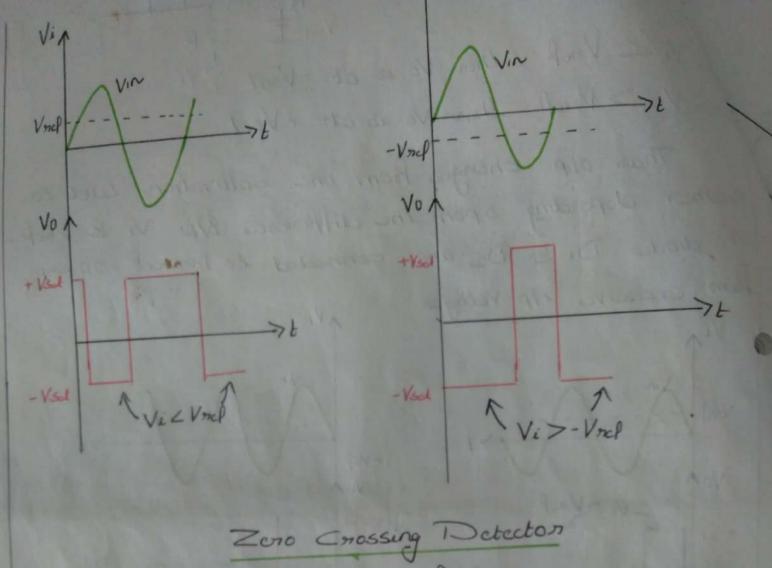

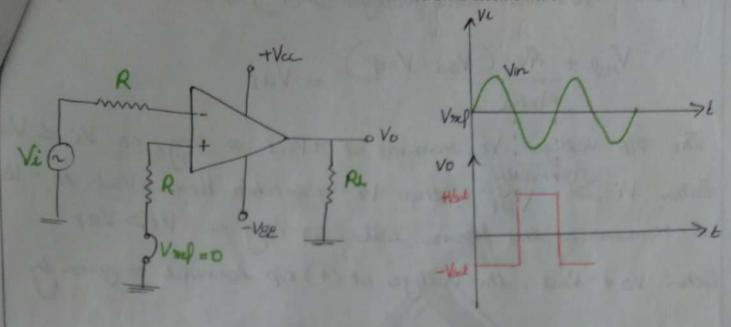

Zero Crossing Detector

Sine to square were

Converter 4

The Vnel is set to zero & ilp sine were is applied to (-) ilp terminal The olp were form sewitched blow +ve & -ve salwood on levels, ruhen Vi passes through zero in the negative & possitive direction nespectively. In some applications Vi may be a slow varying signal consoning more time to coass ov. Thus sewitching of vo blow solumation valleges takes larger time. Conversely due to noise at the ilp terminal of op-amp. Vo may runecessarily sawther blow that & -Vsal. Bath of these problems can overcome with the ruse of negerocrative an pasitive feed back in the out of Schmill Tringer.

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

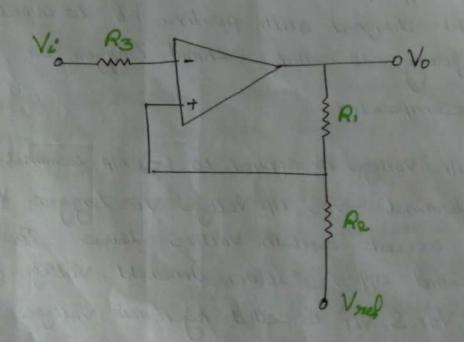

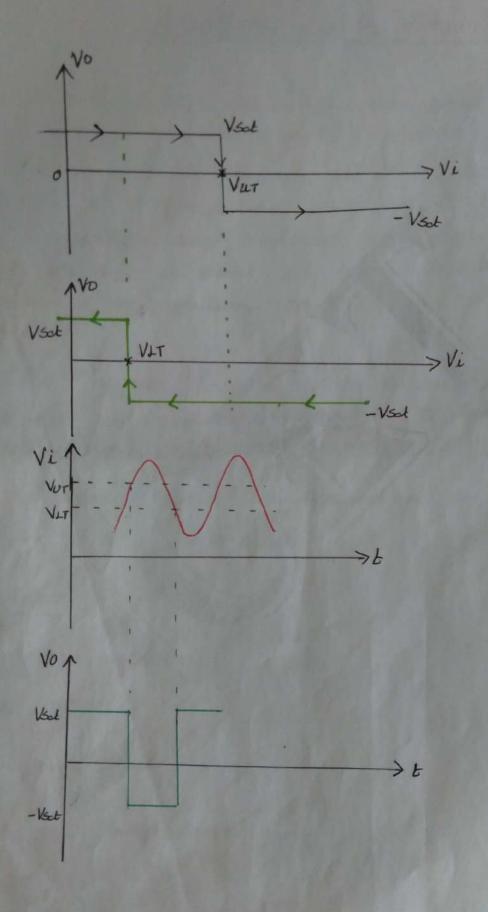

Schmitt Trigger on Regenerative Comparator

The basic comparators is used in open loop made. Since the openloop goth of openp is very large, fate. triggering at olp can occur ever due to small mill valts. Triggering at olp can occur ever due to small mill valts. When the charges slowly as compared to olp, noise is completed from olp of comparators back to the. The comparators cut designed with positive fib to avoid comparator cut designed with positive fib to avoid when wanted triggering is called schmill tragger or Regenerative comparator.

The up voltage is applied to (-) up terminal ?

Pb to (+) up terminal . The up voltage Vi triggers the olp Vo

everytime, it exceeds centain voltage levels. These

Voltages are called upper 2 Lower threshold Vallages { Vur, V+1}

The diff blu Vur 2 V+1 is called hystoxisis voltage

VH = VUT-VAT

Suppose Vo=+Vsat, then vallage at (+) up terminal u Vnel + Az (Vsot-Vnel) = Ver The old Voltage Vo memains at +Vsat as long as Vi < Van Elber Vi > VIII ther Vo Szentches Rom + Vsat to - Van & memoins at the same tevel as long as Vi>VIII When Vo = - Vsat, the voltage at (+) ilp terminal is given by Vncf - R2 (Vset + Vncl) = VLT Eucher Vi & Stightly VIT, Vo Szuitches Room - Vsat to + Vsat Hysterisis Zelidth VH = V217-VIT = 2R2Vsot

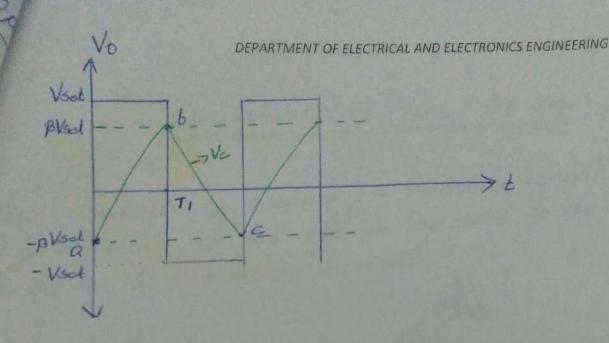

The fig shows asiable multivibrator with olp of openp feedback to C+) up terminal The oresistors Rig R2 from a vollage divides n/w 2 a Prochan B = R2 A+R2

Let ofp is at + Vsal

The Vollage at + 41p tersminal is at + BVset.

The Vollage at + 41p tersminal is at + BVset.

Charging of C' continues until Ve is just greated than Vallage at (+) 41p tersminal.

Buten this happens at Pt b' the old sauthed down to - Vset.

olp is now at - Vsol

=> Ther the copocitors 'c' starts charging

to vool.

There the copocitors 'c' starts charging

to vool.

There the copocitors 'c' starts charging

to vool.

At

$$t=T_1$$

,

$\beta V \cot = V \cot C 1 - CI+\beta e^{-T_1/RC}$

$$(I-\beta) = CI+\beta e^{-T_1/RC}$$

$$(I-\beta) = CI+\beta e^{-T_1/RC}$$

$$\Rightarrow T_1 = RC \ln \frac{I+\beta}{I-\beta} = RC \ln \frac{R_1 + 2R_2}{R_1}$$

$$\Rightarrow T_1 = RC \ln \frac{I+\beta}{I-\beta} = RC \ln \frac{R_1 + 2R_2}{R_1}$$

Total time Period,  $T = 2T_1 = 2RC \ln \frac{R_1 + 2R_2}{R_1}$

#### RAMP GENERATOR

If the step input of the integrating amplifier is replaced by a continuous time square wave, the change in the input signal amplitude charges and discharges the feedback capacitor. This results in a triangular wave output with a frequency that is dependent on the value of  $(R_0, C_0)$ , which is referred to as the time constant of the circuit. Such a circuit is commonly called a Ramp Generator.

During the positive half-cycle of the square wave input, a constant current I flows through the input resistor Rf. Since the current flowing into the op-amp internal circuitry is zero, effectively all of the current flows through the feedback capacitor C<sub>6</sub>. This current charges the capacitor. Since the capacitor connected to the virtual ground, the voltage across the capacitor is the output voltage of the op-amp.

During the negative half-cycle of the square wave input, the current I is reversed. The capacitor is now linearly charged and produces a positive-going ramp output.

AAA

(b) Output Wareform

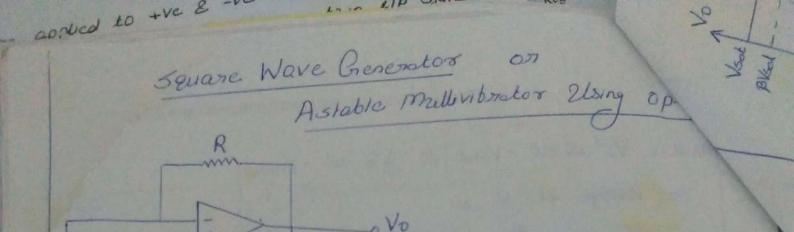

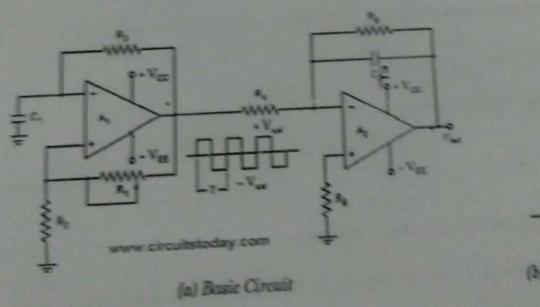

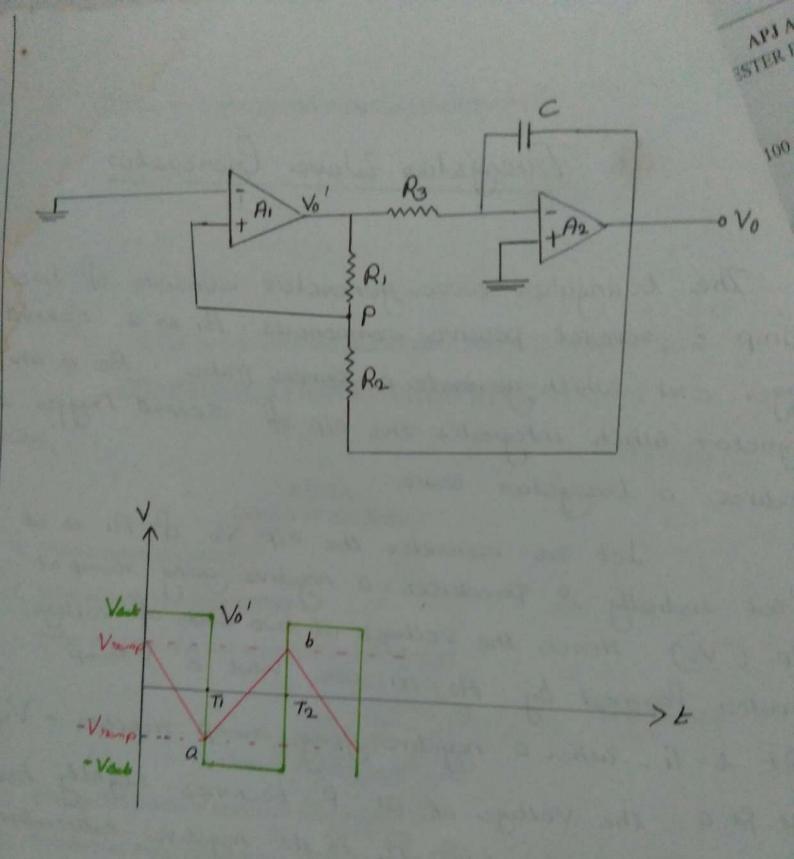

# Triangular Wave Grenerator

op amp 2 several passive components. Ph is a schmitt 1 sigger CM's evhich generate a square passe. Re is an integrator which integrates the old of schmitt trugger to The briangular every generators consists of Lwo

didon formed by Re-Ri are Vsat & Vnamp of (Vo). Hence the voltages at two ends of Nottage Produce a biggular wave. Let us consider the olp No of A1 is at

integraling 2 increases the old in possitive direction. At t=T2 at Pt 'b' the voltage at Pt P' becomes greater at Pi'a', the vollage at Pi P' becomes slightly less level - Vsat. Edills the olp of Ri at - Vsat, Re Starts than OV. This szentches Pi, to its regative saturation Pet t= Ti, Eutrer a regelve going manp meaches - Vnemp

than OV & Smitches Vo' to +Vsat. This cycle

7= 4R2R3C P. YT = R. 4R2R3C

Explain :

e generated i