### Module I

- SCR-Structure, static characteristics & switching (turn-on & turn-off) characteristics

- di/dt & dv/dt protection –

- turnon methods of SCR two transistor analogy - series and parallel connection of SCRs -Structure and principle of operation of power diode, TRIAC,GTO, Power MOSFET & IGBT – Comparison

# SCR (Silicon Controlled Rectifier)

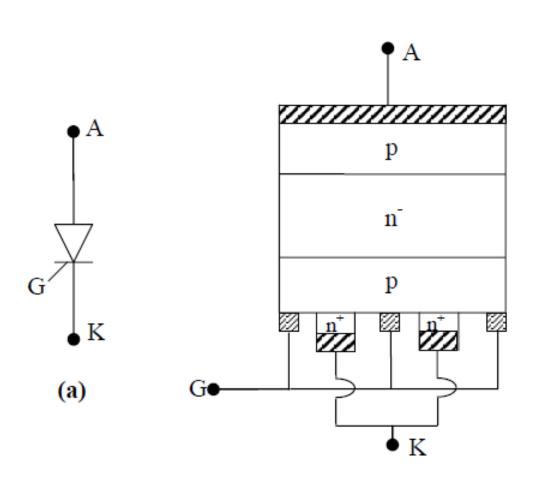

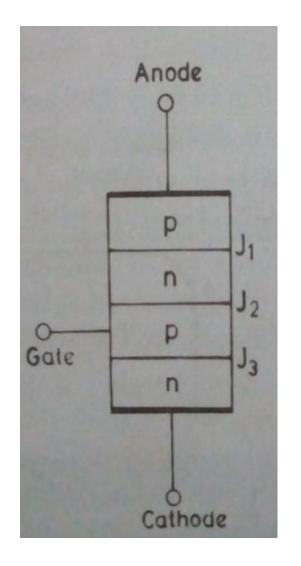

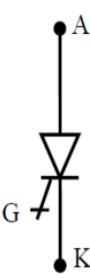

- Four layer, three junction, p-n-p-n semiconductor switching device.

- Basically a thyristor consist of 4 layers of alternate p-type and n-type silicon semiconductors forming three junctions J1, J2 and J3

# SCR (Silicon Controlled Rectifier)

- Gate terminal is usually kept near the cathode terminal

- The terminal connected to outer p region is called the anode

- The terminal connected to outer n region is called the cathode and that connected to inner p region is called gate

- ➤ For large current applications thyristors need better cooling, this is achieved to great extent by mounting them onto heat sinks

- SCRs of voltage rating 10kV and an r.m.s current rating of 3000A with corresponding power handling capacity of 30MW are now available

- Such a high power thyristor can be switched on by a low voltage supply of about 1A and 10W

- An SCR is so called because silicon is used for its construction and its operation as a rectifier can be controlled

- Like the diode SCR is a unidirectional device, that blocks the current flow from cathode to anode

- Unlike the diode, a thyristor also blocks the current flow from anode to cathode until it is triggered into conduction by a proper gate signal between gate and cathode terminal

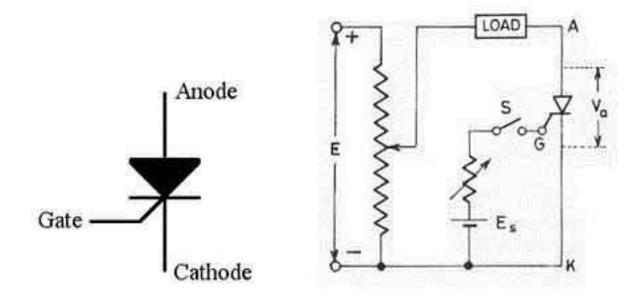

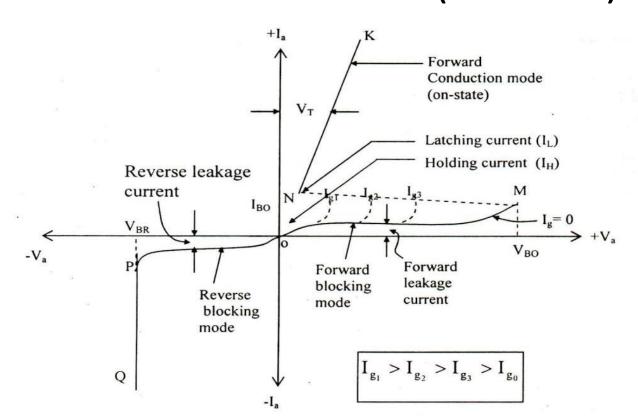

## SCR — Static V-I Characteristics

- An elementary circuit diagram for obtaining static V-I characteristics of a thyristor is shown below

- The anode and cathode are connected to main source through load

- The gate and cathode are fed from a source of Es which provides +ve gate current from gate to cathode

Thyristor Symbol Circuit diagram of thyristor.

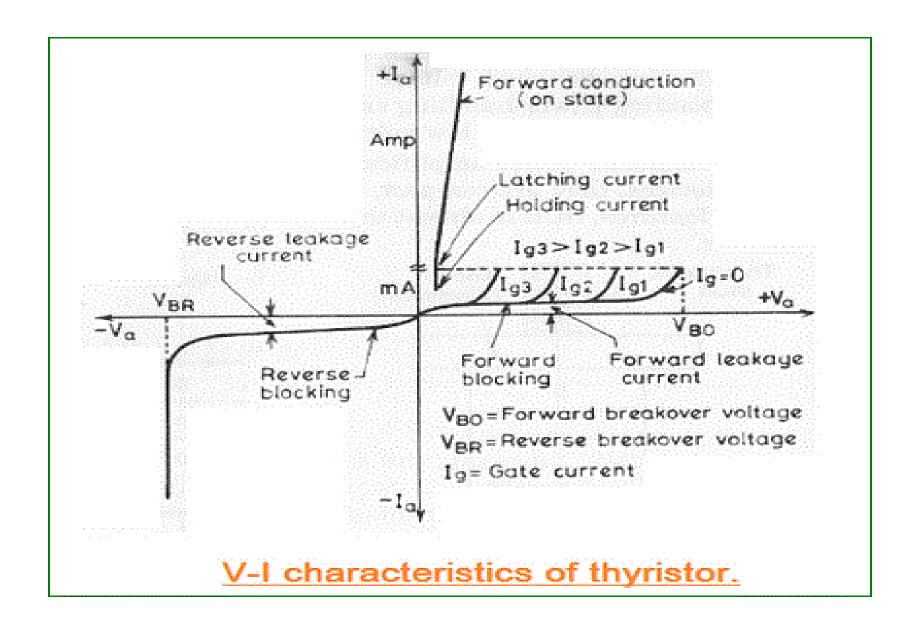

The characteristics reveals that a thyristor has three basic modes of operation Reverse blocking mode Forward blocking mode (off state) Forward conduction mode (on state)

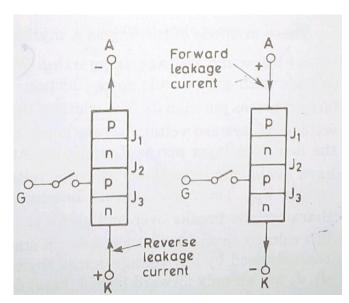

- Reverse blocking mode

- When cathode is made +ve w.r.t anode with switch S open thyristor is reverse biased Junction

- J1 and J3 are seen to be reverse biased

- A small leakage current of the order of a few milli-amperes flows. This is reverse blocking mode, called the off state of a thyristor

- If the reverse voltage is increased, then at a critical breakdown

- level, called reverse breakdown voltage VBR, an avalanche occur

at J1 and J3

Reverse current increases rapidly

## Forward blocking mode

- When anode is +ve w.r.t cathode, with gate circuit open,thyristor is said to be forward biased

- J1 and J3 are forward biased

- J2 is reverse biased

- In this mode, a small current called forward leakage current flows

- As the forward leakage current is small, SCR offer a high impedance

- Therefore a thyristor can be treated as an open switch even in the forward blocking mode

### Forward conduction mode

- When anode to cathode forward voltage is increased with gate circuit open, reverse biased junction J2 will have an avalanche breakdown at a voltage called forward break-over voltage VBO

- After this breakdown thyristor gets turned on with point M at once shifting to N and then to a point where between N and K

- Here NK represents the forward conduction mode

- A thyristor can be brought from forward blocking mode to forward conduction mode by turning on by applying

- 1)A positive gate pulse between gate and cathode

- 2)A forward break-over voltage across anode and cathode

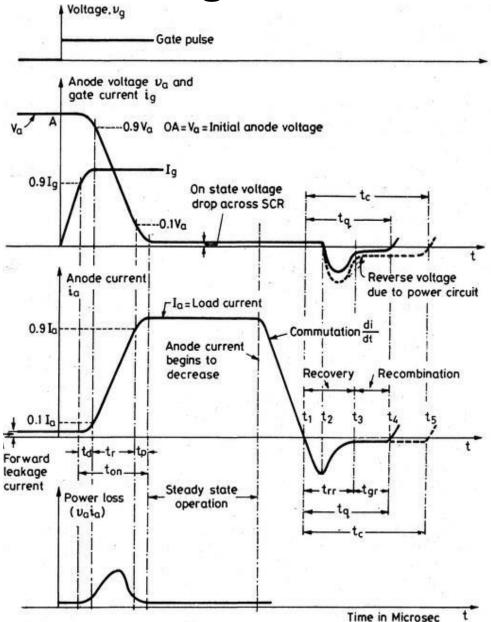

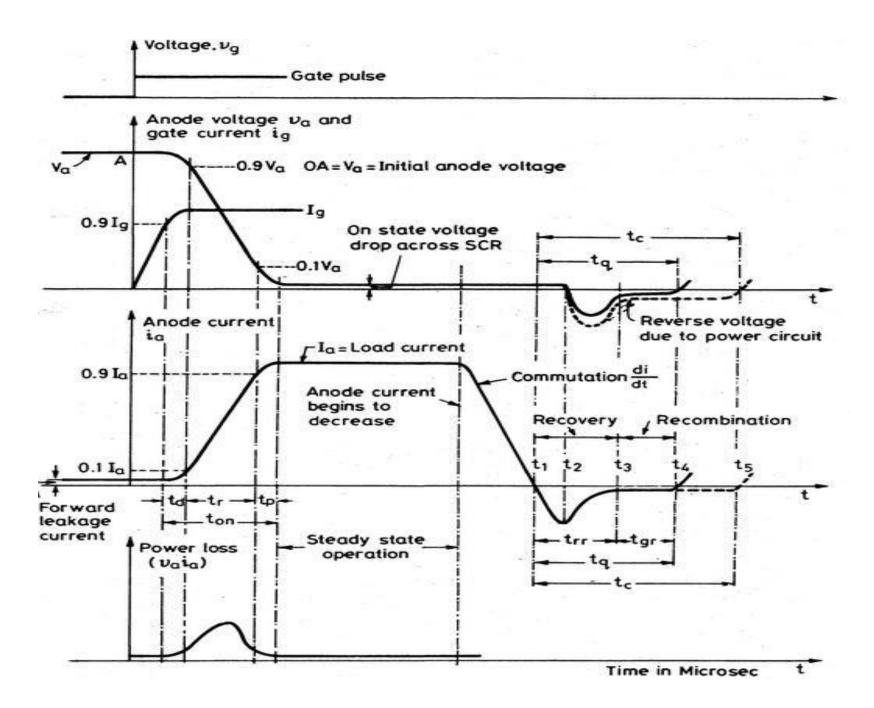

# SCR – Switching Characteristics

- During turn on and turn off process a thyrisor is subjected to different voltages across it and different currents through it

- The time variation of a voltage across a thyristor and the current through it during turn on and turn off process gives the dynamic or switching characteristics of a thyristor

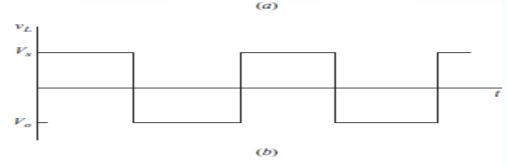

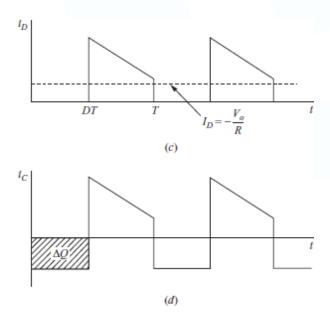

## SCR – Switching Characteristics

# Switching characteristics during turn on

- A forward biased thyristor is usually turned on by applying a +ve gate voltage between gate and cathode.

There is however a transition time form forward off state to forward on state.

- This transition time is called thyristor turn on time Is defined as the time during which it changes from forward blocking state to final on state

- The turn on time can be divide into three intervals

- Delay time td

- Rise time tr

- Spread time tp

## Delay time td

- Measured from the instant at which gate current reaches 0.9lg to the instant at which anode current reaches 0.1la

- Ig and la are the final values of gate and anode currents

- ➤ It can also be defined as the time during which anode voltage falls from Va to 0.9Va.Va is the initial value of anode voltage

- Another way of defining is the time during which anode Current rises from forward leakage current to 0.1Ia, where Ia is the final value of anode current

- ➤ With the thyristor initially in the forward blocking state the anode voltage is OA and anode current is small leakage current

- Initiation of turn on process is indicated by a rise in anode current from small leakage current and a fall in anode cathode voltage from forward blocking voltage OA

- ➤ As gate current begins to flow from gate to cathode with the application of gate signal, the gate current has non-uniform distribution of current density over cathode surface due to the p layer

- During delay time anode current flows in a narrow region near the gate where gate current density is the highest

- The delay time can be reduced by applying high gate current and more forward voltage between anode and cathode

- > The delay time is fraction of microsecond

#### Rise time

- ➤ Is the time taken by the anode current to rise form 0.1la to 0.9la

- ➤ Time required for the forward blocking off state voltage to fall from 0.9 to 0.1 of its initial value

- Rise time is inversely proportional to the magnitude of gate

- current and its build up rate

- Rise time can be reduced if high and steep current pulses are applied to the gate

- The main factor determining the tr is the nature of anode circuit

- ➤ During rise time turn on losses in the thyristor are the highest due to high anode voltage and large anode current occurring together in the thyristor

- As these losses occur only over a small conducting region, local hot spot may be formed

- ➤ And the device may be damaged

## Spread time

- ➤ Time taken by the anode current to rise from 0.9Ia to Ia Time for the forward blocking voltage to fall from 0.1 of its initial value of its on state voltage drop (1 to 1.5V)

- During this time conduction spreads over entire cross section of the cathode of SCR

- ➤ After the spread time anode current attains steady state value and the voltage drop across SCR is equal to the on state voltage drop of the order of 1 to 1.5V

- Total turn on time of an SCR is equal to the sum of delay time, rise time and spread time

- Manufactures usually specify the rise time which is of the order of 1 to 4μ sec

- Total turn on time depends on the anode circuit parameters and gate signal wave-shapes

# Switching characteristics during Turn off

- > Turn off means that it has changed from on to off state and is capable of blocking the forward voltage

- ➤ This dynamic process of SCR from conduction state to forward blocking state is called commutation process or turn off process

- Once the thyristor is on, gate loses control the SCR can be turned off by reducing the anode current below holding current

- The turn of time tq of a thyristor is defined as the time between the instant anode current become zero and the instant SCR regains forward blocking capability

- During time tq, all the excess carriers from the four layers of SCR must be removed.

- This removal of excess carriers consisting of sweeping out of holes from outer p layer and electrons from outer n layer

- The carriers around junction J2 can be removed only by

- recombination

- The turn off time is divided into two interval

- 1) Reverse recovery time trr

- 2) Gate recovery time tgr

- tq=trr+tgr

## Reverse recovery time

- > At instant t1, anode current becomes zero

- After t1, anode current build up in the reverse direction

- ➤ The reason for the reversal of anode current after t1 is due to the presence of carriers stored in the four layers

- ➤ The reverse recovery current removes excess carriers from the end junction J1 and J3 between the instant t1 and t3

- > In other words, reverse recovery current flows due to the

- sweeping out of holes from top p layer and electrons from bottom layer

- At instant t2, when about 60% of the stored charges are removed from the outer two layers carrier density across J1 and J3 begins to ecrease and with this reverse recovery current also starts decaying

- The reverse current decay is fast in the beginning but gradual thereafter

- The fast decay of the recovery current causes a reverse voltage across the device due to the circuit inductance

- This reverse voltage surge may cause damage to the device

- In practice this avoided by using protective RC element across SCR

- At instant t3, when reverse recovery current has fallen nearly to zero, end junction J1 and J3 recover and SCR is able to block the reverse voltage

## Gate recovery time

- ➤ At the end of reverse recovery period (t1-t3), the middle junction J2 still has trapped charges therefore, the thyristor is not able to block the forward voltage at t3

- The trapped charges around J2 cannot flow to the external circuit

- > Therefore this charges must decay only by recombination

- This recombination is possible if a reverse voltage is maintained across SCR The rate of recombination of charges is independent of the external circuit parameter

- ➤ The time for recombination of charges between t3 and t4 is called gate recovery time tgr

- At instant t4, junction J2 recovers and the forward voltage can be reapplied between anode and cathode

- The turn off time provided to a thyristor by the practical

- circuit is called circuit turn off time to

- Is defined as the time between the instant anode current

- become zero and the instant reverse voltage due to practical circuit reaches zero

- tc must be greater than tq for reliable turn off

- Otherwise the device may turn on at undesired instant, process called commutation failure

# Thyristor protection

- Reliable operation of a thyristor demands that its specified ratings are not exceeded. In practice, a thyristor may be subjected to overvoltage or over-currents

- During SCR turn on, di/dt may be prohibitively large

- There may be false triggering of SCR by high value of dv/dt

- A thyristor must be protected against all such abnormal conditions for satisfactory and reliable operation of SCR circuit and the equipment

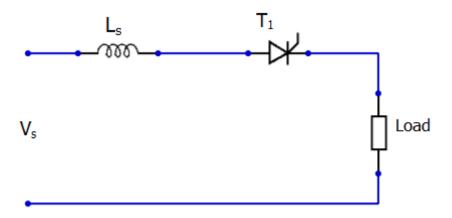

#### di/dt protection

- When a thyristor is forward biased and is turned on by a gate pulse, conduction of anode current begins in the immediate neighborhood of the gate cathode junction

- Thereafter the current spread across the whole area of the junction

- The thyristor design permit the spread of conduction to the whole junction area as rapidly as possible

- However if the rate of rise of anode current i.e., di/dt is large as compared to the spread velocity of carriers, local hot spot will be formed near the gate junction. This localized heating may destroy the thyristor.

- Therefore the rate of rise of anode current at the time of turn on must be kept below the specified limiting value

- The value of di/dt can be maintained below acceptable limit by using a small inductor called, di/dt inductor in series with the anode circuit

- Typical di/dt limit values of SCR are  $20 500 \text{ A}/\mu \text{ sec}$

- Local hot spot heating can also be avoided by ensuring that the conduction spreads to the whole area as early as possible

- This can be achieved by applying agate current nearer to the maximum specified gate current

di/dt=Vs/Ls

Ls – series inductance including stray inductance

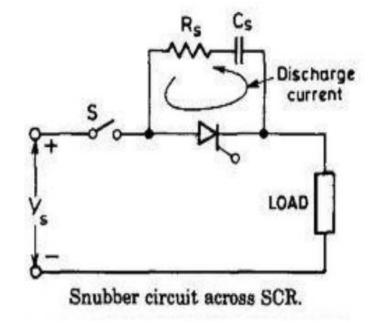

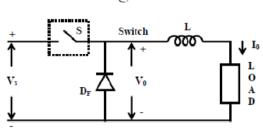

#### dv/dt protection

- If rate of rise of suddenly applied voltage across thyristor is high, the device may get turned on

- Such phenomena of turning on a thyristor is called dv/dt turn on And this must be avoided as it leads to false operation of the thyristor circuit

- For controllable operation of the thyristor, the rate of rise of anode to cathode voltage dVa/dt must be kept below the specified limit

- Typical value of dv/dt are 20 500V / μ sec

- False turn on of a thyristor by large dv/dt can be prevented by using a snubber circuit in parallel with the device

- Snubber circuit

- Consist of a series combination of resistance Rs and capacitance Cs in parallel with the thyristor

- Cs in parallel with the device is sufficient to prevent unwanted

- dv/dt triggering of the SCR

- When switch S is closed, a sudden voltage appear across the circuit Capacitor Cs behaves like a short circuit, therefore voltage across SCR is zero

- With the passage of time voltage across Cs builds up at a slow rate such that dv/dt across Cs and therefore across SCR is less than the specified maximum dv/dt rating of the device

- When the SCR is turned on capacitor discharges through the SCR and sends a current equal to Vs/ (resistance of the path formed by Cs and SCR)

- As this resistance is quite low, the turn di/dt will tend to be excessive and as a result SCR may be destroyed

- In order to limit the magnitude of discharge current a resistance Rs is inserted in series with Cs

- The value of snubber circuit constant  $\tau$ =RsCs can be determined from for a known value of dv/dt.

$$\frac{dv}{dt} = \frac{V_s}{R_s C_s}$$

• The value of Rs is found from

$$R_s = \frac{V_s}{I_{TD}}$$

The discharging current

$$I_{TD} = \frac{V_s}{R_1 + R_2}$$

## Turn on methods of SCR

With anode +ve w.r.t cathode, a thyristor can be turned on by any one of the following techniques

Forward voltage triggering

Gate triggering

dv/dt triggering

Temperature triggering

Light triggering

#### Forward voltage triggering

- When forward voltage applied between anode and cathode with gate circuit open, junction J2 is reverse biased

- As a result depletion layer formed across J2

- The width of this layer decreases with an increase in anode cathode voltage

- If forward voltage across anode-cathode is gradually increased, a stage come when depletion layer across j2 vanishes

- At this moment reverse biased junction J2 is said to have avalanche breakdown and the voltage at which this occur is called forward break-over voltage

- The name forward break-over voltage is given because at this voltage V<sub>BO</sub> v-i characteristics break-over and shift to its on state position with brek-over current I<sub>BO</sub>

- At this voltage, thyristor changes from off state (high voltage with low leakage current) to on state characterized by low voltage across thyristor with large forward current

- As other junction J1, J3 are already forward biased, breakdown of junction J2 allows free movement of carriers across three junctions and as a result large forward anode current flows

- This forward current is limited by load impedance

- In practice the transition from off state to on state obtained by exceeding V<sub>BO</sub> is never employed as it may destroy the device

### Gate triggering

- Turning on thyristor by gate triggering is simple, reliable and efficient

- It is therefore the most usual method of firing the forward biased SCR

- A thyristor with forward break-over voltage (say 800 V) higher than the normal voltage (say 400V) is chosen

- This means that thyristor will remain in forward blocking state with normal working voltage across anode and cathode and with gate open

- However when turn of a thyristor required, a +ve gate voltage between gate and cathode is applied

- The forward voltage at which the device switches to on state depends on the magnitude of gate current

- Higher is the gate current lower is the forward break-over voltage

- When +ve gate current is applied, gate p layer is flooded with electrons from the cathode

- This is because cathode n layer is heavily doped as compared to gate p layer

- As the thyristor is forward biased, some of these electrons reaches junction J2

- As a result width of the depletion layer near junction J2 is reduced

- This cause the junction J2 to break down at an applied voltage lower than the forward break-over voltage VBO

# Turn on methods of SCR

- Once the SCR is conducting a forward current, reverse biased junction J2 no longer exist

- No gate current is required for the device to remains in on state

- Therefore if the gate current is removed, the conduction of current from anode to cathode is unaffected

- However if the gate current reduced to zero before rising the anode current attains a value, called latching current the device will turn off again

- The latching current may be defined as the minimum value of anode current which it must attain during turn on process to maintain conduction when gate signal is removed

- Once the thyristor is conducting, gate loses control

- The thyristor can be turned off only if the forward current falls below a low level current called holding current

- The holding current may be defined as the minimum value of anode current below which it must fall for turning off the thyristor

- The latching current is higher than holding current

- The latching current is associated with the turn on process and holding current with turn off process

- Usually latching current is 2 to 3 times the holding current

- In industrial applications, holding current (typically 10 m A) is almost taken as zero

## dv/dt triggering

- With forward voltage across anode and cathode, the two outer junctions J1 and J3 are forward biased and inner junction J2 is reverse biased

- This reverse biased junction J2 has the characteristics of a capacitor due to charges existing across the junction

- In other words space charge exist in the depletion region near junction J2 and therefore junction J2 behaves like a capacitance

- If forward voltage is suddenly applied, a charging current through junction capacitance Cj may turn on the SCR

- Almost the entire suddenly applied forward voltage Va appears across junction J2 the charging current ic

$$i_c = \frac{dQ}{dt} = \frac{d}{dt}(C_j.V_a) = C_j \frac{dV_a}{dt} + V_a \frac{dC_j}{dt}$$

As the junction capacitance is almost constant, dCj/dt is zero and current ic,

$$i_c = C_j \frac{dV_a}{dt}$$

- $i_c = C_j \frac{dV_a}{dt}$  If the rise of forward voltage dVa/dt is high, the charging current ic would be more

- This charging current plays the role of gate current and turn on the SCR even though gate signal is zero

- Note that even if Va is small, it is the arte of change of Va that plays the role of turning on the device

#### Temperature triggering (thermal triggering)

- During forward blocking, most of the applied voltage appears across reverse biased junction J2

- This voltage across J2, associated with leakage current, would rise the temperature of this junction

- With increase in temperature, width of depletion layer decreases

- This further leads to more leakage current and therefore more junction temperature

- With this cumulative process at some high temperature, depletion layer of reverse biased junction vanishes and the device gets turned on

### Light triggering

• For light triggered SCR, a recess is made in the inner p layer

• When this recess is irradiated free charge carriers are generated just like when gate signal is applied between gate and cathode

Light p  $p_1(p^+) 10^{19} \text{cm}^{-3}$   $p_1(p^+) 10^{19} \text{cm}^{-3}$   $p_2(p^+) 10^{17} \text{cm}^{-3}$   $p_2(p^+) 10^{19} \text{cm}^{-3}$   $p_3(p^+) 10^{19} \text{cm}^{$

- The pulse of light of appropriate wavelength is guided by optical fibers for irradiation

- If the intensity of this light thrown on the recess exceeds a certain value, forward biased SCR is turned on

- Such a thyristor is known as light activated SCR (LASCR)

- LASCR may be triggered with a light source or with a gate signal

- Sometimes a combination of both may be used

- Light triggered SCR have now been used in high voltage direct current (HVDC) transmission system

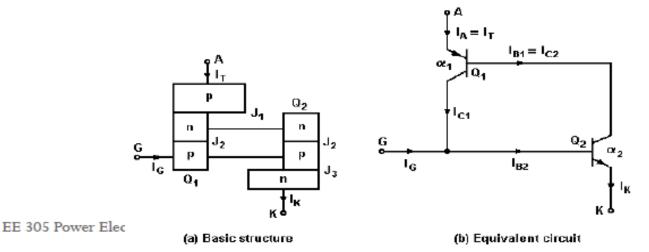

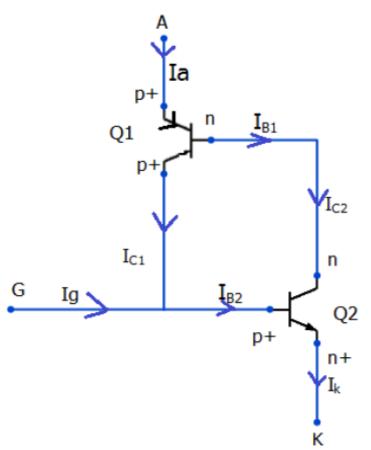

## Two transistor analogy

- The principle of thyristor operation can be explained with the use of its transistor model (or two transistor analogy)

- Two transistor model is obtained by bisecting the two middle layers along the dotted line, in tow separate halves

- Junction J1-J2 and J2-J3 can be considered to constitute pnp and npn transistors separately

8/21/2017

# Two transistor analogy

In the off state of a transistor, collector current Ic is related to emitter current IE as

$$I_c = \alpha I_E + I_{CBO}$$

- Where α is the common base current gain

- Icbo is the common base leakage current of collector base junction of a transistor

- For transistor Q1, emitter current IE= anode current Ia and Ic= collector current Ic1

- Therefore for Q1

$$I_{c1} = \alpha_1 I_a + I_{CBO1}$$

Similarly for transistor Q2

$$I_{c2} = \alpha_2 I_k + I_{CBO2}$$

The sum of two collector current is equal to the external circuit current Ia entering at anode terminal A

$$I_a = I_{c1} + I_{c2}$$

$$I_a = \alpha_1 I_a + I_{CBO1} + \alpha_2 I_k + I_{CBO2}$$

When gate current is applied the Ik=Ia+Ig, by substituting this

$$I_a = \alpha_1 I_a + I_{CBO1} + \alpha_2 (I_a + I_g) + I_{CBO2}$$

$$I_a = \frac{\alpha_{2*}I_g + I_{CBO1} + I_{CBO2}}{1 - (\alpha_1 + \alpha_2)}$$

- ullet For a silicon transistor, current gain lpha is very small at low emitter current

- With an increase in emitter current,  $\alpha$  build up rapidly

- With gate Ig=0 and with thyristor forward biased,  $(\alpha 1 + \alpha 2)$  is very small

- Under this condition forward leakage current some what more than  $I_{CBO1}+I_{CBO2}$  flows

- If by some means the emitter current of two component transistors can be increased so that  $\alpha 1 + \alpha 2$  approaches unity

- As per above equation (equation for Ia) Ia tends to become infinity, thereby turning on the device

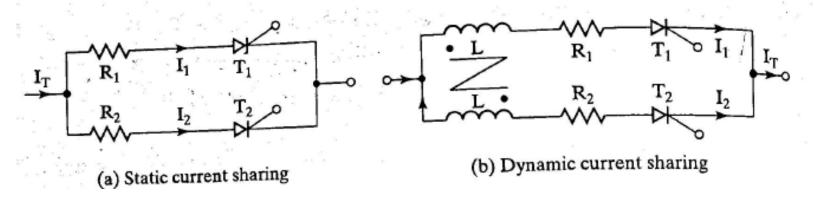

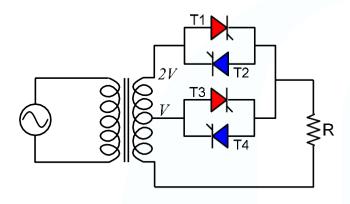

## Series and parallel connection of SCR

- For some industrial applications, the demand for voltage and current ratings is so high that a single SCR cannot fulfill such requirements

- In such cases SCRs are connected in series in order to meet the H.V demand and in parallel to meet the high current demand

- For series or parallel connected SCR it should be ensure that each SCR rating is fully utilized and the system operation is satisfactory

- String efficiency is a term that is used for measuring the degree of utilization of SCRs in a string

```

= \frac{actual\ voltage\ / current\ rating\ of\ the\ whole\ string}{[individual\ volatge\ / current\ rating\ of\ one SCR]\ [Number\ of\ SCR\ in\ a\ string\ ]}

```

- In practice this ratio is less than one

- For obtaining highest possible string efficiency, the SCRs connected in series / parallel string must have identical V-I characteristics

- As SCRs of same ratings and specifications do not have identical characteristics, unequal voltage/ current sharing is bound to occur for all SCRs in a string

- As a consequence string efficiency can never be equal to one

- However unequal voltage/ current sharing by the SCRs in a string can be minimized to a great extend by using external equalizing circuits

- Even this equalizing circuits, the efficiency is less than unity

- For a given system if one extra unit is added to the series / parallel string, the voltage / current shared by each device would become lower than its normal rating

- The use of voltage / current shared by each device would become lower than its normal rating

- The use of this extra unit will certainly improve the reliability of the string though at an increased cost

- A measure of the reliability of the string is given by a factor called DRF – derating factor

- DRF=1- string efficiency

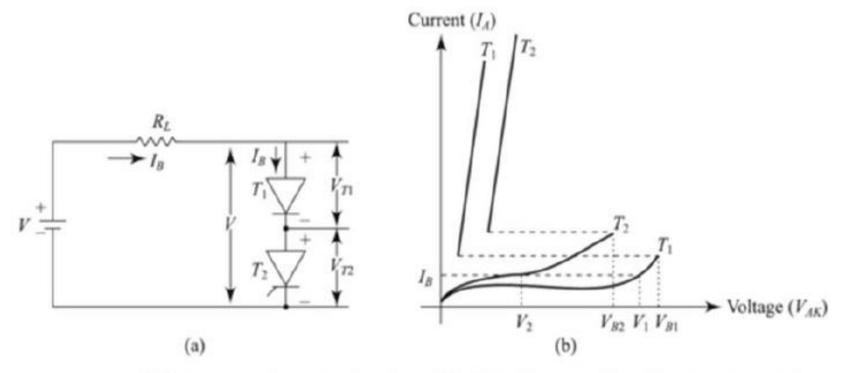

#### Series operation

(a) Series connection of thyristors  $T_1$  and  $T_2$  (b) V-I characteristics of thyristors  $T_1$  and  $T_2$

#### Series operation

- When system voltage is more than the voltage rating of a single thyristor, SCRs are connected in series in a string

- As stated before, these SCRs should have their V-I characteristics as close as possible

- Consider 2 SCR with their V-I characteristics

- For SCR1 leakage resistance is high (=V1/Io)

- For SCR2 it is low (V2/Io)

- For the same leakage current Io in the series connected SCRs, SCR1 support rated voltage whereas SCR2 support voltage V2<V1</li>

- Two SCR can support a maximum voltage of V1+V2 and not the rated blocking voltage 2V1

The string efficiency for two series connected SCRs

$$\frac{V_1 + V_2}{2V_1} = \frac{1}{2} \left( 1 + \frac{V_2}{V_1} \right)$$

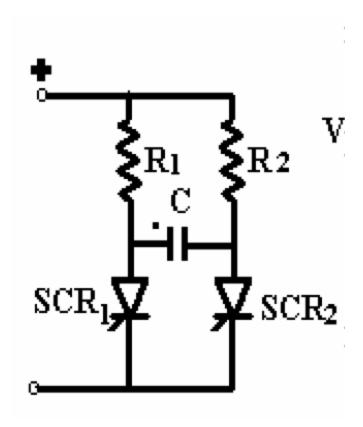

- A uniform voltage distribution in steady state can be achieved by connecting a suitable resistance across each SCR such that each parallel combination has the same resistance

- This will require different values of resistance for each SCR which is a difficult proposition

- A more practical way of obtaining a reasonably uniform voltage distribution during steady state working of series connected SCR is to connect the same value of shunt resistance R across each SCR

- This shunt resistance R is called the static equalizing circuit

- Let there be n<sub>s</sub> thyristors in the string

- The off state current of thyristor T1 be ID1 and that of other thyristor are equal such that ID2= ID3=IDn and ID1<ID2</li>

- Because thyristor T1 has the least off state current T1 shares higher voltage

- If I1 is the current through the resistor R across T1 and the current through other resistors are equal so that I2=I3=In

- The off –state current spread is

$$\Delta I_D = I_D - I_{D1} = I_T - I_2 - I_T + I_1 = I_1 - I_2 \text{ or } I_2 = I_1 - \Delta I_D$$

- The voltage across T<sub>1</sub> is V<sub>D1</sub> = R\*I1

- Using Kirchhoff's voltage law

$$V_{s} = V_{D1} + (n_{s} - 1)I_{2}R = V_{D1} + (n_{s} - 1)(I_{1} - \Delta I_{D})R$$

$$= V_{D1} + (n_{s} - 1)I_{1}R - (n_{s} - 1)R\Delta I_{D}$$

$$= n_{s}V_{D1} - (n_{s} - 1)R\Delta I_{D}$$

Solving above equation for the voltage VD1

$$V_{D1} = \frac{V_s + (n_s - 1)R\Delta I_D}{n_s}$$

A derating factor that is normally used to increase the reliability of the string is defined as the

$$DRF = 1 - \frac{V_s}{n_s V_{DS(\text{max})}}$$

#### Parallel operation

- When thyristors are connected in parallel, the load current is not shared equally due to different in their characteristics

- If a thyristor carries more current than that of the others, its power dissipation increases thereby increasing the junction temperature and decreasing the internal resistance

- This in turn increases its current sharing and may damage the thyristor

- This internal runaway may be avoided by having a common het sink, so that all units operate at same temperature

- A small resistance may be connected in series with each thyristor to force equal current sharing

- But there may be considerable power loss in the series resistance

- A common approach for the current sharing of thyristors is to use magnetically coupled inductors

- If the current through thyristor T1 increases a voltage of opposite polarity can be induced in the winding of thyristor T2 and the impedance through the path of T2 can be reduced, thereby increasing the current flow through T2

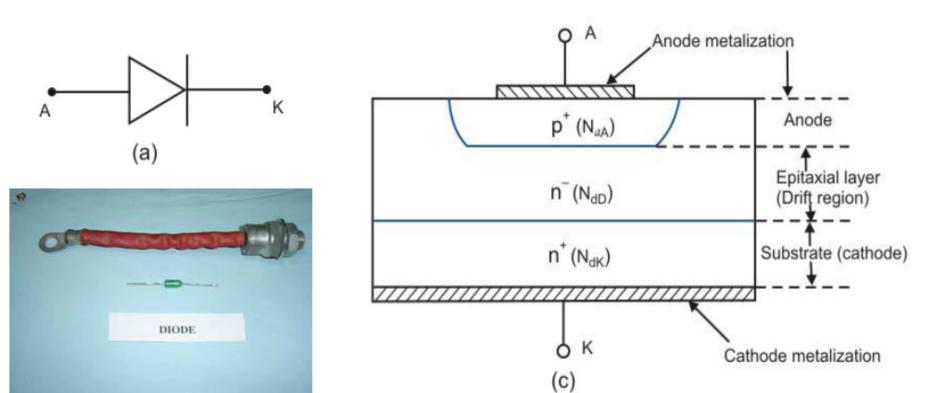

## Power semiconductor diode

- Power semiconductor diode is the "power level" counter part of the "low power signal diodes"

- These power devices, however, are required to carry up to several KA

of current under forward bias condition and block up to several KV

under reverse biased condition.

- That is the construction of power diodes arises from the need to make them suitable for high-voltage and high-current applications.

- These extreme requirements call for important structural changes in a power diode which significantly affect their operating characteristics.

- The practical realization and resulting structure of a power diode is shown

## Power semiconductor diode - structure

Circuit symbol, photograph and cross sectional view of a power diode

- It consist of heavily doped n+ substrate

- On this substrate, a lightly doped n- layer is epitexially grown

- Now a heavily doped p+ layer is diffused into n- layer to form the anode of the power diode

- This shows that n- layer is the basic structural feature not found in signal diodes

- The function of n- layer is to absorb the depletion layer of the reverse biased p+ n- junction J1

- The breakdown voltage needed in a power diode governs the thickness of n- layer

- Greater the breakdown voltage, more the n- layer thickness

- The drawback of n- layer is to add significant ohmic resistance to the diode when it is conducting a forward current

- This leads to large power dissipation in the diode

- So proper cooling arrangements in large diode ratings are essential

- Circuit symbol of a power diode is same as that of a signal diode

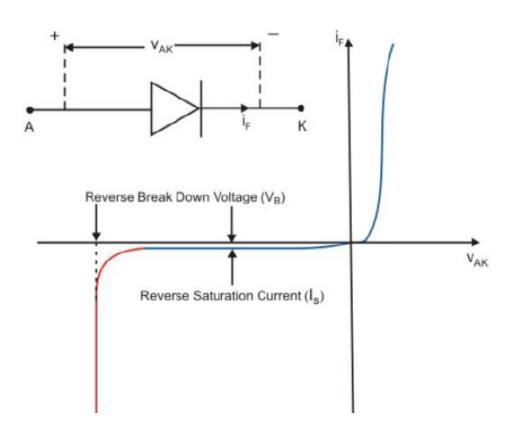

## Power semiconductor diode - Chara.

- Power diode is a two terminal, p-n semiconductor device

- The two terminals of diode are called, anode and cathode

- The two important characteristics of diode are

- 1) Diode V-I characteristics

- 2) Diode reverse recovery characteristics

#### **Diode V-I characteristics**

- When anode is positive w.r.t cathode, diode is said to be forward biased

- With increase of the source voltage Vs from zero value, initially diode current is zero

- From Vs =0 to cut in voltage, the forward diode current is very small

- Cut in voltage is also known as, threshold voltage or turn on voltage

- Beyond cut in voltage, the diode current rises rapidly and the diode is said to conduct

- For silicon diode, the cut in voltage is around 0.7 V

- When diode conducts, there is a forward voltage drop of the order of 0.8 to 1 V

- When cathode is positive w.r.t anode, the diode is said to be reverse biased

- In the reverse biased condition a small reverse current called leakage current of the order of microamperes or mill amperes flows

- The leakage current is almost independent of the magnitude of reverse voltage until this voltage reaches breakdown voltage

- At this reverse breakdown, voltage remains almost constant but reverse current becomes quite high, limited only by the external circuit resistance

- A large reverse breakdown voltage, associated with high reverse current leads to excessive power loss that may destroy the diode

- This shows that reverse breakdown of a power diode must be avoided by operating it below the specific peak reverse repetitive voltage V<sub>RRM</sub>

- For an ideal diode, the voltage drop across conducting diode is zero and VRRM is infinite

- Diode manufactures also indicate the value of peak inverse voltage (PIV) of a diode

- This is the largest reverse voltage to which a diode may be subjected during its working

- The power diodes are available with forward current rating of 1A to several thousands of ampere with reverse voltage rating of 50 V to 5000 V or more

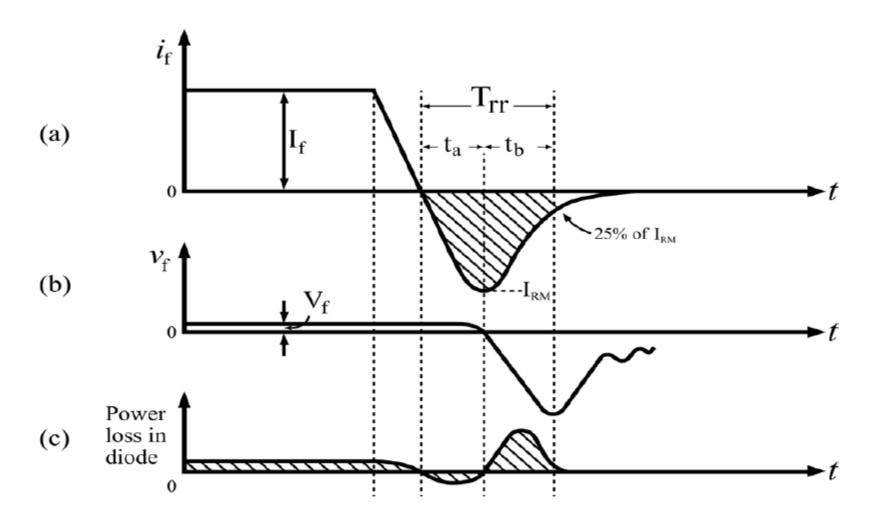

#### Diode reverse recovery characteristics

- After the forward diode current decays to zero, the diode continues to conduct in the reverse direction because of the presence of stored charges in the depletion region and the semiconductor layers

- The reverse current flows for a time called reverse recovery time trr

- The diode regain its blocking capability until reverse recovery current decays to zero

- Is defined as the time between the instant forward diode current becomes zero and the instant reverse recovery current decays to 25% of its reverse peak value Irm

Reverse recovery characteristics

- The reverse recovery time is composed of two segments time ta and tb, i.e. trr=ta+tb

- $\bullet$  Time ta is the time between zero crossing of forward current and peak reverse current  $I_{\text{RM}}$

- During ta, charge stored in depletion layer is removed

- tb- is measured from the instant of reverse peak value IRM to the instant when 0.25IRM is reached

- During tb charge from the semiconductor layer is removed

- The shaded area represent the stored charge, or reverse recovery charge QR which must be removed during the reverse recovery time trr

- The ratio tb/ta is called the softness factor or S factor

- Its usual value is unity and this indicate low oscillatory reverse recovery process

- A diode with S-factor unity is called soft-recovery diode

- And a diode with S factor <1 is called snappy recovery diode or fast recovery diode

- The peak inverse current can be expressed as

$$I_{RM} = t_a \frac{di}{dt}$$

$$Q_R = \frac{1}{2} I_{RM} t_{rr} \qquad I_{RM} = \frac{2Q_R}{t_{rr}}$$

• If trr=ta

$$I_{RM} = t_{rr} \frac{di}{dt} \qquad t_{rr} \frac{di}{dt} = \frac{2Q_R}{t_{rr}}$$

$$t_{rr} = \left[\frac{2Q_R}{\left(\frac{di}{dt}\right)}\right]^{1/2}$$

• With ta=trr, we get

$$I_{RM} = t_{rr} \frac{di}{dt} = \left[ \frac{2Q_R}{\left( \frac{di}{dt} \right)} \right]^{1/2} \cdot \frac{di}{dt}$$

$$=\left[2Q_{R}\left(\frac{di}{dt}\right)\right]^{1/2}$$

## Power semiconductor diode- Types

#### General purpose diode

- High reverse recovery time, order of 25 micro sec

- Current rating from 1A to several thousands of ampere

- Voltage rating 5V to 5kV

- Application battery charging, electric traction, electroplating, welding, UPS etc..

#### Fast-recovery diode

- Low reverse recovery time of about 5 micro sec

- Application chopper, commutation circuit, SMPS, induction heating etc...

- Current rating from 1A to several thousands of ampere

- Voltage rating 50V to 3kV

### Schottky diode

- Use metal-to-semiconductor junction for rectification

- The metal is usually aluminum

- Low cut in voltage

- Higher reverse leakage current

- Higher operating frequency

- Reverse Voltage rating 100V

- Forward current rating 1A to 300A

- Applications high frequency instrumentation, switching power supplies

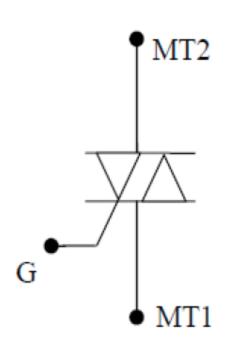

## **TRIAC**

- An SCR is a unidirectional device an it can conduct from anode to cathode only and not from cathode to anode

- ATRIAC can conduct in both the directions

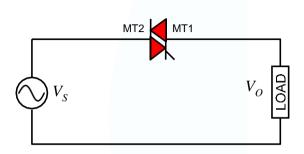

- TRIAC bidirectional thyristor with three terminals

- Extensively used for the control of power in ac circuits (residential lamp dimmers, heater control, speed control of small single phase series and IM)

- The word derived form combing the capital letters from the word TRIode and AC

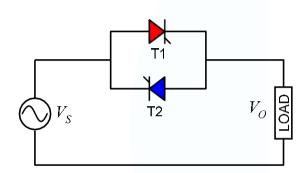

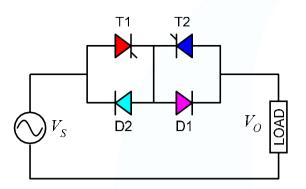

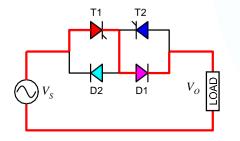

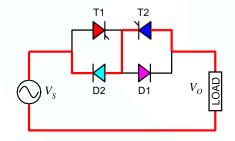

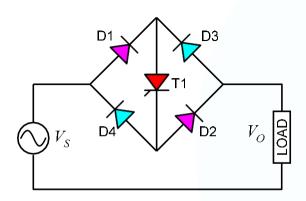

- When in operation, a TRIAC is equivalent to two SCRs connected in anti-parallel

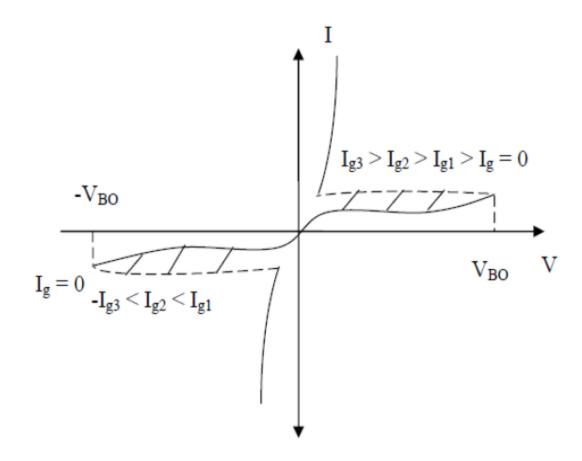

- The circuit symbol and characteristics are shown

As TRIAC can conduct in both the direction, the terms anode and cathode are not applicable to TRIAC

\[

\Psi MT

\]

Its three terminal are usually designated as

MT1 – Main Terminal 1

MT2 – Main Terminal 2

G - Gate

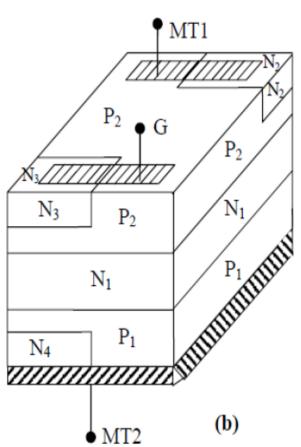

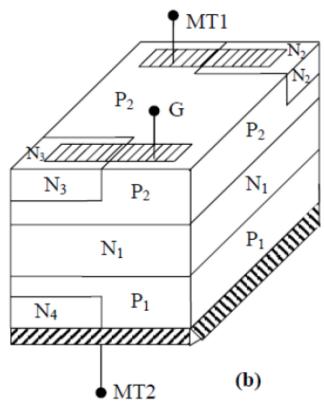

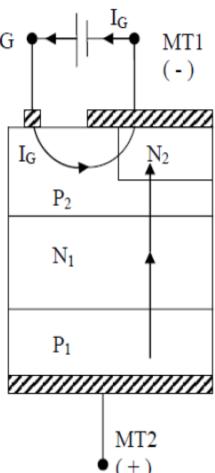

Cross sectional view of TRIAC showing all the layers and junction is shown

• The gate G is near terminal MT1

The cross hatched strip shows that G is connected to N3 as well as P2

• MT1 is connected to P2 and N2

MT2 is connected to P1 and N4

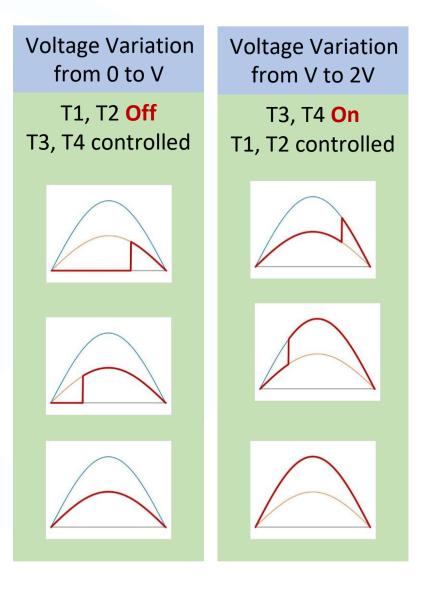

- Since TRIAC is a bidirectional device and can have its terminals at various combinations of +ve and -ve voltages, there are 4 possible electrode potential combinations as given below

- 1) MT2 is +ve w.r.t MT1, G +ve w.r.t MT1

- 2) MT2 is +ve w.r.t MT1, G -ve w.r.t MT1

- 3) MT2 is -ve w.r.t MT1, G -ve w.r.t MT1

- 4) MT2 is -ve w.r.t MT1, G +ve w.r.t MT1

- Trigeering sensitivity is highest for combination 1 & 3

- For bidirectional control and uniform gate trigger 2 & 3 used

- 4 usually avoided

### <u>Mode – 1(MT2 is +ve w.r.t MT1, G +ve w.r.t MT1)</u>

- When MT2 is +ve w.r.t MT1 junction P1N1, P2N2 are forward biased

- Junction N1P2 reverse biased

- When G is +ve w.r.t MT1gate current flows mainly through P2N2

- When gate current has injected sufficient charges into P2 layer, reverse biased junction N1P2 breaks down

- As a result TRIAC starts conducting through -P1N1P2N2

- TRIAC operates in the first quadrant

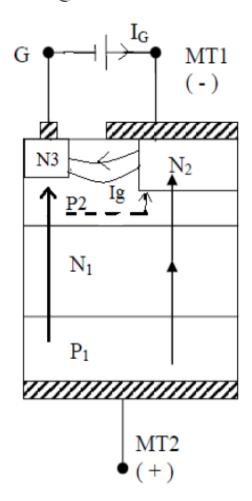

### <u>Mode – 2 (MT2 is +ve w.r.t MT1, G -ve w.r.t MT1)</u>

- When G is –ve w.r.t MT1, gate current flows through P2N3

- N1P2 forward biased

- Conduction through P1N1P2N3

- With the above conduction, voltage drop across this path falls but P2N3 rises towards MT2

- A potential gradient exist across P2

- Left hand region become higher potential than right hand region

- Current (shown in dotted line) established

- As a result right hand portion P1N1P2N2 begins to conduct

- The device structure P1N1P2N3 regarded as pilot SCR

- P1N1P2N2- main SCR

- Device with MT2 +ve and G –ve is less sensitive

- Therefore more gate current is required

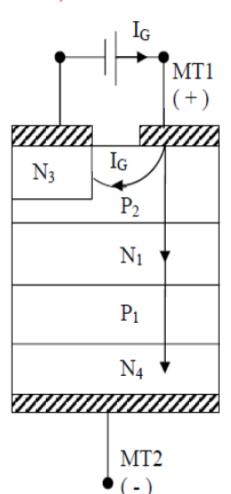

### Mode 3 (MT2 is -ve w.r.t MT1, G -ve w.r.t MT1)

- N3 act as a remote gate

- Gate current flows from P2 to N3

- Reverse biased junction N1P1 is broken

- Finally P2N1P1N4 is turned on completely

- Operation is in 3<sup>rd</sup> quadrant

- Device is more sensitive under this condition

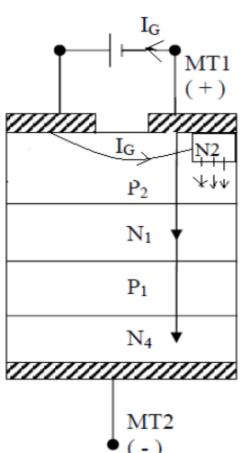

#### Mode 4 (MT2 is -ve w.r.t MT1, G +ve w.r.t MT1)

- Gate current forward biases junction P2N2

- N2 inject electrons into P2 layer (shown by dotted arrows)

- As a result reverse biased junction

N1P1 breaks down

- The structure P2N1P1N4 is completely turned on

- Current after turn on is limited by external load

- Device is less sensitive

- Operation is in 3<sup>rd</sup> quadrant

# GTO (Gate Turn Off thyristor)

- Conventional thyristor (CTs) are nearly ideal switches for their use in power electronic application

- These can be easily turned on by positive gate current

- Once in the on state, gate loses control

- CTs can now be turned off by expensive and bulky commutation circuitry

- This shortcoming of thyristors limit their use up to about 1KHz applications

- These drawbacks in thyristors has led to the development of GTOs

- GTO is a more versatile power semiconductor device

- Like a CT but with added features in it

- Can be easily turned off by a —ve gate pulse of appropriate amplitude

- GTO pnpn device that can be turned on by a +ve gate current and turned off by a –ve gate current at its gate cathode terminal

- Self turn off capability of GTO makes it the most suitable device for inverter and chopper circuit

- pn pn three terminal device with Anode (A) cathode (K) and gate (G)

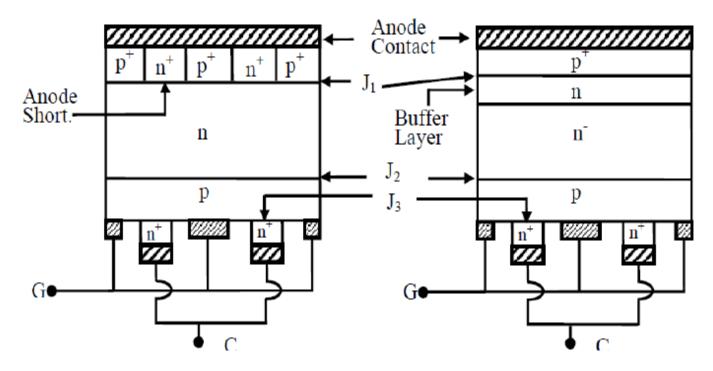

- Four layers are -p+np+n+

- Anode is made up of n+ type diffused into p+ layer

anode shorted GTO and buffer layer GTO structure shown

below

EE 305 Power Electronic

## GTO - Turn on process

- Turned on by applying a +ve gate current

- As GTO is forward biased, regeneration process starts as in a CT

- Current gains, α1, α2 begins to rise

- When  $\alpha 1 + \alpha 2 = 1$ , saturation level is reached and GTO is turned on

- The anode current Ia is then limited by load impedance

# GTO - Turn off process

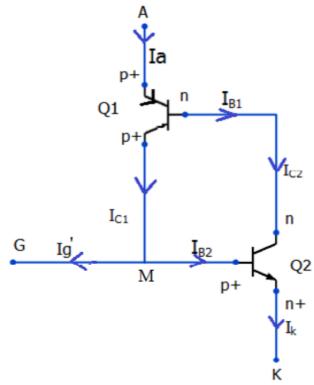

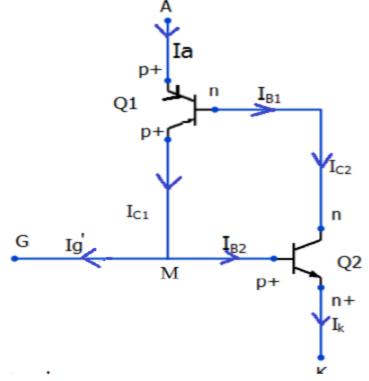

- Two transistor model is analyzed for understanding the turn off process in a GTO

- $Ic2 = \beta_2 . IB_2$

- Ic1 =  $\beta_1$  . IB1

- $Ic1 = \alpha 1 . IE1$

- $Ic2 = \alpha 2 . IE2$

- As stated above, for initiating the turn off process in GTO a —ve gate current is applied across gate cathode terminal

Now KCL at node M gives,

$$I_{C1}-I_{g'}-I_{B2}=0$$

$$I_{B2}=I_{C1}-I_{g'}=\alpha_1$$

.  $I_{a}-I_{g'}$

$$Ia = Ic_1 + Ic_2$$

$$I_{C_2}=I_{a-}I_{C_1}=(1-\alpha_1)$$

. Ia

• When saturation in Q2 has occurred  $I_{B2}=(I_C2/\beta_2)$

• This can be accomplished only if IB2 is made less than Ic2/ $\beta$ 2

- When  $I_{B2} < (I_{C2}/\beta_2)$ , Q2 would shift to active region and regenerative action would eventually turn off the GTO

- The turn off gain is defined as the ratio of anode current Ia to gate current Ig' needed to turn off the GTO

- Turn off gain  $\beta_{\text{off}} = I_a / I_g' = \alpha_2 / (\alpha_1 + \alpha_2 1)$

### Turn off action of GTO

- Ia=Ik and Ig' more than Ik

- When —ve gate current Ig' flows between gate cathode terminals net base current (IB2- Ig') is reversed

- Excess carriers are drawn from base p+ region of Q2 and collector current IC1 of Q1 is diverted into the external gate circuit

- This remove base drive of transistor Q2

- This further removes base current I<sub>B1</sub> of transistor Q1

- And the GTO is eventually turned off

• Low value of negative gate current requires, low value of  $\alpha_1$  and high value of  $\alpha_2$

EE 305 Power Electronics

# <u>Applications of GTO</u>

- High performance drive system such as field oriented control scheme used in rolling mills, robotics and machine tools

- Traction purpose because of their lighter weight

- Adjustable frequency inverter drives

- at present GTO with ratings up to 5000 V and 3000 A are available

# <u>IGBT</u>

- Developed by combining the best qualities of both BJT and MOSFET

- Thus an IGBT posses high input impedance like MOSFET and has low on state power loss as in BJT

- Free from secondary breakdown problem

- Also known as

Metal Oxide Insulated Gate Transistor (MOSIGT)

Conductively Modulated Field Effect Transistor (COMFET)

Gain Modulated FET (GEMFET)

Insulted Gate Transistor (IGT)

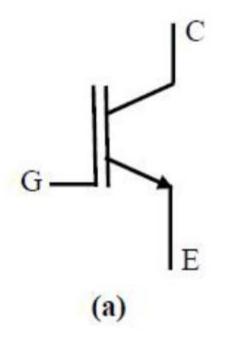

#### Circuit symbol of an IGBT.

- (a) Circuit symbol.

- (b) Photograph.

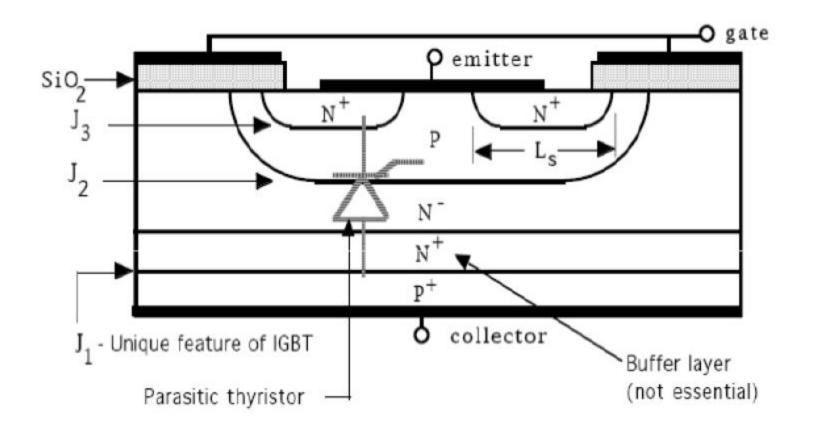

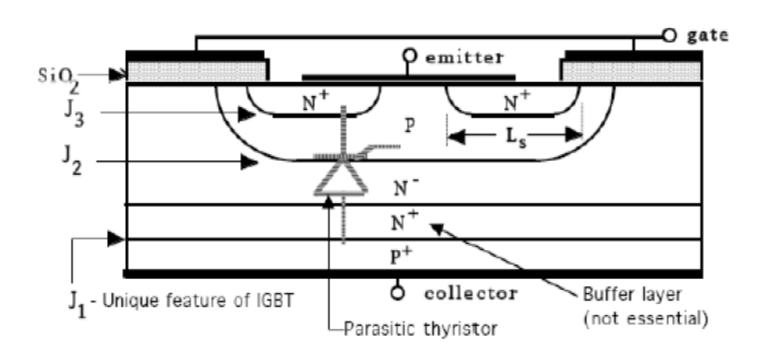

#### Basic structure of an IGBT

- Body region and emitter is shorted to minimize possible turn on of the thyristor.

- n+ buffer layer is between P+ and n- drift layer, is not essential for the operation of the IGBT.

- (IGBT with buffer layer is called punch- through type, PT-IGBT's and without buffer layer is called non-punch through type, NPT- IGBT's )

- Buffer layer improves the operation of IGBT.

### Blocking state operation

### **Blocking (Off) State Operation of IGBT**

Blocking state operation - V<sub>GE</sub> < V<sub>GE(th)</sub>

- Applied Collector emitter voltage is dropped across junction J2 and only very small leakage current flows.

- Depletion region of the J2 junction extends principally into the n- drift region ( since P type body region is more doped than n- drift region)

- Thickness of drift region is large enough to accommodate depletion layer so that depletion layer boundary does not touch P+ layer. So it can block reverse voltage ( magnitude same as forward voltage)

- This type of IGBT is known as symmetrical IGBT or nonpunch through IGBT.

- This reverse voltage blocking capability is useful in some ac circuit applications.

- If thickness of drift region is reduced, depletion layer may touch P+. To avoid that we keep a buffer layer, n+ layer.

- This type of structure is called anti symmetric or punch through IGBT.

- Shorter drift region means lower on-state losses.

- Presence of buffer layer reverse voltage capability quite low.

#### On state operation

- Gate emitter voltage increases to more than threshold value, an inversion layer is formed beneath the gate of IGBT.

- This inversion layer shorts the n- drift region to the n+ source region exactly as in the MOSFET.

- An electron current flows through this inversion layer which in turn causes substantial hole injection from the P+ drain contact layer in to n- drift region as shown in figure.

- The injected holes move across the drift region by both drift and diffusion, taking a variety of path, and reach the p type body region that surrounds the n+ source region.

As soon as the holes are in the p type body region, their space charge attracts electrons from the emitter metallization that contacts the body region, and the excess holes are quickly recombined.

## Comparison of IGBT with MOSFET

#### **IGBT**

- Three terminal called, gate, emitter and collector

- High input impedance

- Voltage controlled device

- Can designed for higher voltage rating than PMOSFET

#### MOSFET

- Three terminal called, gate, source and drain

- High input impedance

- Voltage controlled device

- On state voltage drop and losses rises rapidly than IGBT with rise in temperature

## Comparison between GTO and Thyristor

#### Disadvantages

- Magnitude of latching and holding current is more

- On state voltage drop and associated loss is more

- Triggering gate current required is high

- Gate drive circuit losses are more

- Reverse voltage locking capability is less than forward voltage blocking capability

#### Advantages

- Faster switching speed

- Surge current capability is comparable with an SCR

- More di/dt rating at turn on

- GTO circuit configuration has low size and weight

- Higher efficiency

- Reduced acoustical and electromagnetic noise due to elimination of commutation chokes

### Power MOSFET - Comparison with BJT

#### **BJT**

- Bipolar

- Input impedance low

- Higher switching losses

- Current controlled device

- -ve temperature coefficient

- Hot spot and secondary breakdown occur in BJT

- Available with rating up to 1200 V, 800 A

#### **MOSFET**

- Uni-polar device

- High input impedance

- Lower switching losses and conduction losses

- voltage controlled device

- +ve temperature coefficient

- Secondary breakdown does not occur

- High voltage rating, more conduction loss

- 500 V, 140 A

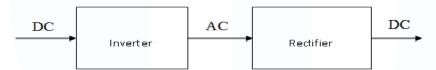

| CONVERSION<br>FROM/TO | NAME                                              | FUNCTION                                                              | SYMBOL |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------|--------|

| DC to DC              | Chopper                                           | Constant to variable DC or<br>variable to constant DC                 |        |

| DC to AC              | Inverter                                          | DC to AC of desired voltage and frequency                             | ~      |

| AC to DC              | Rectifier                                         | AC to unipolar (DC) current                                           | ~      |

| AC to AC              | Cycloconverter,<br>AC-PAC,<br>Matrix<br>converter | AC of desired frequency and/or<br>magnitude from generally line<br>AC | ~_~    |

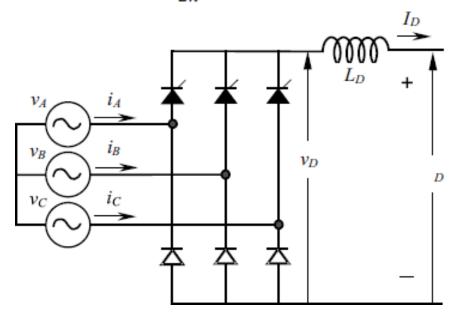

## MODULE- II

Gate triggering circuits – R, RC, UJT triggering circuits – natural and forced commutation (concept only). Requirements of isolation and synchronization in gate drive circuits- Opto and pulse transformer based isolation.

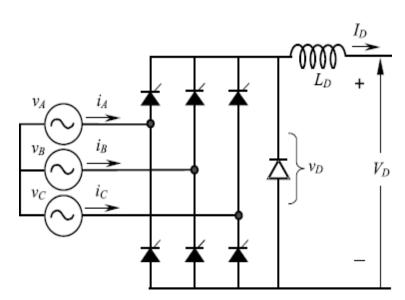

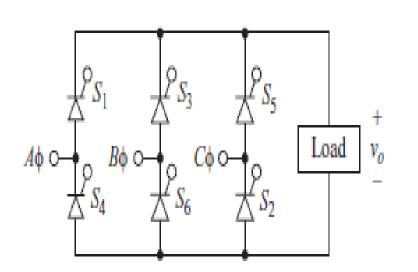

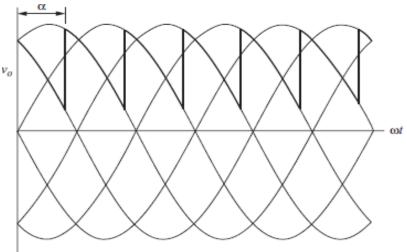

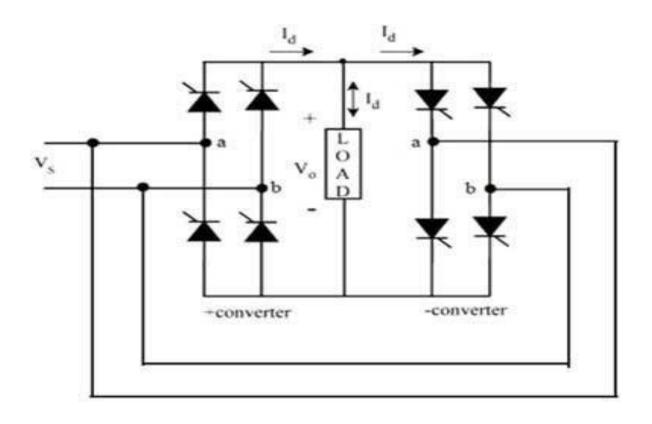

Controlled rectifiers – half-wave controlled rectifier with R load – 1-phase fully controlled bridge rectifier with R, RL and RLE loads (continuous & discontinuous conduction) – output voltage equation – 1- phase half controlled bridge rectifier with R, RL and RLE loads – displacement power factor – distortion factor.

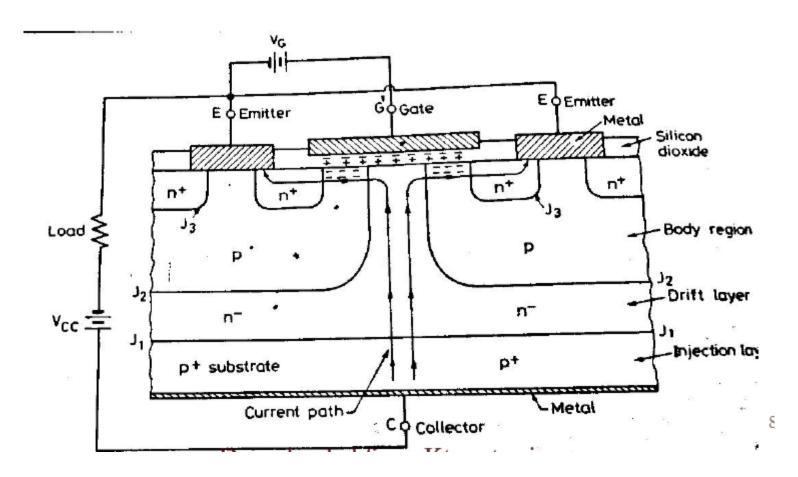

## Gate triggering circuits

- An SCR can be switched from off-state to on-state in several ways

- Forward voltage triggering

- dv/dt triggering

- Temperature triggering

- Light triggering

- Gate triggering

- The instant of turning on the SCR cannot be controlled by first three methods

- Light triggering used in some applications especially in series connected string

- Gate triggering most common method, efficient and reliable

## Main features of firing circuits

- Gate control circuit is also called firing or triggering circuit

- Gate circuits are usually low power electronics circuits

## Main features of firing circuits

- A firing circuit should fulfill the following two functions

- ❖ If power circuit has more than one SCR, the firing circuit should produce gating pulses for each SCR at the desired instant for proper operation of the power circuit

- The control signal generated by a firing circuit may not be able to turn on an SCR. It is therefore common to feed the voltage pulse to a driver circuit and then to a gate cathode circuit

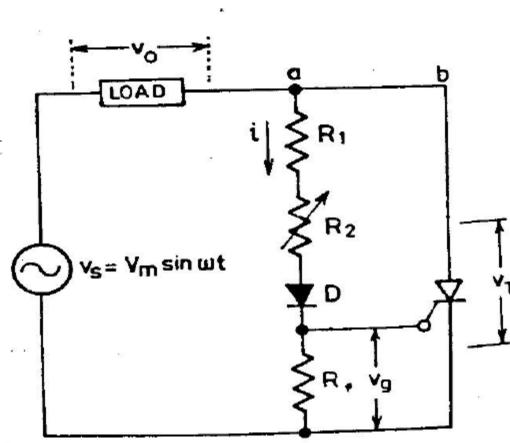

## R triggering circuit (Resistance triggering)

- Simplest and most economical

- Suffer from a limited range of firing angle control (0 to 90°)

- R2 variable resistance

- R stabilizing resistance

- In case R2=0, gate current may flow from source, trough load, R1, D and gate to cathode

# R triggering circuit (Resistance triggering)

- This current should not exceed maximum permissible gate current Igm

- R1 therefore found from the relation

$$\frac{V_m}{R_1} \le I_{gm} \qquad or \ R_1 \ge \frac{V_m}{I_{gm}}$$

- Function of R1 is to limit the gate current to a safe value as R2 is varied

- Resistance R should have a value such that maximum voltage drop across it does not exceed maximum possible gate voltage Vgm

- This can happen only when R2 is zero

- Under this condition

$$\frac{V_m}{R_1 + R} \cdot R \le V_{gm}$$

- As resistance R1, R2 are large, gate trigger circuit draws a small current

- Diode D allows the flow of current during positive half cycle only

- The amplitude of this dc pulse can be controlled by varying R2

- The potentiometer setting R2 determines the gate voltage amplitude

- When R2 is large current i is small and the voltage across R,vg=i.R is also small

- As Vgp is less than Vgt, SCR will not turn on

- Therefore load voltage vo=0, io=0 and supply voltage appear across SCR

- Trigger circuit consist of resistance only, therefore vg is in phase with source voltage vs

- R2 is adjusted such that Vgp=Vgt, this gives the value of firing angle as 90

## R triggering circuit (Resistance triggering)

- The same circuit also is applicable for TRIAC.

- However, diode D1 has to be removed such that a trigger signal will be available at the gate terminal during both halfcycles.

- Because the gate of a TRIAC is not equally sensitive in all four of its modes of switching, α and hence vo are usually different in the positive and negative half-cycles of the supply voltage.

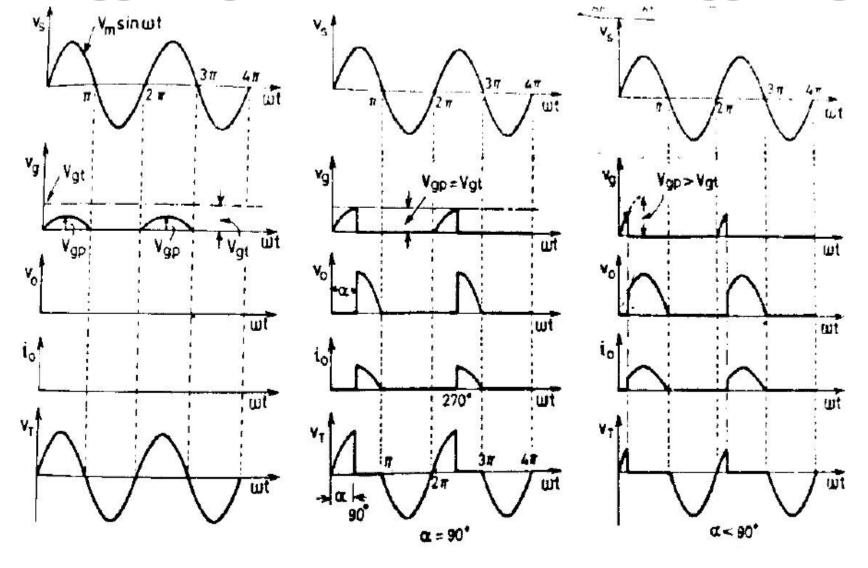

## RC triggering circuit

- The limited range of firing angle control by resistance firing circuit can be overcome by RC firing circuit

- Several variations of RC trigger circuits are available

- In these cases the range of  $\alpha$  is extendable beyond 90.

#### RC half wave triggering circuit

- By varying the value R, firing angle can be controlled from 0 to 180

- In the –ve half cycle capacitor C charges through D2 with lower plate +ve to the peak supply voltage Vm at  $\omega t$ =-90

- After ωt=-90, source voltage Vs decreasing from –Vm at ωt=-90 to zero at ωt=0

- During this period capacitor voltage may fall from -Vm to some small value -oa

- Now the charging of the capacitor (with upper plate positive) takes place through R and the charging rate depends on the time-period RC.

- When capacitor charges to +ve voltage equal to VGT, conduction of the SCR takes place.

- After this capacitor holds a small +ve voltage

- Diode D1 used to prevent the breakdown of cathode to gate junction through D2 during the —ve cycle

• where the angular frequency of ac mains  $\omega t = 2\pi/T$ .

$$RC \ge \frac{1.3\ T}{2} = \frac{4}{\omega}$$

The value of R is chosen such that the required Igt and Vgt are supplied to the gate terminal:

$$R \le \frac{V_s - V_{gt} - v_d}{I_{gt}}$$

Where v is the voltage at the switching instant of thyristor and v<sub>D</sub> is forward voltage drop of diode D1

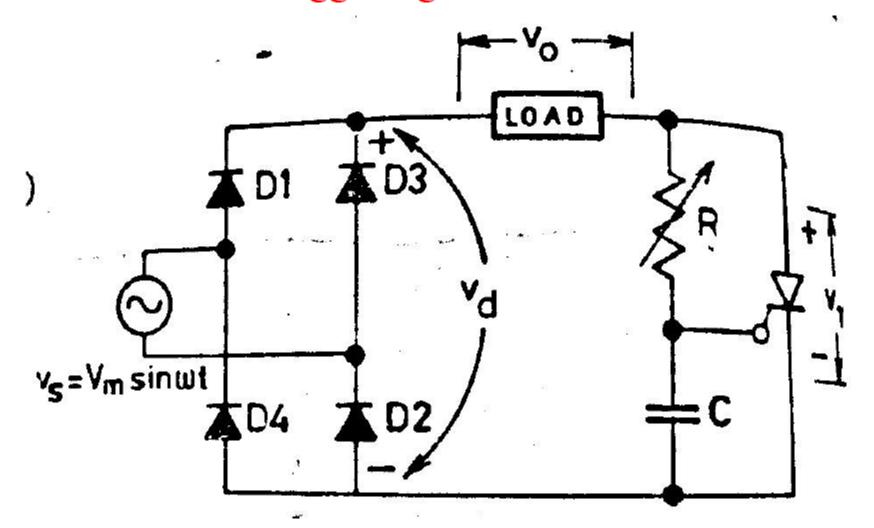

### RC Full wave triggering circuit

- Diode D1-D4 form a full wave diode bridge

- When capacitor charges to a voltage equal to Vgt, SCR triggers and rectified voltage Vd appears across load as Vo

- The value of RC can be calculated by

$$RC \geq 50.\frac{T}{2} = \frac{157}{\omega}$$

R is given by

$$R \ll \frac{V_s - V_{gt}}{I_{gt}}$$

## **UJT triggering circuit**

- Resistance and RC triggering circuits described above gives prolonged pulses

- As a result power dissipation in the gate circuit is large

- At the same time, R and RC triggering circuits cannot be used for automatic or feedback control system

- These difficulties can be overcome by use of UJT triggering circuits

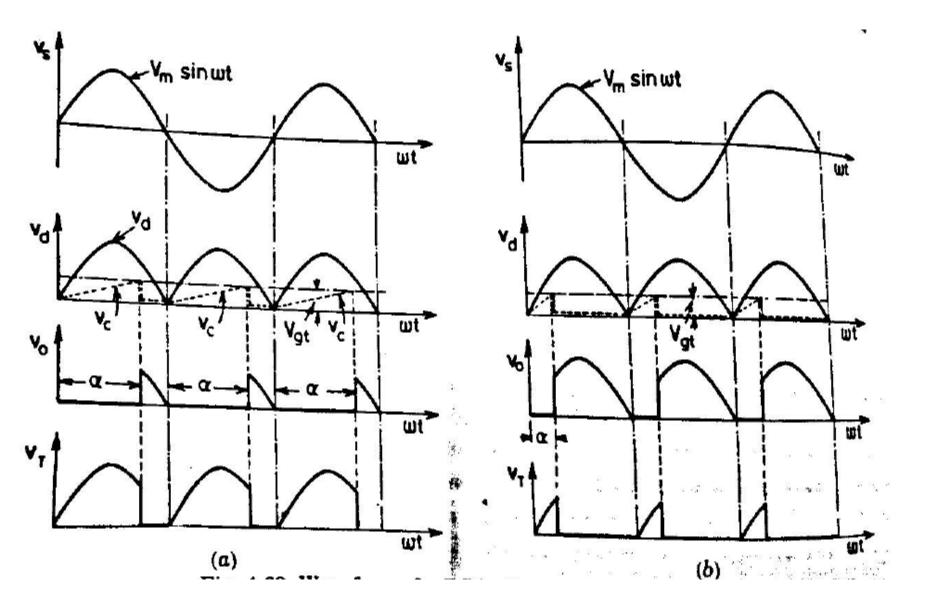

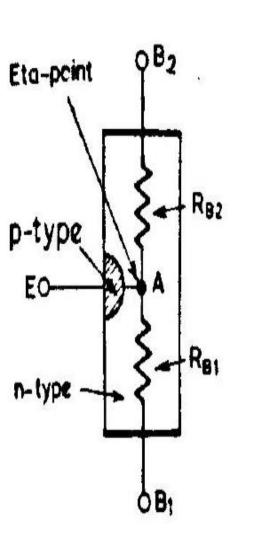

- An UJT is made up of an n-type silicon base to which p-type emitter is embedded

- The n-type base is slightly doped whereas p-type is heavily doped

B2

- The two ohmic contacts provided at each end are called base-one B1 and base-two B2

- So an UJT is a three terminal device emitter, base one and base two

- The emitter terminal divides the inter base resistance (VBB) into two parts (say, RB1 and RB2).

- If a dc biasing voltage (VBB) is applied across the base terminals, the voltage in N-type material near emitter terminal (k) is given by  $R_{R1}$

$V\eta = \frac{R_{B1}}{R_{B1} + R_{B2}} = \eta V_{BB}$

• where  $\eta$  is called the intrinsic-standoff ratio of UJT and its value is less than unity (typical value varies between 0.5 and 0.85).

- The UJT is highly efficient switch; its switching time is in the range of nanoseconds

- Since UJT exhibit negative resistance characteristics, it can be used as a relaxation oscillator

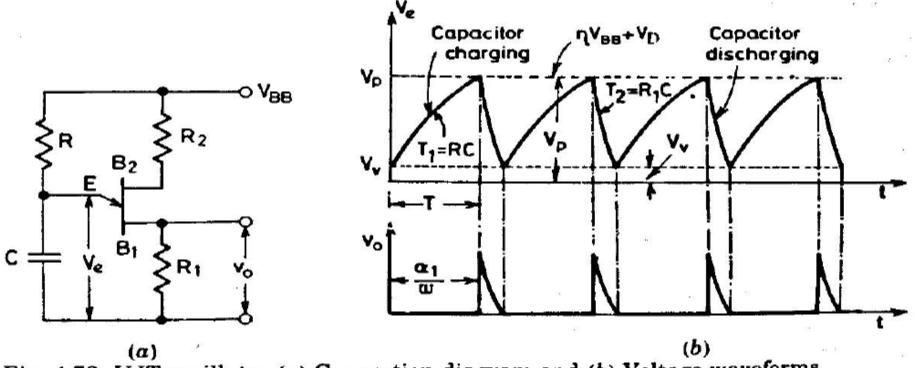

Fig. 4.72. UJT oscillator (a) Connection diagram and (b) Voltage waveforms.

- The external resistance R1 and R2 are small in comparison with the internal resistances RB1 and RB2

- The charging resistance R should be such that its load line intersect the device characteristics only in the —ve resistance region

- When source voltage VBB is applied, capacitor C begins to charge through R exponentially towards VBB

- The time constant of the charge circuit is

$$\tau_1 = RC$$

When this emitter voltage reaches peak-point voltage Vp, the uni-junction between E-B1 breaks down  As a result, UJT turns on and capacitor C rapidly discharges through low resistance R1 with a time constant

$$\tau_2 = R_1 C$$

- When emitter voltage decays to the valley-point voltage Vv, emitter current falls below Iv and UJT turns off

- The time T required for the capacitor C to charge from initial voltage Vv to peak-point voltage Vp through large resistance R can be obtained as

$$V_p = \eta V_{BB} + V_D = V_v + V_{BB} (1 - e^{-T/RC})$$

$$V_D = V_v, \eta = (1 - e^{-T/RC})$$

$$T = \frac{1}{f} = RC \ln \left( \frac{1}{1 - \eta} \right)$$

- The charging of the capacitor starts from each zero crossover instant only.

- The first pulse in each half-cycle that triggers the thyristor is synchronized with v, and therefore α becomes equal in each cycle.

- By controlling R, the time period of oscillator  $(\tau)$ , or the delay period of the first pulse  $(\tau)$ ,  $\alpha$  can be adjusted.

- The UJT trigger circuit may also be energized from a separate transformer (for biasing) and the same performance can be achieved.

## Natural and forced commutation

- A thyristor can be turned ON by applying a positive voltage of about a volt or a current of a few tens of milliamps at the gatecathode terminals.

- However, the amplifying gain of this regenerative device being in the order of the 10<sup>8</sup>, the SCR cannot be turned OFF via the gate terminal.

- It will turn-off only after the anode current is annulled either naturally or using forced commutation techniques.

- These methods of turn-off do not refer to those cases where the anode current is gradually reduced below Holding Current level manually or through a slow process.

- Once the SCR is turned ON, it remains ON even after removal of the gate signal, as long as a minimum current, the Holding Current, Ih, is maintained in the main or rectifier circuit.

## Natural and forced commutation

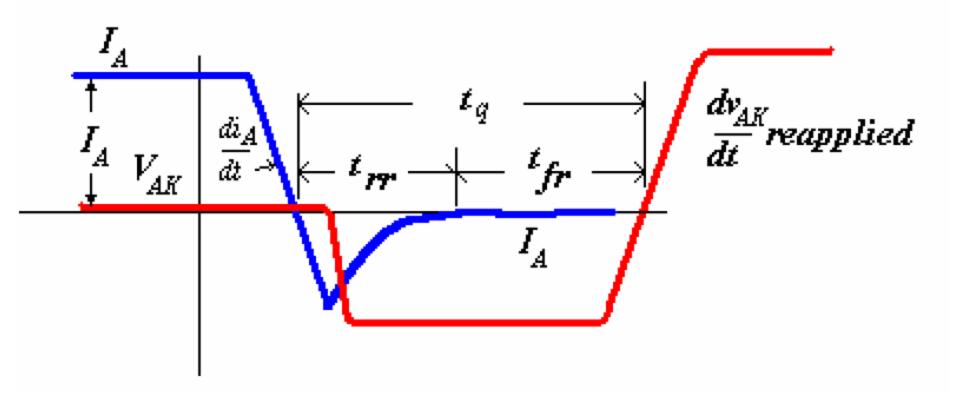

Turn off dynamics of SCR

- In all practical cases, a negative current flows through the device.

- This current returns to zero only after the reverse recovery time trr, when the SCR is said to have regained its reverse blocking capability.

- The device can block a forward voltage only after a further tfr, the forward recovery time has elapsed.

- Consequently, the SCR must continue to be reverse-biased for a minimum of tfr + trr = tq, the rated turn-off time of the device.

- The external circuit must therefore reverse bias the SCR for a time toff > tq. Subsequently, the reapplied forward biasing voltage must rise at a dv/dt < dv/dt (reapplied) rated.</li>

- SCRs have turn-off times rated between 8 50  $\mu$ secs.

- The faster ones are popularly known as 'Inverter grade' and the slower ones as 'Converter grade' SCRs.

- The latter are available at higher current levels while the faster ones are expectedly costlier

The six distinct classes by which the SCR can be turned off are:

- Class A Self commutated by a resonating load

- Class B Self commutated by an L-C circuit

- Class C C or L-C switched by another load carrying SCR

- Class D C or L-C switched by an auxiliary SCR

- Class E An external pulse source for commutation

- Class F AC line commutation

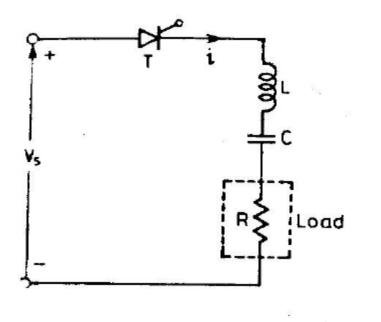

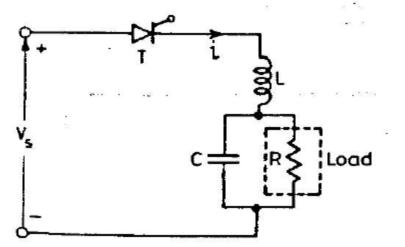

## **Class A Commutation:**

## **Load commutation**

(b)

(a)

- R is load resistance

- For low values of R, R, L and C can be connected in series

- For high values of R E and R are connected in parallel

- Essential requirement for both the circuit overall circuit must be under-damped

- When energized from dc source, current builds up like sinusoidal wave form

- Current first rises to maximum value and then decreases

- When current decays to zero and tends to reverse, SCR T is turned off

- Possible only in dc circuit

- Also called resonant commutation, self commutation or load commutation

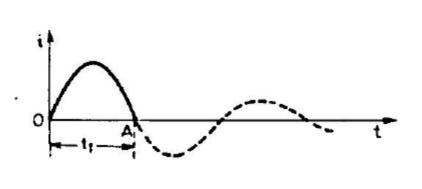

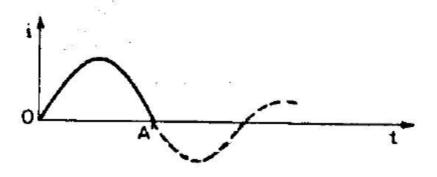

## Class B: Resonant pulse commutation

- Source voltage Vs charges capacitor C to voltage Vs with left hand plate +ve

- Main thyristor as well as auxiliary thyristor are off

- When T1 is turned on at t=0, constant current Io is is established in the load circuit

- Up till time t1; ic=0, vc=Vs,io=Io iT1=Io

- For initiating the commutation of main thyristor T1, auxiliary thyristor TA is gated at t=t1

- With TA on, a resonant current ic begins to flow from C through TA, L and back to C

$$i_c = -V_s \sqrt{\frac{C}{L}} \sin \omega_0 t$$

- -ve sign is due to the fact that, this current flows opposite to the reference +ve direction chosen for ic

- At t1; ic=0, vc=-Vs and iT1=Io

- Just after t2, ic tends to reverse, TA is turned off at t2

- With vc=-Vs, right hand plate has +ve polarity

- Resonant current ic now builds up through C, L, D and T1

- As this current ic grows opposite to forward thyristor current of T1, net forward current iT1=Io-ic begins to decrease

- Finally when ic in the reversed direction attains the value Io, forward current in T1 is reduced to zero and the device T1 is turned off at t3

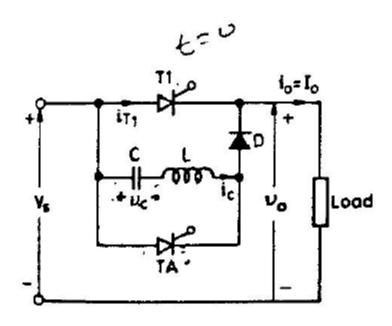

### Class C, C or L-C switched by another load-carrying SCR

- This configuration has two SCRs.

- One of them may be the main SCR and the other auxiliary.

- Both may be load current carrying main SCRs.

- The configuration may have four SCRs with the load across the capacitor, with the integral converter supplied from a current source.

- Assume SCR<sup>2</sup> is conducting. C then charges up in the polarity shown.

- When SCR<sup>1</sup> is triggered, C is switched across SCR<sup>2</sup> via SCR<sup>1</sup> and the discharge current of C opposes the flow of load current in SCR<sup>2</sup>.

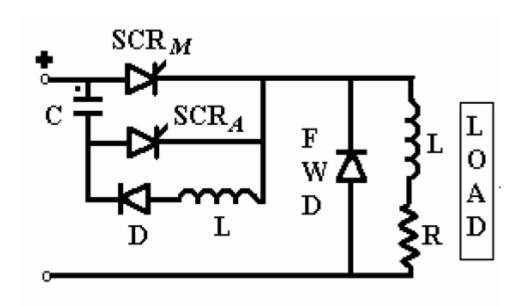

### Class D, L-C or C switched by an auxiliary SCR

- Class C can be converted to Class D if the load current is carried by only one of the SCR's, the other acting as an auxiliary turn-off SCR.

- The auxiliary SCR would have a resistor in its anode lead of say ten times the load resistance.

- SCRA must be triggered first in order to charge the upper terminal of the capacitor as positive.

- As soon as C is charged to the supply voltage, SCRA will turn off.

- If there is substantial inductance in the input lines, the capacitor may charge to voltages in excess of the supply voltage.

- This extra voltage would discharge through the diode-inductorload circuit.

- When SCRM is triggered the current flows in two paths: Load current flows through the load and the commutating current flows through C- SCRM -L-D network.

- The charge on C is reversed and held at that level by the diode D.

- When SCRA is re-triggered, the voltage across C appears across SCRM via SCRA and SCRM is turned off.

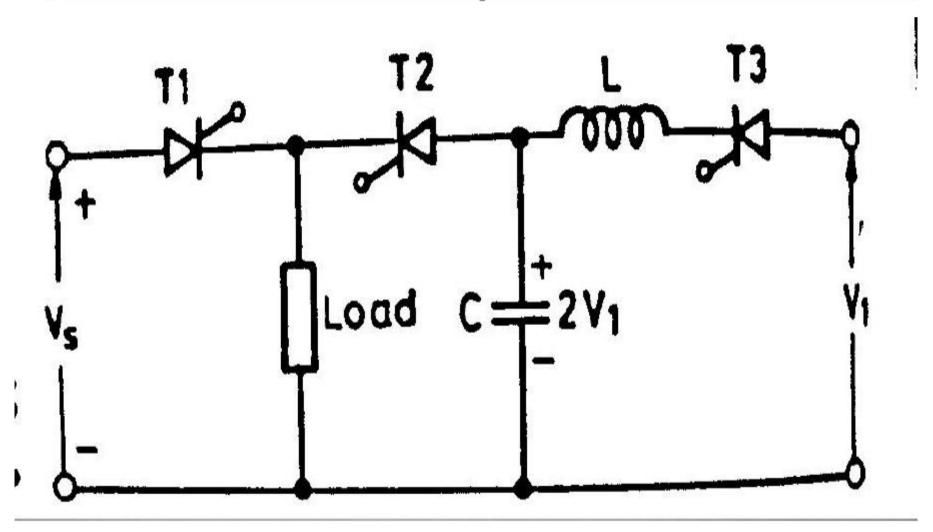

#### Class E - External pulse commutation

- A pulse of current is obtained from a separate voltage source to turn off the conducting SCR

- The peak value of the current pulse must be more than the load current

- Vs is the voltage of main source and V1 is the voltage of auxiliary supply

- Thyristor T1 is conducting and load is connected to Vs

- When T3 is turned on, V1, T3, L and C form an auxiliary circuit

- Therefore C is charged to a voltage +2V1and auxiliary current falls to zero T3 gets commutated

- For turning off T1, T2 is turned on

- With T2 on, T1 is subjected to a reverse voltage, Vs-2V1 and T1 is therefore turned off

- After T1 turned off, capacitor discharges through load

### Class F: Line commutation

- Can occur only when source is ac

- When SCR is energized from ac source, current has to pass through its natural zero at the end of every +ve half cycle

- Then ac source apply a reverse voltage across SCR automatically

- As a result SCR turned off

- This is called natural commutation, because no external circuit is employed to turn off the thyristor

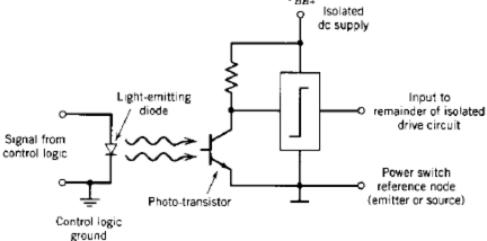

#### **Optocouplers**

- Consist of a light emitting diode (LED), the output transistor and a built in schmitt trigger

- A +ve signal from the control logic causes the LED to emit light that is focused on the optically sensitive base region of a photo transistor  $v_{BB*}$

- The light falling on the base region generate a significant number of electron hole pair in the base region that causes the photo transistor to turn on

- The resulting drop in voltage at the photo transistor collector causes the schmitt trigger to change state

- The output of the schmitt trigger is the optocoupler output and can be used as the control input to the isolated drive circuit

- The capacitance between LED and the base of the receiving transistor within the optocoupler should be as small as possible to avoid retriggering at both turn on and turn off of the power transistor due to the jump in the potential between the power transistor emitter reference point and the ground of the control electronics

- To reduce this problem optocouplers with electrical shield between the LED and the receiver transistor should be used

- As an alternative, fiber optic cables can be used to completely eliminate this retriggering problem and to provide very high electrical isolation and creepage distance

- When using fiber optic cables, the LED is kept on the printed circuit board of the control electronics, and the optical fiber transmits the signal to the receiver transistor which is put on the drive circuit printed circuit board

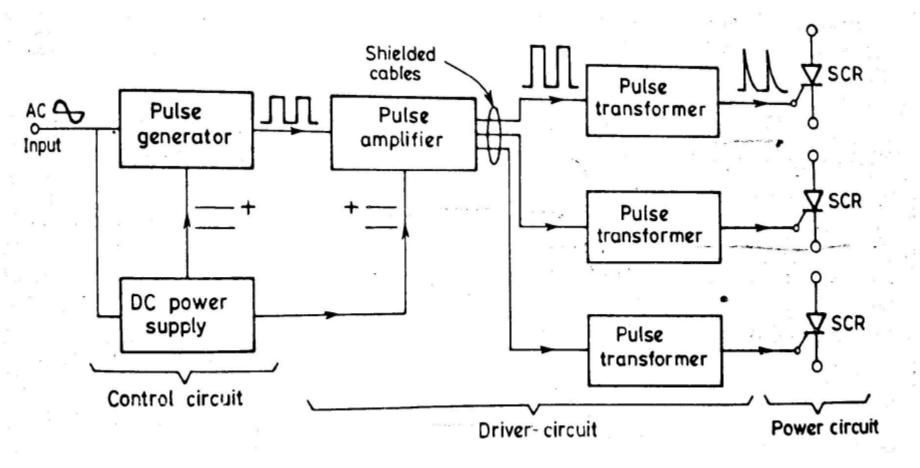

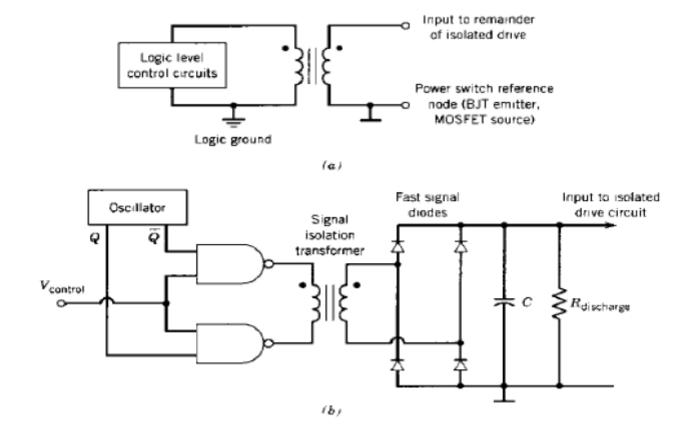

#### Pulse transformer

Instead of using optocouplers or fiber optic cables, the control signal can be coupled to the electrically isolated drive circuit by means of a transformer

- If the switching frequency is high and the duty ratio D varies only slightly around 0.5, a baseband control signal of appropriate magnitude can be applied directly to the primary of a relatively small and light weight pulse transformer as in (a)

- And the secondary output can be used to either directly drive the power switch or used as the input to an isolated drive circuit

- As the switching frequency is decreased below the tens of kilohertz range, a baseband control signal directly applied to the transformer primary becomes impractical because the size and weight of the transformer becomes increasingly larger

- Modulation of a high frequency carrier by a low frequency control signal enables a small high frequency pulse transformer to be used for even low frequency control signal

- In fig.b. the control signal modulates a high frequency oscillator output before being applied to the primary of a high frequency signal transformer

- Since a high frequency transformer can be made quite small, it is easy to avoid stray capacitance between the input and output winding and the transformer will be inexpensive

- The transformer secondary output is rectified and filtered and then applied to the comparator and the rest of the isolated drive circuit

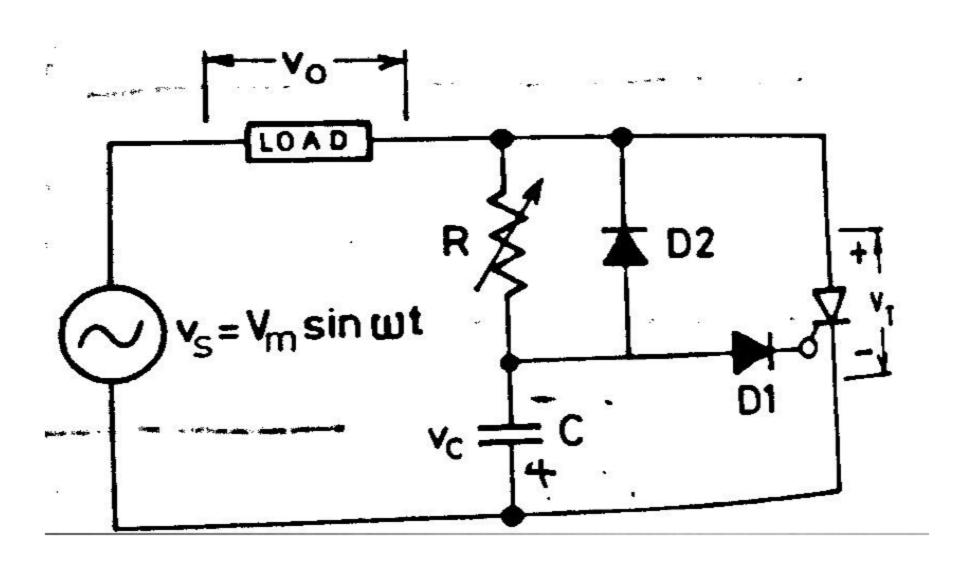

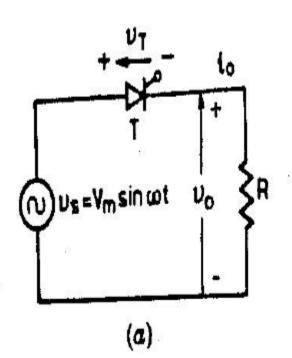

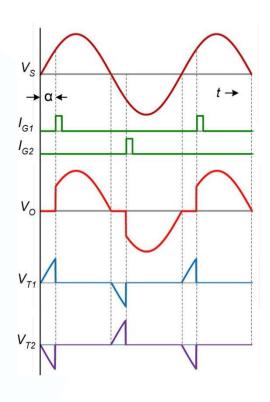

### <u>Controlled rectifiers –</u> <u>Principles of phase control</u>

- the firing angle may defined as the angle between the instant thyristor would conduct if it were a diode and the instant it is triggered

- Is measured form the angle that gives the largest average output voltage or the highest load voltage

- It is also defined as the angle measured from the instant that gives the largest output voltage to the instant it is triggered

- Angle measured from the instant SCR gets forward biased to the instant it is triggered

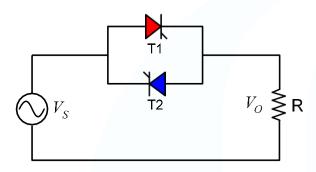

#### Single phase half controlled

- Single phase half controlled rectifier with R load

- Single phase half controlled rectifier with R L load

- Single phase half controlled rectifier with R L load and freewheeling diode

- Single phase half controlled rectifier with R L E load

- Single phase half controlled rectifier with R L E load and freewheeling diode

#### Single phase full controlled

- Single phase full controlled rectifier with R load

- Single phase full controlled rectifier with R L load (Continues conduction)

- Single phase full controlled rectifier with R L load (Discontinues conduction)

- Single phase full controlled rectifier with R L load and freewheeling diode

- Single phase full controlled rectifier with R L E load (Continues conduction)

- Single phase full controlled rectifier with R L E load (Discontinues conduction)

- Single phase full controlled rectifier with R L E load and freewheeling diode

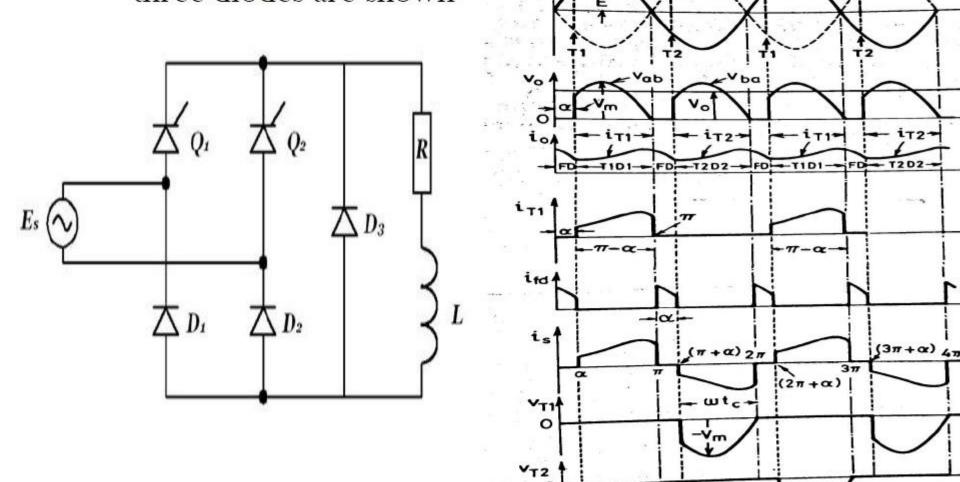

#### Single phase semi converter

- Single phase semi-converter with R load

- Single phase semi-converter with R L load (Continues conduction)

- Single phase semi-converter with R L load (Discontinues conduction)

- Single phase semi-converter with R L load and freewheeling diode

- Single phase semi-converter with R L E load (Continues conduction)

- Single phase semi-converter with R L E load (Discontinues conduction)

- Single phase semi-converter with R L E load and freewheeling diode

- The source voltage is  $v_s = V_m \sin \omega t$

- An SCR can conduct only when anode voltage is +ve and a gate signal is applied

- At some delay angle  $\alpha$ , a +ve gate signal applied between gate and cathode turns on the SCR

- Immediately full supply voltage is applied across the load

- At the instant of angle  $\alpha$ , Vo rises from zero to  $V_m \sin \omega t$

- Thyristor remains on from  $\omega t = \alpha$  to  $\pi$ ,  $(2\pi + \alpha)$  to  $3\pi$  etc...

- During this interval voltage across thyristor =0

- I is off from  $\pi$  to  $(2\pi + \alpha)$ ,  $3\pi$  to  $(4\pi + \alpha)$  etc...

- During this interval voltage across thyristor has the wave shape of supply voltage

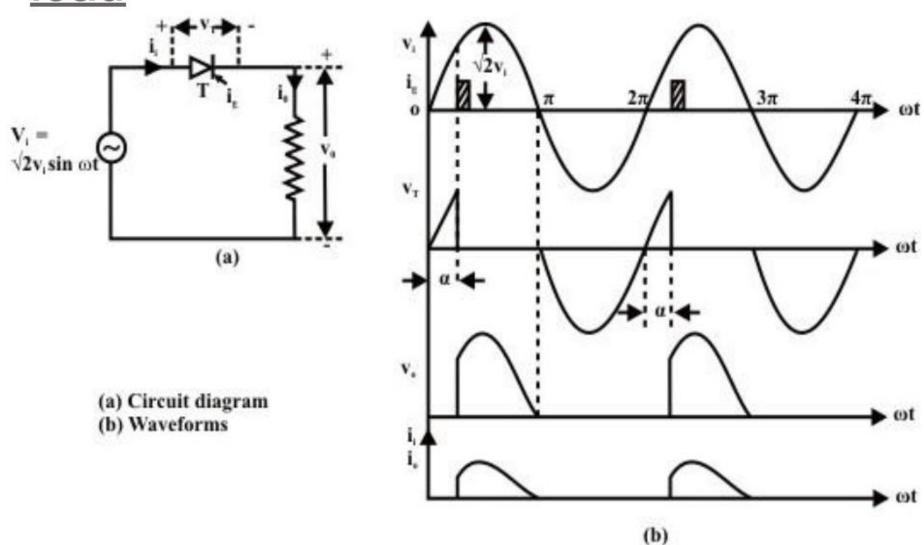

Fig. 10.1: Single phase fully controlled half wave rectifier supplying a resistive load

It may be observed that  $v_s = v_o + v_T$

As the thyristor is reverse biased for  $\pi$  radians, circuit turn of f time

$$t_c = \frac{\pi}{\omega}$$

, where  $\omega = 2\pi f$  and  $f$  is the supply frequency

Average voltage across load R is given by

$$V_o = \frac{1}{2\pi} \int_{\alpha}^{\pi} V_m \sin \omega t. \, d(\omega t) = \frac{V_m}{2\pi} (1 + \cos \alpha)$$

The maximum value of average output voltage occurs at  $\alpha = 0$

$$V_{o.m} = \frac{V_m}{2\pi} . 2 = \frac{V_m}{\pi}$$

$Also, V_o = \frac{V_{o.m}}{2} (1 + \cos \alpha)$

Average load current,

$$I_o = \frac{V_o}{R} = \frac{V_m}{2\pi R} (1 + \cos \alpha)$$

• R.m.s. value of voltage is given by

$$V_{or} = \left[\frac{1}{2\pi} \int_{\alpha}^{\pi} V_m^2 \sin^2 \omega t. d(\omega t)\right]^{1/2}$$

$$=\frac{V_m}{2\sqrt{\pi}}\Big[(\pi-\alpha)+\frac{1}{2}\sin 2\alpha\Big]^{1/2}$$

• The value of r.m.s current is

$$I_{or} = \frac{V_{or}}{R}$$

• Power delivered to resistive load = (rms load voltage)(rms load current)  $= V_{or}I_{or} = \frac{{V_{or}}^2}{R} = I_{or}^2 R$

- Input volt amperes = (rms source voltage) (total rms line current)  $= V_s I_{or} = \frac{V_s^2 \sqrt{2}}{2R\sqrt{\pi}} \left[ (\pi \alpha) + \frac{1}{2} \sin 2\alpha \right]^{1/2}$

- Input power factor

$$= \frac{power\ delivered\ to\ the\ load}{input\ VA} = \frac{V_{or}I_{or}}{V_{s}I_{or}} = \frac{V_{or}}{V_{s}}$$

$$pf = \frac{1}{\sqrt{2}\pi} \left[ (\pi - \alpha) + \frac{1}{2}\sin 2\alpha \right]^{1/2}$$

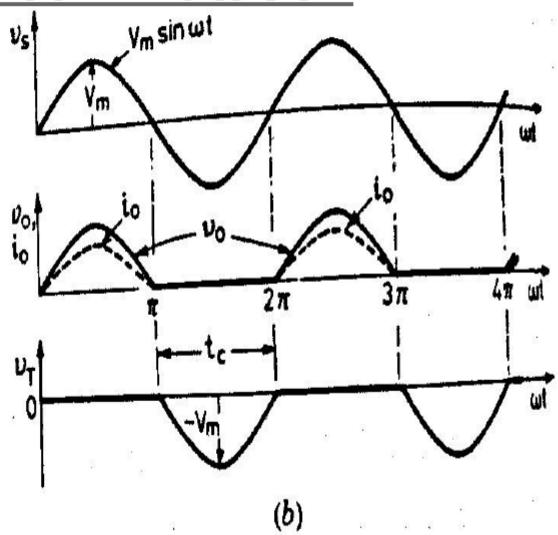

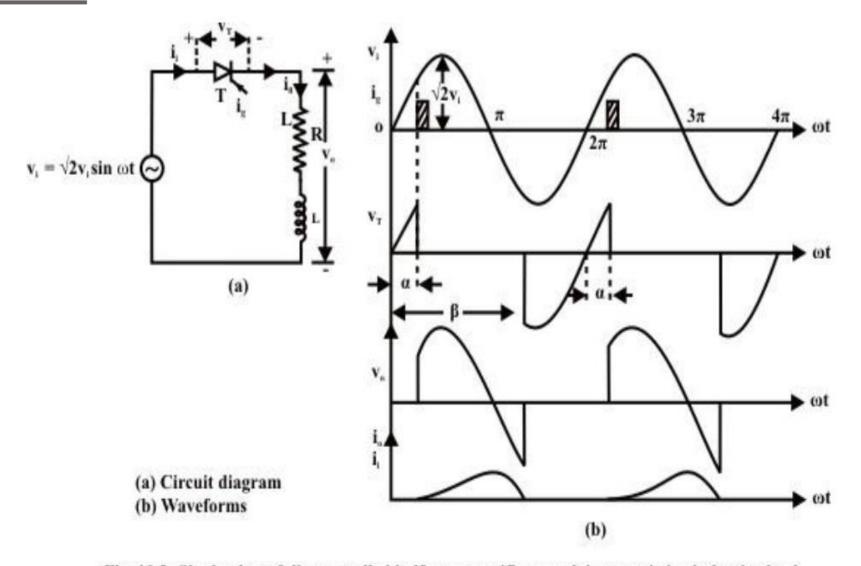

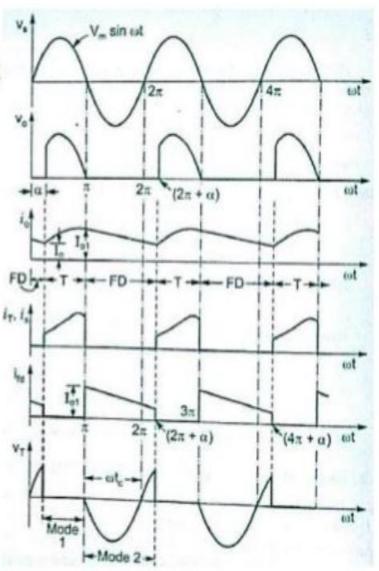

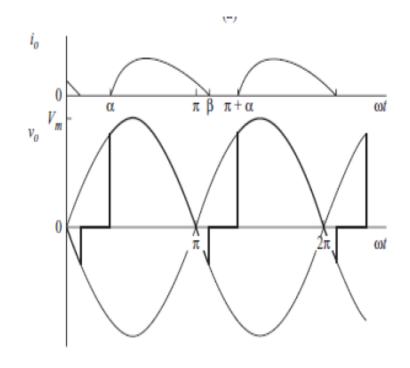

Fig. 10.2: Single phase fully controlled half wave rectifier supplying a resistive inductive load

- At  $\omega t = \alpha$  thyristor is turned on by gate signal

- The load voltage Vo at once become equal to the source voltage Vs

- But the inductance L forced the load, or output current io to rise gradually

- After some time io reaches maximum value and then begin to decrease

- At  $\omega t = \pi$ , Vo is zero but io is not zero because of the load inductance

- After ωt=π, SCR is subjected to reverse anode voltage but it will

not be turned off as load current io is not less than holding current

- At some angle  $\beta > \pi$ , io reduces to zero and SCR is turned off as it is already reverse biased

- After  $\omega t = \beta$ , vo=0 and io=0

- At  $\omega t = 2\pi + \alpha$ , SCR is triggered again, vo is applied to the load and load current develops as before

- Angle is called the extinction angle and is called the conduction angle

- The circuit turn off time  $t_c = \frac{2\pi \beta}{\omega}$

- The voltage equation for the circuit when T is on

$$V_m \sin \omega t = Ri_o + L \frac{di}{dt}$$

Average load voltage

$$V_0 = \frac{1}{2\pi} \int_{\alpha}^{\beta} V_m \sin \omega t. \, d(\omega t) = \frac{V_m}{2\pi} (\cos \alpha - \cos \beta)$$

Average load current

$$I_o = \frac{V_m}{2\pi R} (\cos \alpha - \cos \beta)$$

Rms load voltage

$$V_{or} = \left[\frac{1}{2\pi} \int_{\alpha}^{\beta} V_m^2 \sin^2 \omega t. d(\omega t)\right]^{1/2}$$

$$= \frac{V_m}{2\sqrt{\pi}} \left[ (\beta - \alpha) - \frac{1}{2} \left\{ \sin 2\beta - \sin 2\alpha \right\} \right]^{1/2}$$

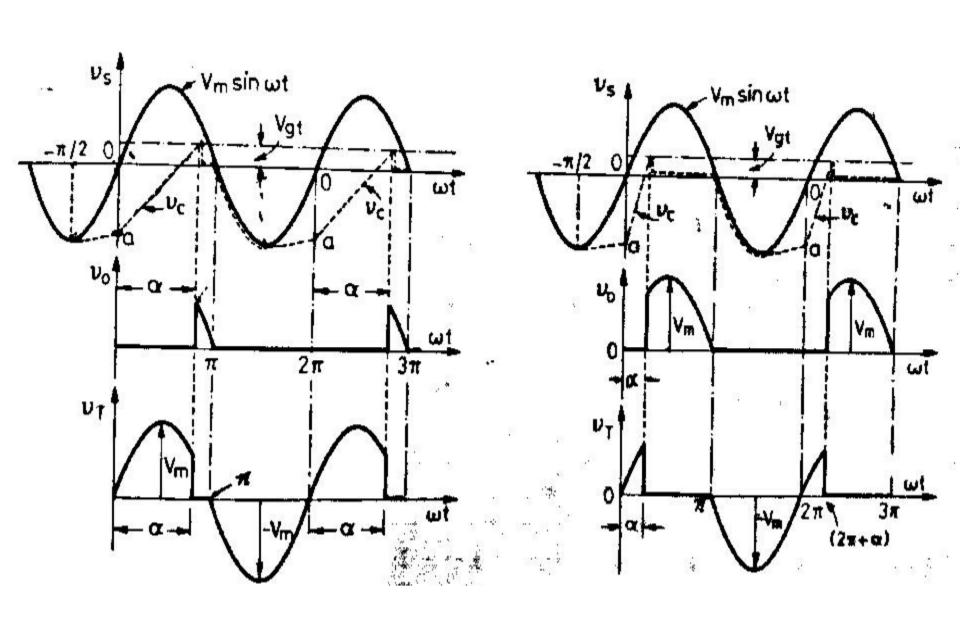

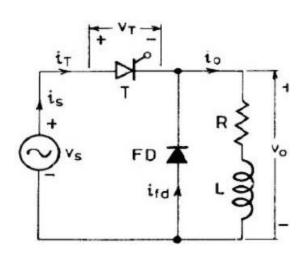

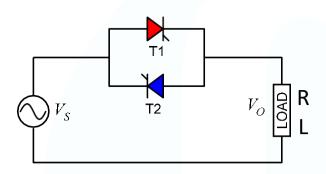

### Single phase half wave circuit with RL load and freewheeling diode

Single phase Half wave Control with R-L load & Free Wheeling Diode

- The waveform of load current io can be improved by connecting a freewheeling diode across the load

- A freewheeling diode is also called bypass diode or commutating diode

- At ωt=0, source voltage becoming +ve

- ullet At some delay angle lpha, forward biased SCR is triggered and source voltage Vs appears across the load as Vo

- At ωt=π, source voltage Vs=0, and just after this instant as Vs tends to reverse freewheeling diode FD is forward biased through the conducting SCR

- As a result load current io is immediately transferred from SCR to FD as Vs tends to reverse

- At the same time SCR is subjected to reverse voltage and zero current, it is therefore turned off at  $\omega t = \pi$

- It is assumed that during freewheeling period, load current does not decays to zero until the SCR is triggered again at  $(2\pi+\alpha)$

- Voltage drop across FD is taken as almost zero, the load voltage vo is therefore zero during the freewheeling period

- SCR is reverse biased from  $\omega t = \pi to \omega t = 2\pi$

- Therefore circuit turn off time

$$t_c = \frac{\pi}{\omega}$$

- Operation of the circuit can be explained in two modes

- First mode conduction mode

- SCR conduct from  $\alpha$  to  $\pi$ ,  $2\pi + \alpha$  to  $3\pi$  and so on and FD is reverse biased

- The duration of this mode is for  $[(\pi \alpha)/\omega]$  sec

- For conduction mode the voltage equation be

$$V_m \sin \omega t = Ri_o + L \frac{di_o}{dt}$$

- Mode II − freewheeling mode

- $\Pi$  to  $2\pi + \alpha$ ,  $3\pi$  to  $4\pi + \alpha$  etc...

- In this mode SCR is reverse biased from Π to 2π, 3π to 4π etc...

- As the load current is assume continues, FD conducts from  $\Pi$  to  $2\pi + \alpha$ ,  $3\pi$  to  $4\pi + \alpha$  etc... and so on

- The voltage equation for this mode

$$0 = Ri_o + L \frac{di_o}{dt}$$

Average load voltage is given by

$$V_0 = \frac{1}{2\pi} \int_{\alpha}^{\pi} V_m \sin \omega t. d(\omega t) = \frac{V_m}{2\pi} (1 + \cos \alpha)$$

Average load current

$$I_o = \frac{V_0}{R} = \frac{V_m}{2\pi R} (1 + \cos \alpha)$$

#### The advantages of using FD are

- Input pf is improved

- Load current waveform is improved

- Load performance is better

- As energy is stored in the inductor L is transferred to R during the freewheeling period overall converter efficiency improves

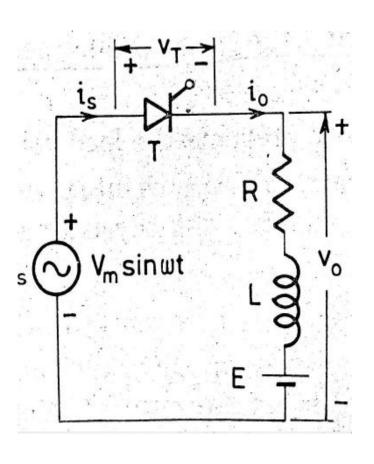

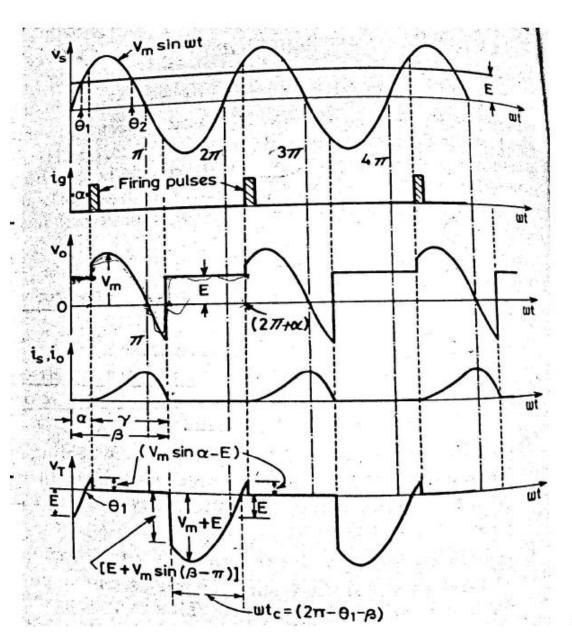

- The counter emf in the load may be due to battery or do motor

- The minimum value of firing angle is obtained form the relation  $V \sin \omega t = E$

- relation  $V_m \sin \omega t = E$  This is occur at an angle  $\theta_1 = \sin^{-1} \left( E / V_m \right)$

- In case thyristor T is fired at an angle  $\alpha < \theta_1$ , then E>Vs, SCR is reverse biased and therefore it will not turn on

- Similarly maximum value of firing angle is  $\theta_2 = \pi \theta_1$

- During the interval load current is zero and load voltage V0=E

- And during the time io not zero, vo follows vs

• Voltage equation  $V_m \sin \omega t = Ri_o + L \frac{di_o}{dt} + E$

$$V_0 = \frac{1}{2\pi} \int_{\alpha}^{\beta} V_m \sin \omega t. d(\omega t) + E(2\pi + \alpha - \beta)$$

$$= \frac{1}{2\pi} \left[ V_m(\cos \alpha - \cos \beta) + E(2\pi + \alpha - \beta) \right]$$

• Average load current  $I_o = \frac{1}{2\pi R} [V_m(\cos\alpha + \cos\theta_1) - E(\pi - (\theta_1 + \alpha))]$

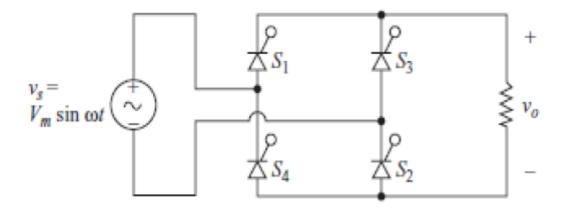

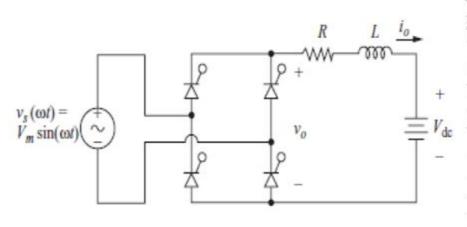

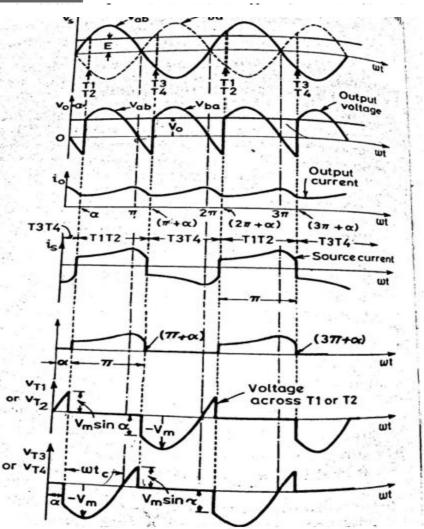

## Single phase fully controlled bridge rectifier with R load

- The output voltage waveform for a controlled full-wave rectifier with a resistive load is shown in Fig.

- The average component of this waveform is determined from

$$V_o = \frac{1}{\pi} \int_{\alpha}^{\pi} V_m \sin(\omega t) d(\omega t) = \frac{V_m}{\pi} (1 + \cos \alpha)$$

Average output current

$$I_o = \frac{V_o}{R} = \frac{V_m}{\pi R} (1 + \cos \alpha)$$

Rms value of output voltage

$$V_{or} = \left[\frac{1}{\pi} \int_{\alpha}^{\pi} V_m^2 \sin^2 \omega t. d(\omega t)\right]^{1/2} = \left[\frac{V_m^2}{2\pi} [(\pi - \alpha) + (1 + \cos 2\alpha)]\right]^{1/2}$$

LL //IL DATTION LIAMENANIA

• The power delivered to the load is a function of the input voltage, the delay angle, and the load components;  $P = I^2$  rms R is used to determine the power in a resistive load, where

$$I_{\text{rms}} = \sqrt{\frac{1}{\pi}} \int_{\alpha}^{\pi} \left(\frac{V_m}{R} \sin \omega t\right)^2 d(\omega t)$$

$$= \frac{V_m}{R} \sqrt{\frac{1}{2} - \frac{\alpha}{2\pi} + \frac{\sin(2\alpha)}{4\pi}}$$

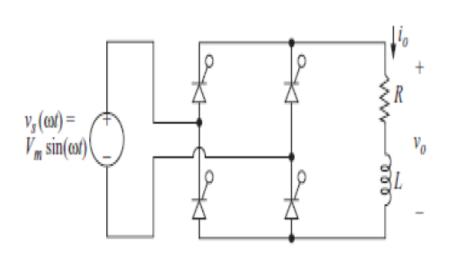

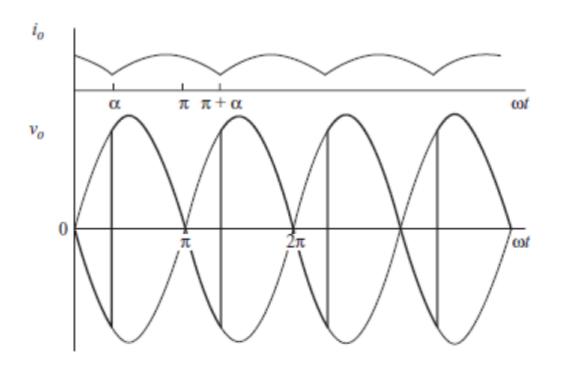

# Single phase fully controlled bridge rectifier with RL load

#### Discontinues conduction

- Load current for a controlled full-wave rectifier with an RL load can be either continuous or discontinuous, and a separate analysis is required for each.

- Starting the analysis at  $\omega t = 0$  with zero load current, SCRs S1 and S2 in the bridge rectifier will be forward-biased and S3 and S4 will be reverse-biased as the source voltage becomes positive.

- Gate signals are applied to S1 and S2 at  $\omega t = \alpha$ , turning S1 and S2 on.

- With S1 and S2 on, the load voltage is equal to the source voltage.

Current function

$$i_o(\omega t) = \frac{V_m}{Z} \left[ \sin(\omega t - \theta) - \sin(\alpha - \theta) e^{-(\omega t - \alpha)/\omega \tau} \right] \quad \text{for } \alpha \le \omega t \le \beta$$

where

$$Z = \sqrt{R^2 + (\omega L)^2} \qquad \theta = \tan^{-1} \left( \frac{\omega L}{R} \right) \quad \text{and} \quad \tau = \frac{L}{R}$$

- The above current function becomes zero at  $\omega t = \beta$ .