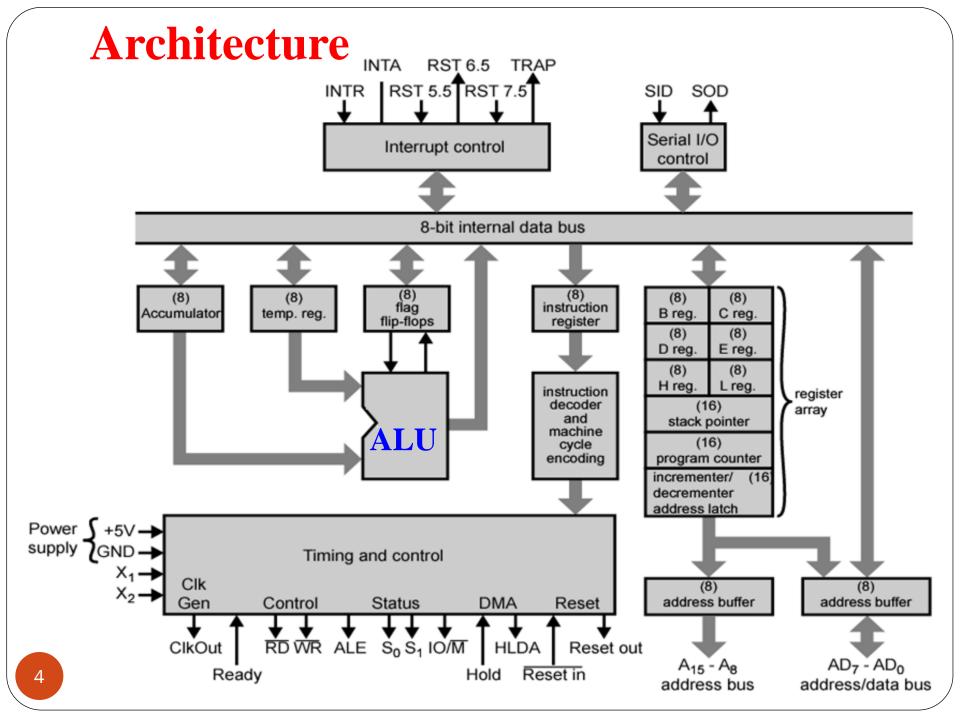

## MICROPROCESSOR 8085

# MODULE 1

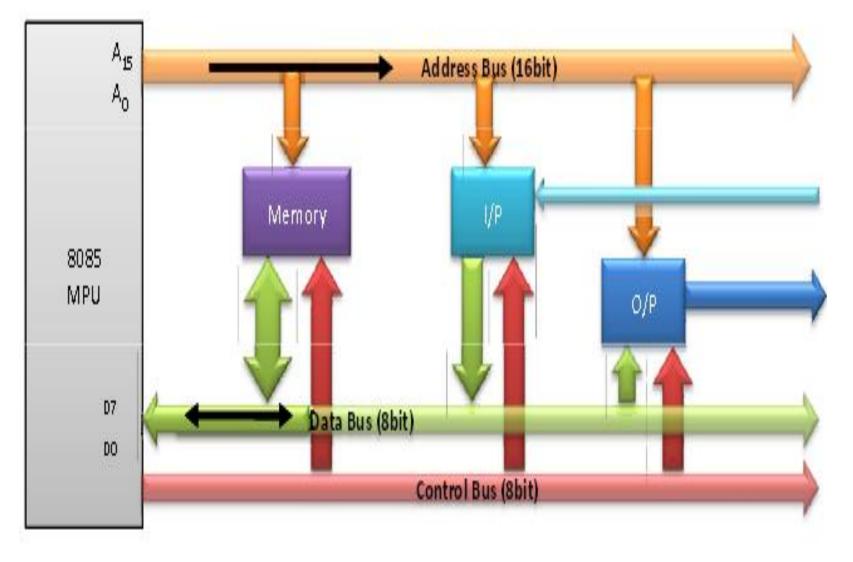

## **8085 Bus Structure**

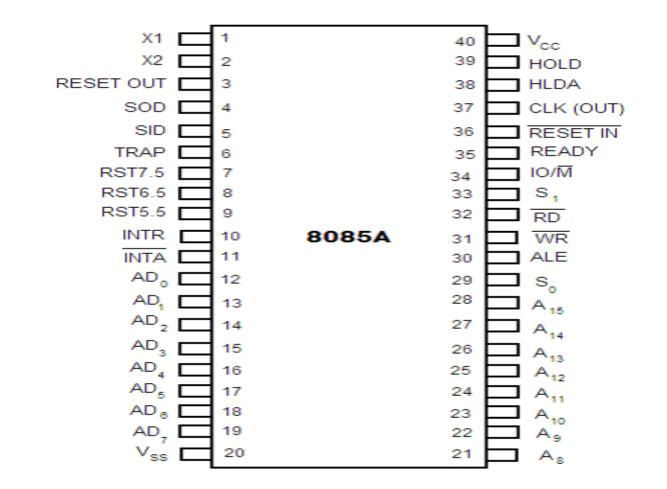

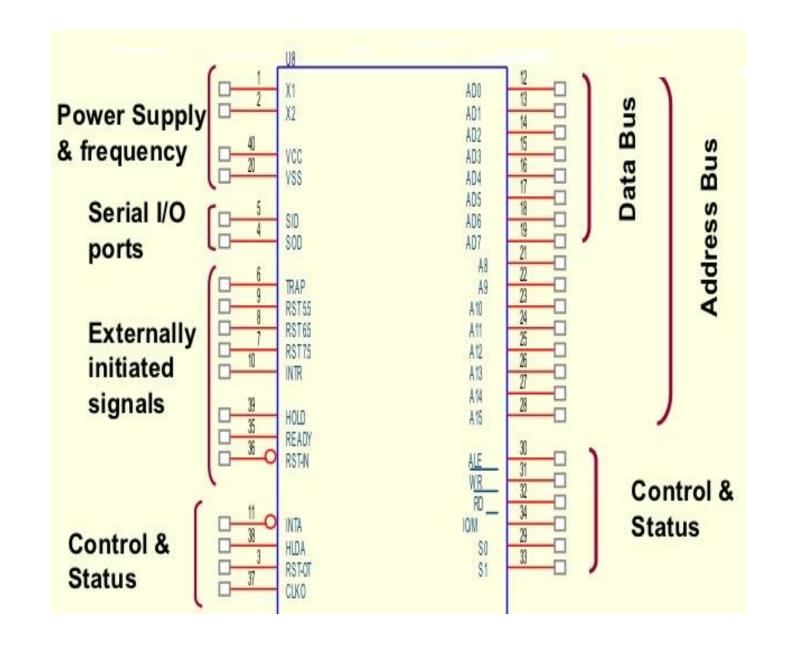

#### **PIN DIAGRAM**

### **Instruction & Data Formats**

8085 Instruction set can be classified **according to size (in bytes)** as

- 1. 1-byte Instructions

- 2. 2-byte Instructions

- 3. **3-byte Instructions**

- 1. Includes Opcode and Operand in the same byte

- 2. First byte specifies Operation Code Second byte specifies Operand

- 3. First byte specifies Operation Code Second & Third byte specifies Operand

#### **Instruction & Data Formats**

- 1. 1-byte Instructions Eg. MOV A, M, CMA, DAA etc

- 2. 2-byte Instructions Eg. MVI A, 08, IN 02, CPI 03 etc

- 3. 3-byte Instructions Eg. LXI H, 4500, STA 4600, LDA 4200

### **Addressing Modes of 8085**

- The microprocessor has **different ways of specifying the data or operand** for the instruction.

- The various formats of specifying operands are called addressing modes

- The 8085 has **Five addressing modes**:

- 1) **Register Addressing mode:** This type of addressing mode specifies register or register pair that contains data.

- Example: ADD B, MOV B A

#### Addressing Modes of 8085

- 2) Immediate Addressing Mode:

- In this type of addressing mode, **immediate data byte is provided with the instruction.**

- Example: MVI A 47H, LXIH, 4100H etc.

## **Memory Addressing**

- One of the operands is a memory location

- Depending on how address of memory location is specified, memory addressing is of two types

- **Direct** addressing

- Indirect addressing

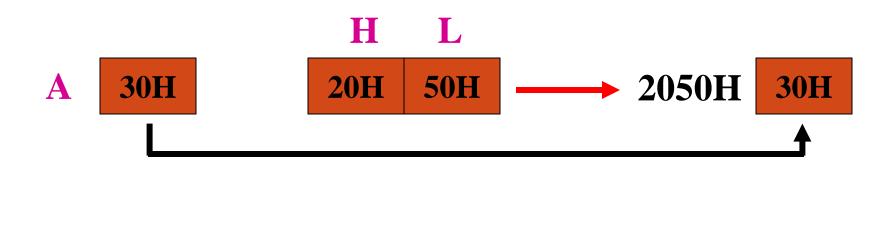

- 3) Direct Addressing Mode: In this type of addressing mode, the 16bit memory address is directly provided with the instruction.

- Example: LDA C5 00 , STA 3050H etc

## Addressing Modes of 8085

- 4) Indirect Addressing Mode: In this type of addressing mode, the 16bit memory address is indirectly provided with the instruction using a register pair

- Example: LDAX B

- (Load the accumulator with the contents of the memory location whose address is stored in the register pair BC)

- MOV M, A ;copy register A to memory location whose address is stored in register pair HL

### **Addressing Modes of 8085**

- 5) **Implied Addressing mode:** In this type of addressing mode, **No operand (register or data) is specified in the instruction.**

- The operand is inborn to the instruction.

- Example: CMA (Complement Accumulator), SIM, RIM etc

# **INSTRUCTION SET**

### **Instruction Set of 8085**

- Consists of

- 74 operation codes, e.g. MOV, MVI

- 246 Instructions, e.g. MOV A,B, MVI A,03

- 8085 instructions can be classified as

- 1. Data Transfer (Copy)

- 2. Arithmetic

- 3. Logical and Bit manipulation

- 4. Branch

- 5. Machine Control

### **Data Transfer Instruction**

- MOV Move

- MVI Move Immediate

- LDA Load Accumulator Directly from Memory

- STA Store Accumulator Directly in Memory

- LHLD Load Hand L Registers Directly from Memory

- SHLD Store Hand L Registers Directly in Memory

- LXI Load register pair Immediate

- LDAX Load accumulator indirect

- STAX Store Accumulator In direct

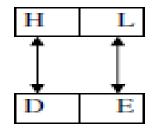

- XCHG Exchange DE pair and HL pair

- XTHL Exchange between HL pair and stack

#### **Data Transfer Instruction**

#### 16bit Data transfer

LHLD 16bit address

#### Example:

#### LHLD C050

Loads data from C050 memory location to Register L and Loads data from C051 memory location to Register H

SHLD 16bit address

#### Example:

#### SHLD C050

Stores data of *Register L* to memory location C050. and Stores data of *Register H* to memory location C051.

#### XCHG

Exchanges the content of HL and DE Register Pair

## **Data Transfer Instructions**

#### • IN portaddr

• i.e. IN 00 (Reads data from the Input Switch, 0 Orepresents the port address of the input switch)

#### • OUT portaddr

• i.e. OUT 00 (Writes data to the Display device where 00 represents the Port address of the display)

#### **Arithmetic Instructions**

- ADDAdd to Accumulator

- ADI Add Immediate Data to Accumulator

- ADCAdd to Accumulator Using Carry Flag

- ACI Add Immediate Data to Accumulator Using Carry Flag

- SUB Subtract from Accumulator

- SUI Subtract Immediate Data from Accumulator

#### **Arithmetic Instructions**

Flag

Borrow

- SBB Subtract from Accumulator Using Borrow ((:Carry)

- SBI Subtract I mmediate from Accumulator Using

- INR Increment Specified Byte by One

- DCRDecrement Specified Byte by One

- INX Increment Register Pair by One

- DCXDecrement Register Pair by One

- DADDouble Register Add: Add Contents of Register

Pair to Hand L Register Pair

#### **Arithmetic Instructions**

#### 16 bit addition instructions

DAD Rp : Adds the content of the HL register with the content of the Register pair specified by Rp and stores the result in the HL register pair

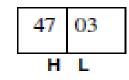

Example:

DAD B

Adds the content of the HL register with the content of the BC register pair stores the result in the HL register pair

HL ← HL+BC

DAD B will result in :

0100 0001 0000 0001 0000 0110 0000 0010 0100 0111 0000 0011

- ANA Logical AND with Accumulator

- ANI Logical AND with Accumulator Using Immediate Data

- ORA Logical OR with Accumulator

- ORI Logical OR with Accumulator Using Immediate Data

- XRA Exclusive Logical OR with Accumulator

- XRI Exclusive OR Using Immediate Data

- CMP Compare

- CPI Compare Using Immediate Data

- RLC Rotate Accumulator Left

- RRC Rotate Accumulator Right

- RAL Rotate Left Through Carry

- RAR Rotate Right Through Carry

- CMA Complement Accumulator

- CMC Complement Carry Flag

- STC Set Carry Flag

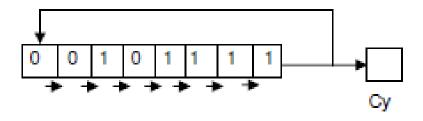

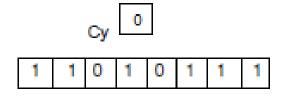

#### RLC (Rotate Accumulator Left)

Every bit of the Accumulator is shifted one bit left and the MSB bit of the Accumulator is copied into the Carry flag and into the Aoth bit

After the RLC instruction is executed the content of the Accumulator and the carry flag will be

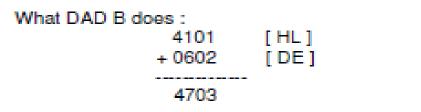

#### RRC (Rotate Accumulator Right)

Every bit of the Accumulator is shifted one bit Right and the LSB bit of the Accumulator is copied into the Carry flag and into the Azth bit

After the RRC instruction is executed the content of the Accumulator and the carry flag will be

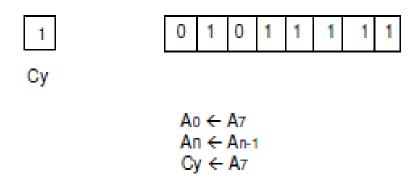

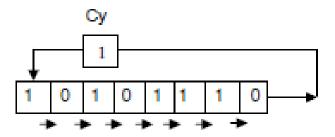

#### RAL (Rotate Accumulator Left through Carry)

Every bit of the Accumulator is shifted one bit left and the MSB bit of the Accumulator is copied into the Carry flag and the Carry flag value is copied into the Acth bit

After the RAL instruction is executed the content of the Accumulator and the carry flag will be

$A_0 \leftarrow Cy$   $A_1 \leftarrow A_{n-1}$  $Cy \leftarrow A_7$

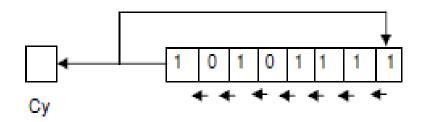

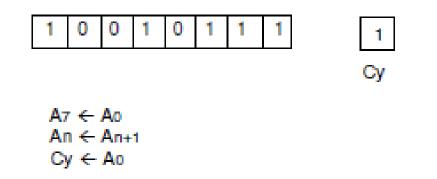

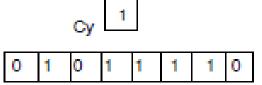

#### RAR (Rotate Accumulator Right through Carry)

Every bit of the Accumulator is shifted one bit Right and the LSB bit of the Accumulator is copied into the Carry flag and the Carry flag value is copied into the Arth bit

After the RAR instruction is executed the content of the Accumulator and the carry flag will be

$A_7 \leftarrow Cy$   $A_1 \leftarrow A_{n+1}$  $Cy \leftarrow A_0$

### **Branching Instructions**

- The unconditional branching instructions are as follows:

- JMP Jump

- CALL Call

- RET Return

- Conditional branching instructions

| • jumps | Calls | Returns        |

|---------|-------|----------------|

| • JC    | CC    | RC (Carry)     |

| • JNC   | CNC   | RNC (No Carry) |

| • JZ    | CZ    | RZ (Zero)      |

| • JNZ   | CNZ   | RNZ (Not Zero) |

## **Jump Instructions**

| Opcode | Description         | Status Flags |

|--------|---------------------|--------------|

| JC     | Jump if Carry       | CY = 1       |

| JNC    | Jump if No Carry    | CY = o       |

| JP     | Jump if Positive    | S = o        |

| JM     | Jump if Minus       | S = 1        |

| JZ     | Jump if Zero        | Z = 1        |

| JNZ    | Jump if No Zero     | Z = o        |

| JPE    | Jump if Parity Even | P = 1        |

| JPO    | Jump if Parity Odd  | P = o        |

### **Call Instructions**

| Opcode | Description         | Status Flags |

|--------|---------------------|--------------|

| CC     | Call if Carry       | CY = 1       |

| CNC    | Call if No Carry    | CY = o       |

| СР     | Call if Positive    | S = o        |

| СМ     | Call if Minus       | S = 1        |

| CZ     | Call if Zero        | Z = 1        |

| CNZ    | Call if No Zero     | Z = o        |

| CPE    | Call if Parity Even | P = 1        |

| CPO    | Call if Parity Odd  | P = o        |

|        |                     |              |

### **Return Instructions**

| Opcode | Description                    | Status Flags |

|--------|--------------------------------|--------------|

| RC     | Return if Carry                | CY = 1       |

| RNC    | Return if No Carry             | CY = o       |

| RP     | Return if Positive             | S = o        |

| RM     | Return if Minus                | S = 1        |

| RZ     | Return if Zero                 | Z = 1        |

| RNZ    | Return <mark>if</mark> No Zero | Z = o        |

| RPE    | Return if Parity Even          | P = 1        |

| RPO    | Return if Parity Odd           | P = o        |

#### Stack, I/O, and Machine Control Instructions.

- PUSH Push Two Bytes of Data onto the Stack

- POP Pop Two Bytes of Data off the Stack

- XTHL Exchange Top of Stack with Hand L

- SPHL Move contents of Hand L to Stack Pointer

- The I/O instructions are as follows:

- IN Initiate Input Operation OUT Initiate Output Operation

#### Stack, I/O, and Machine Control Instructions.

- The machine control instructions are as follows:

- EI Enable Interrupt System

- DI Disable Interrupt System

- HLT Halt

- NOP No Operation

# MODULE 2

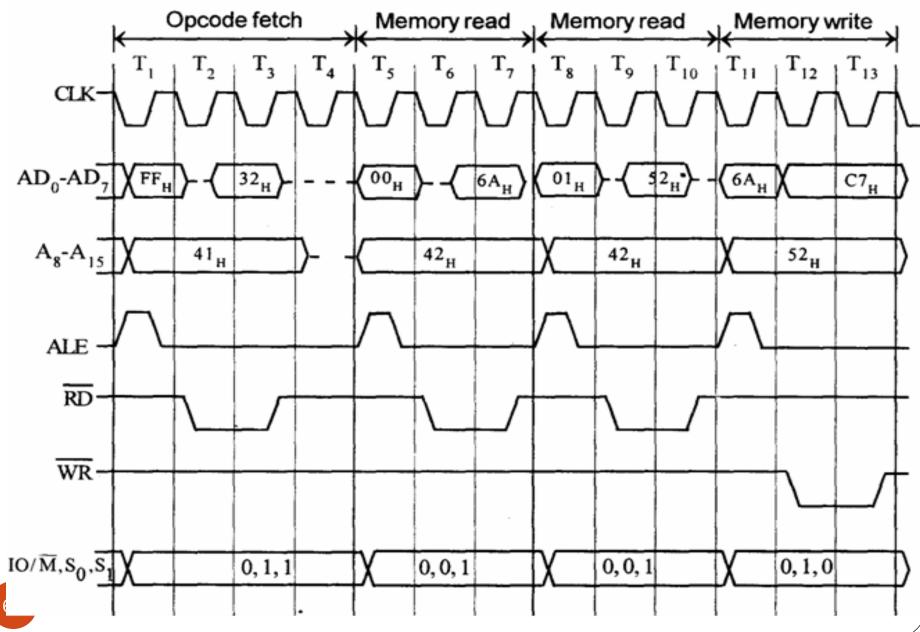

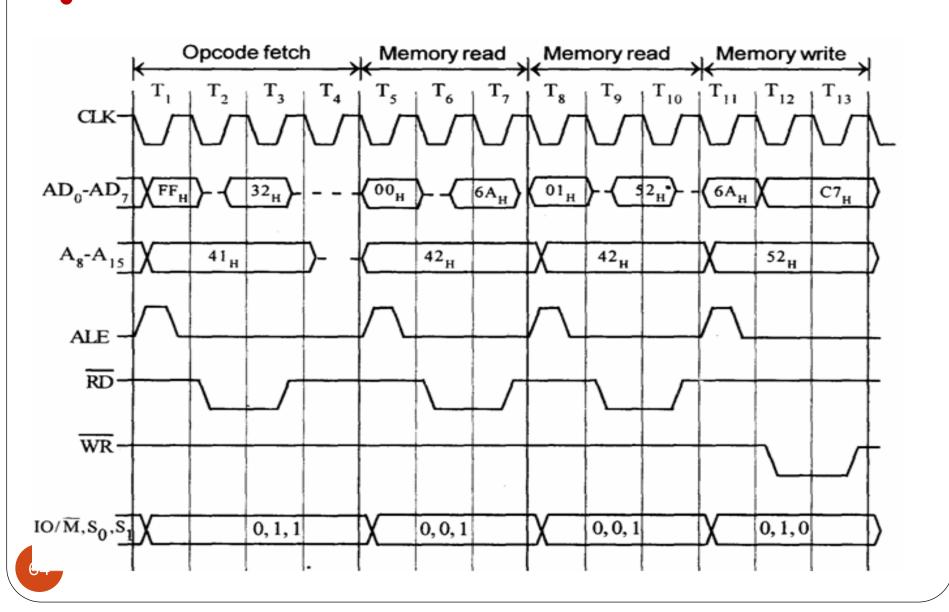

#### **TIMING DIAGRAM**

34

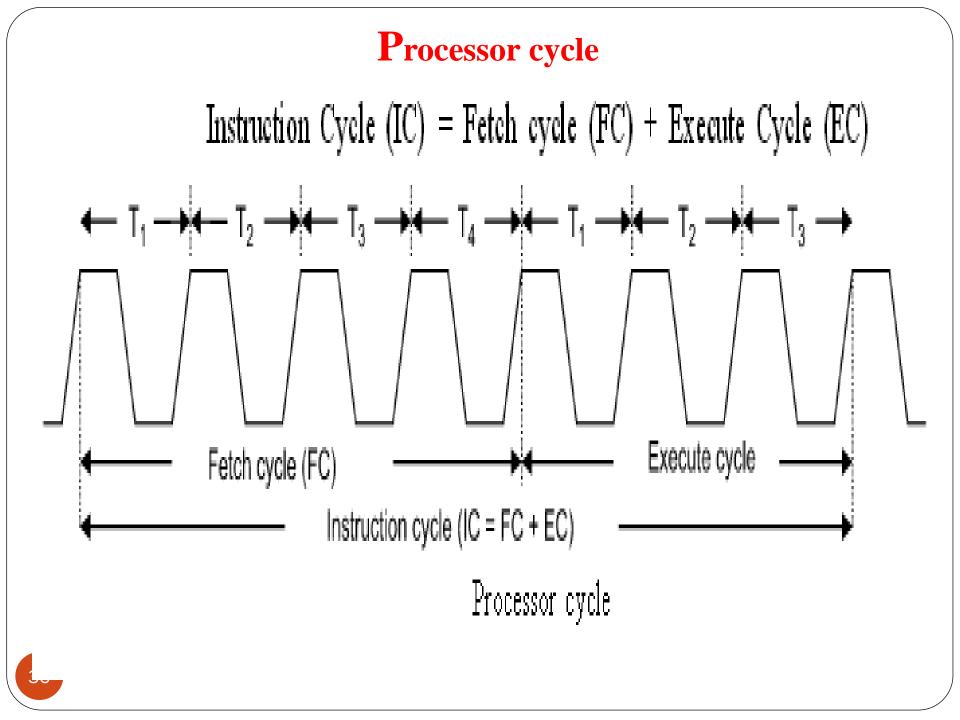

# PROCESSOR AND MECHINE CYCLE

#### **Machine Cycle**

A separate operation performed by microprocessor is called machine cycle.

• MC1= Opcode Fetch---- 4/7 T states

### • MC2= Memory Read, Memory write, I/O/read, I/O write----- 3 T states

# **INSTUCTION EXECUTION**

- Microprocessor reads the instruction byte by byte and then executes it.

- The instruction execution cycle can be clearly divided into three different parts

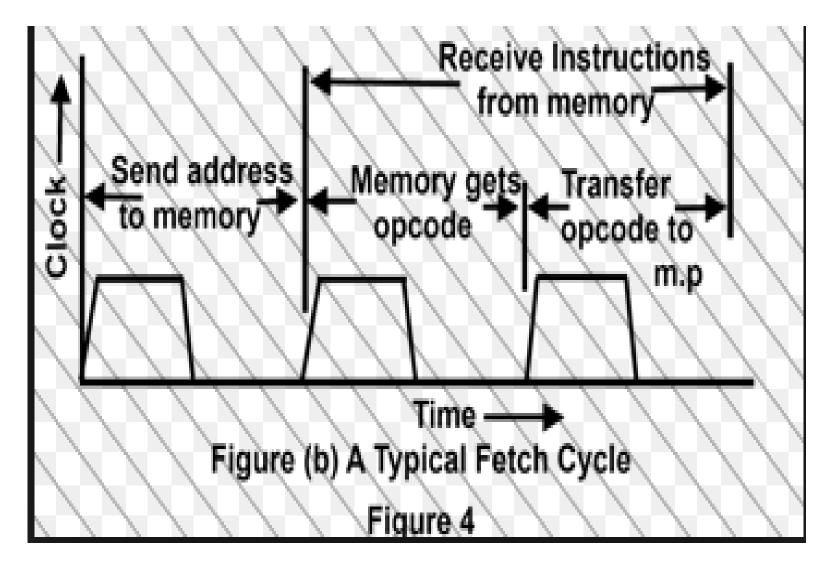

#### • Fetch Cycle

The fetch cycle takes data required from memory, stores it in the instruction register.

#### **Instruction execution**

#### •Decode Cycle

It determines which opcode and addressing mode have been used, and as such what actions need to be carried out in order to execute the instruction.

#### •Execute Cycle

The actual actions which occur during the execute cycle of an instruction.

#### **Instruction execution**

#### •OPCODE

•Opcode is nothing but the machine language instruction which denotes the microprocessor about **what operation should be performed on the specific data.**

• OPERAND

•The data followed by opcode.

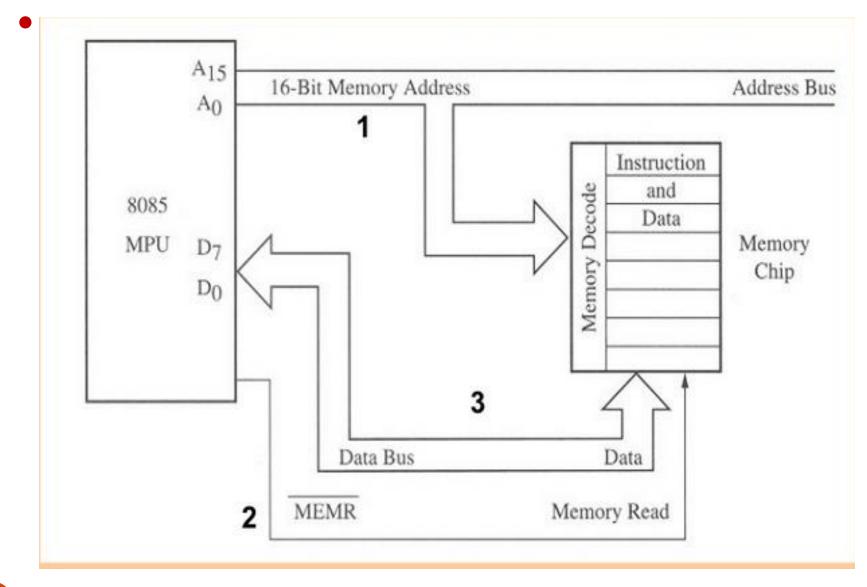

## **Instruction Execution**

- 8085 instruction cycle includes

- 1. Identify the memory location

- 2. Generate timing and control signals

- 3. Data transfer takes place

- 4. Decoding the instruction

- 5. Execution

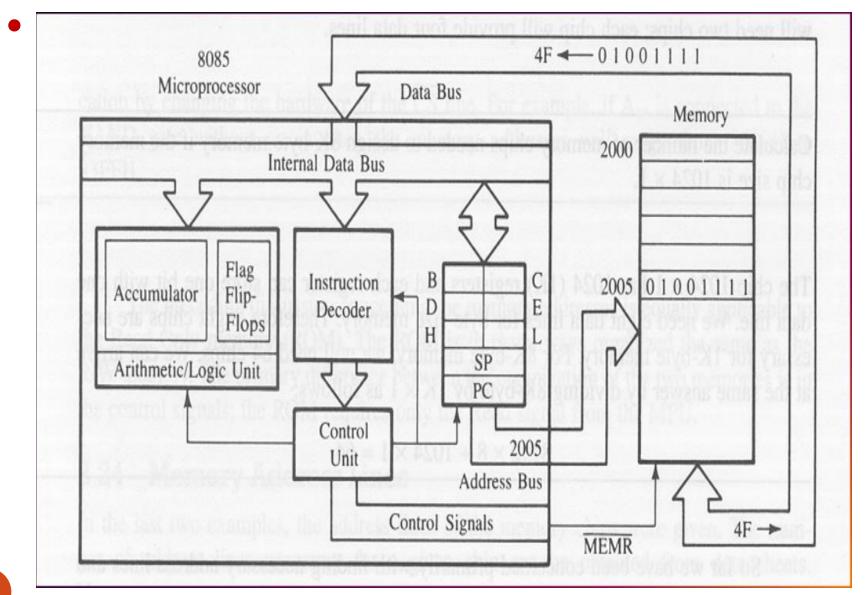

# **1. Identify Memory Location**

# **2.** Generating Control Signals

#### Machine cycle status and control signals

|                                                                       | Status |                |                | Controls |    |      |

|-----------------------------------------------------------------------|--------|----------------|----------------|----------|----|------|

| Machine cycle                                                         | IO/M   | S <sub>1</sub> | S <sub>0</sub> | RD       | WR | INTA |

| Opcode Fetch (OF)                                                     | 0      | 1              | 1              | 0        | 1  | 1    |

| Memory Read                                                           | 0      | 1              | 0              | 0        | 1  | 1    |

| Memory Write                                                          | 0      | 0              | 1              | 1        | 0  | 1    |

| I/O Read (I/OR)                                                       | 1      | 1              | 0              | 0        | 1  | 1    |

| I/O Write (I/OW)                                                      | 1      | 0              | 1              | 1        | 0  | 1    |

| Acknowledge of INTR (INTA)                                            | 1      | 1              | 1              | 1        | 1  | 0    |

| BUS Idle (BI) : DAD                                                   | 0      | 1              | 0              | 1        | 1  | 1    |

| ACK of RST, TRAP                                                      | 1      | 1              | 1              | 1        | 1  | 1    |

| HALT                                                                  | Z      | 0              | 0              | Z        | Z  | 1    |

| HOLD                                                                  | Z      | Х              | X              | Z        | Z  | 1    |

| $X \Rightarrow$ Unspecified, and $Z \Rightarrow$ High impedance state |        |                |                |          |    |      |

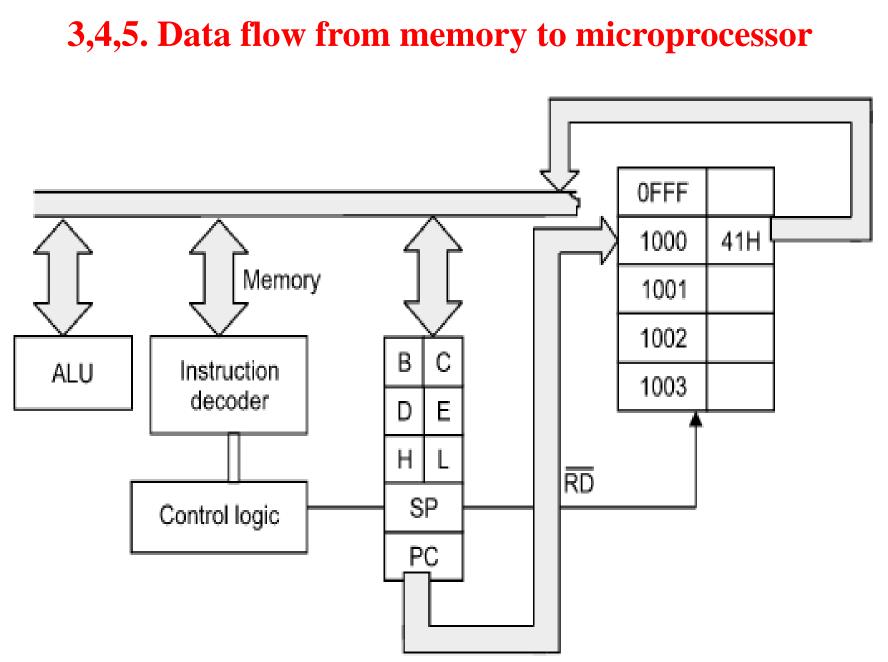

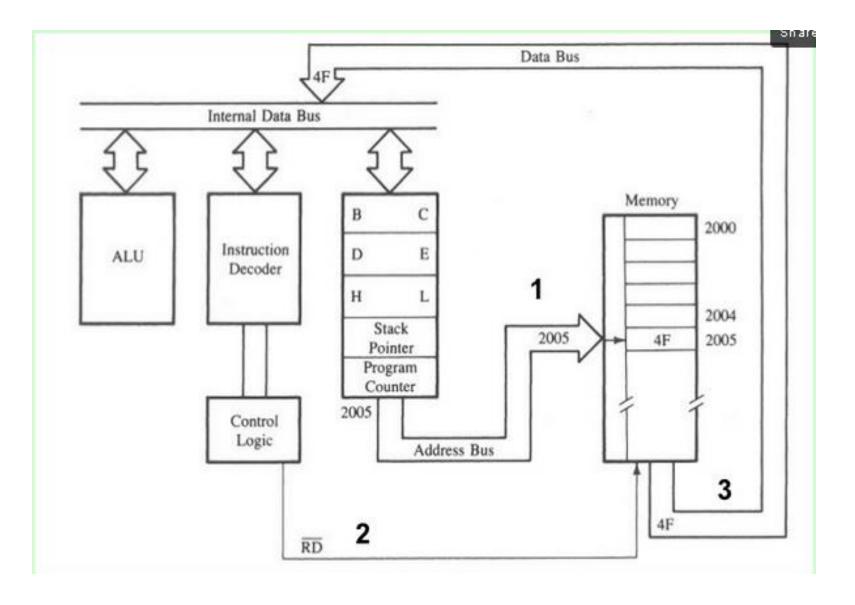

#### 3,4,5. Data flow from memory to microprocessor

•Memory usually starts at address 0000h and could go up to FFFFh (216 or 64K or 65536 in total).

•To access these locations, a 16 bit address is presented to memory and the byte at that location is either read or written.

•The Program Counter is what holds this address when the micro is executing instructions.

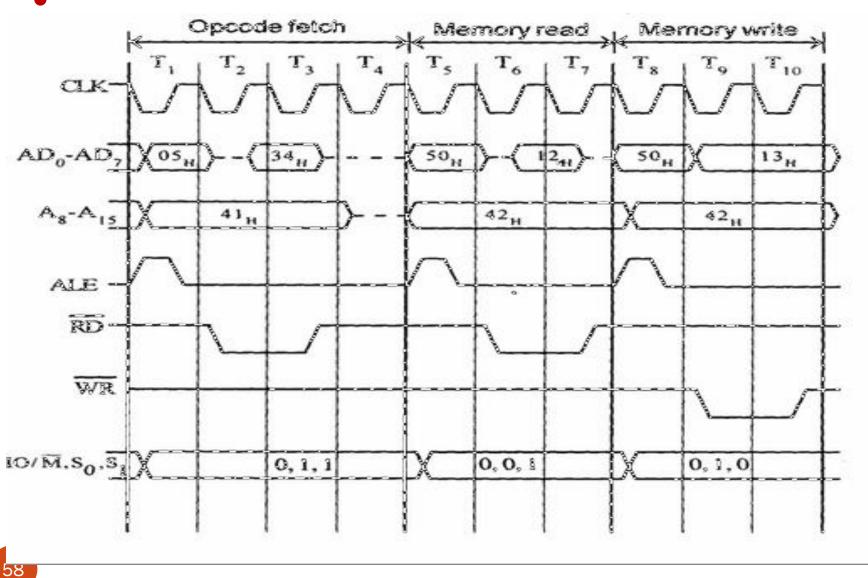

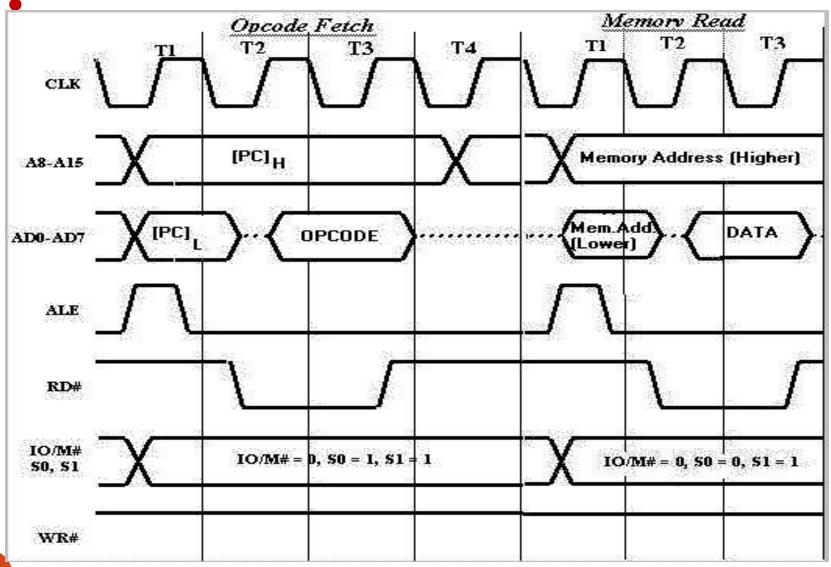

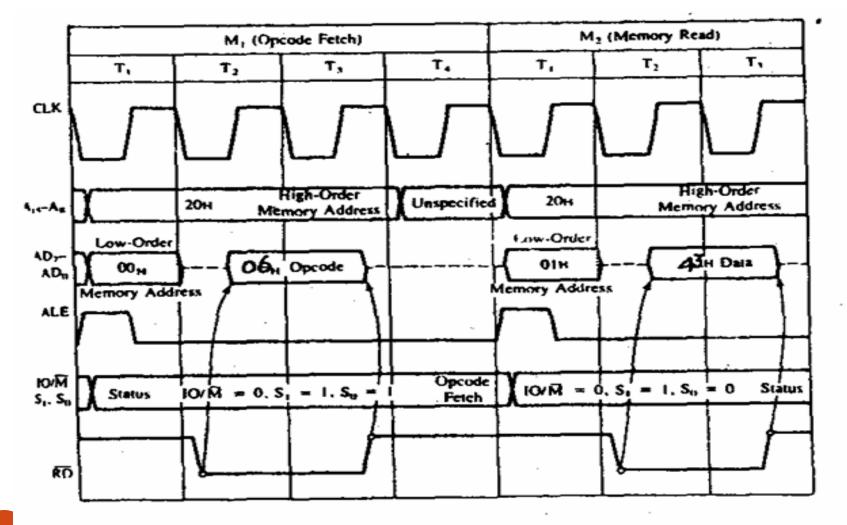

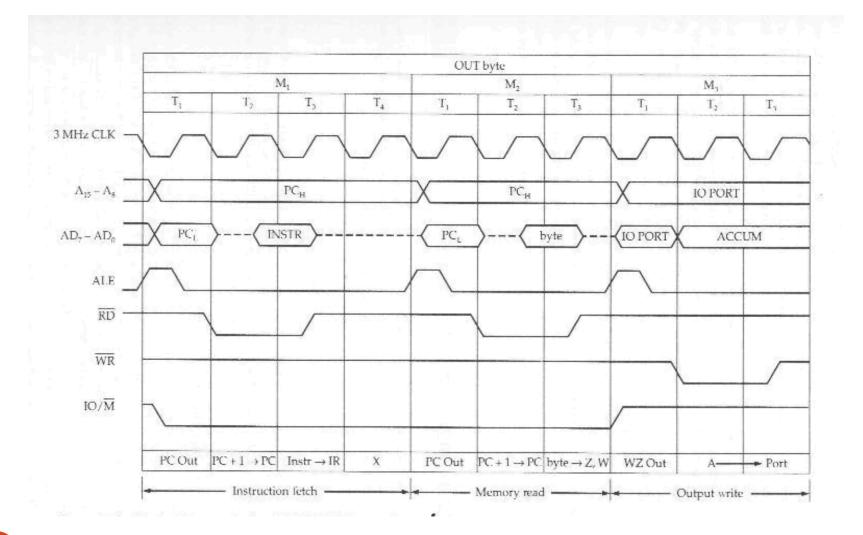

# **TIMING DIAGRAMS**

#### **Timing Diagram examples**

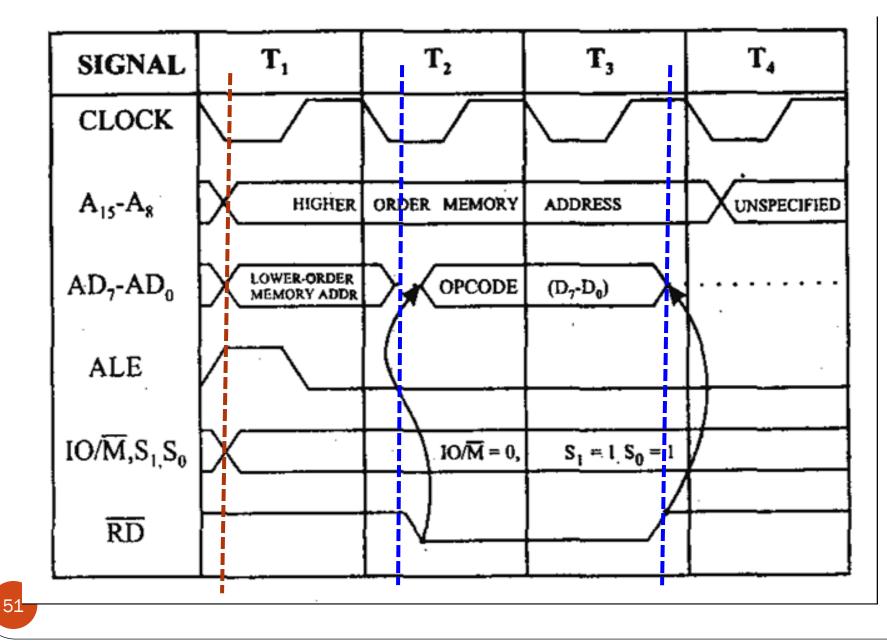

- Timing diagram is the graphical representation of the initiation of read/write and transfer of data operations under the control of 3-status signals IO / M, S1, and S0.

- In 8085, we have 5 machine cycles

- 1. Opcode fetch

- 2. Memory read

- 3. Memory Write

- 4. I/O read

- 5. I/O write

### **Opcode Fetch cycle**

### • It is similar to memory read

### **Opcode Fetch cycle**

#### **Opcode fetch**

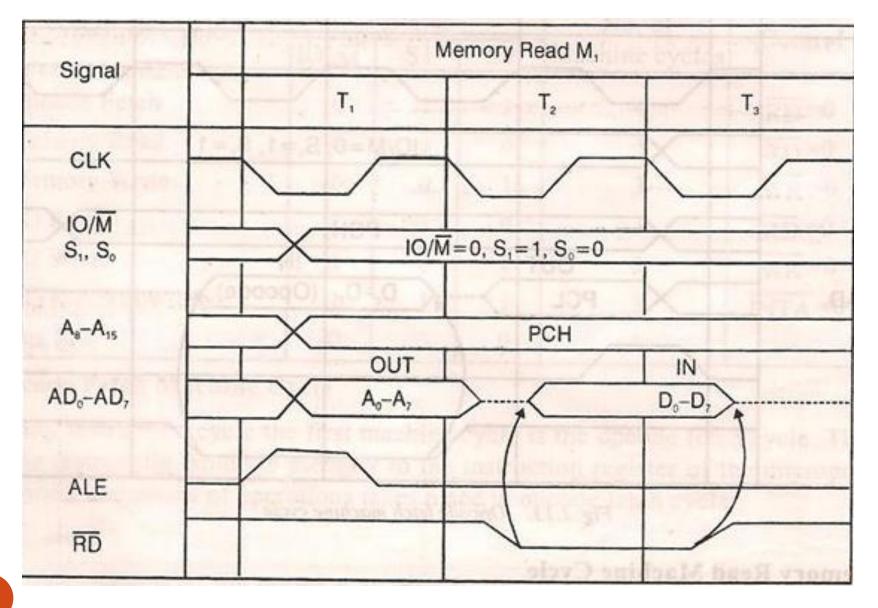

#### **Memory Read**

#### **Memory Read**

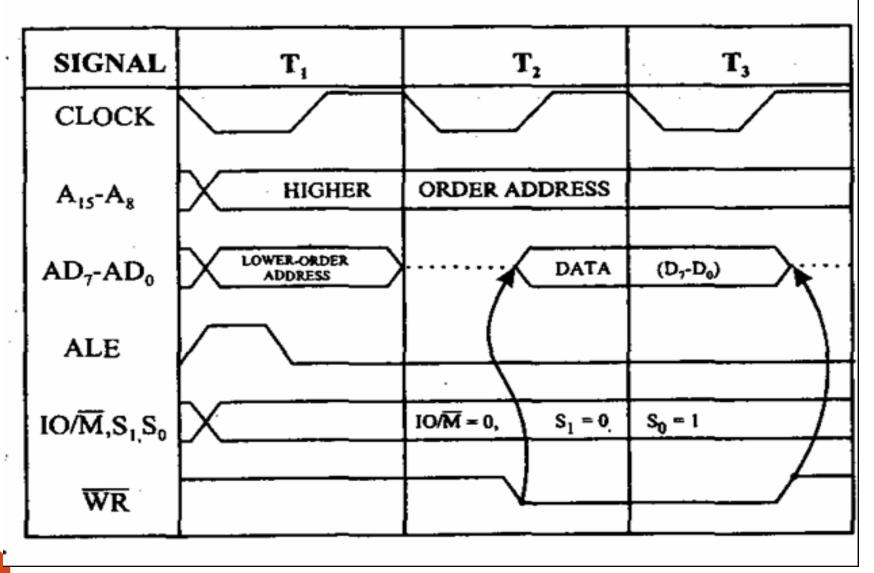

#### **Memory write**

54

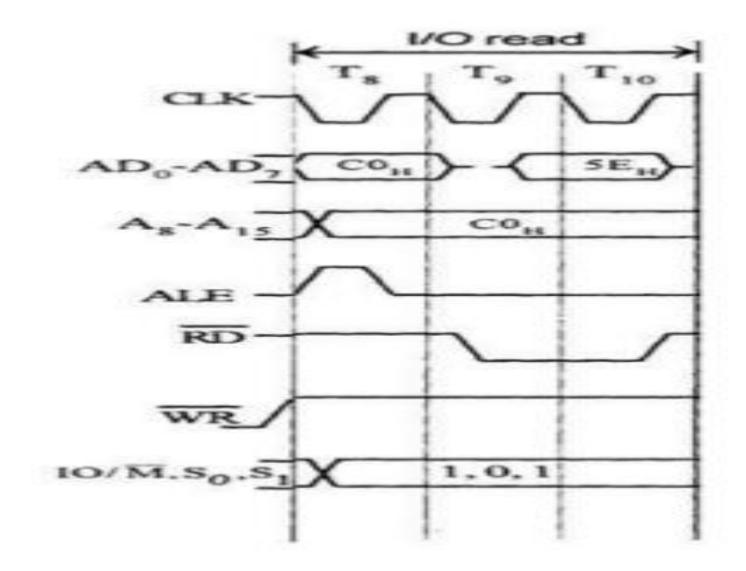

#### I/O Read

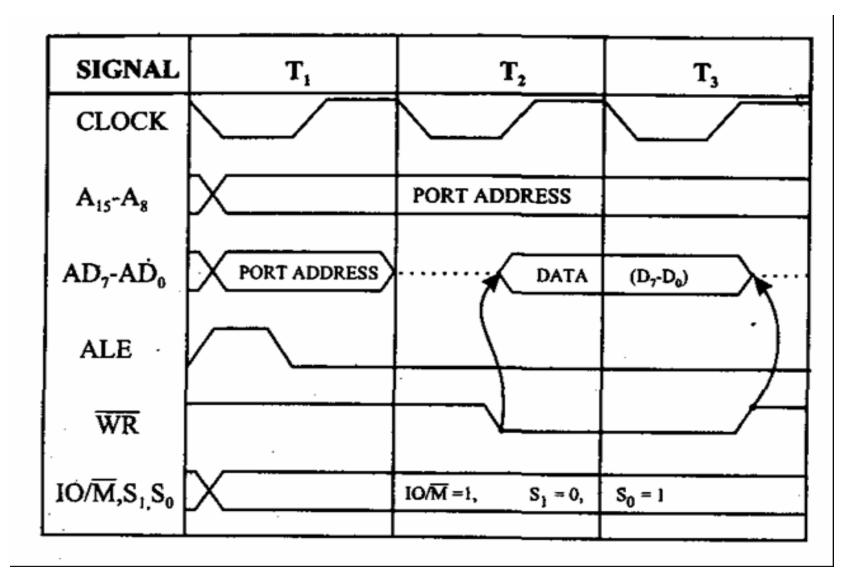

#### **I/O Write**

# TIMING DIAGRAMS EXAMPLE

# **Timing Diagram INR M**

# **Timing Diagram ADD M**

### **Timing Diagram MVI B, Data**

#### **Timing Diagram IN, 8 bit address** Opcode fetch I/O read Memory read T. T<sub>8</sub> T 10 T7 T3 To T. T<sub>6</sub> 5 CLK. DBH 26<sub>H</sub> SEH) COH AD0-AD7 25H COH > A8-A15 41 1 41,88 COH ALE RD-WR 10/M.S.,S. 0, 0, 1 0, 1, 1 1,0,1 М Y

### **Timing Diagram OUT, 8 bit address**

# **Timing Diagram STA**

# **Timing Diagram STA**

# Programming

• 1.Write an assembly program to add two numbers

o MVI D, 02BH

- 0 MVI C, 06FH

- o MOVA, C

- o ADD D

- o STA 4500

- o HLT

# Program

1. Write an assembly program to add two numbers

o LXI H, 4500

- o MOVA, M

- o INX H

- o ADD M

- o STA 4500

- o HLT

# Program

2. Write an Assembly Language Program to add two numbers ; results contain carry

LXI H, 4500 MOVA, M INX H **ADD M** JNC LOOP1 **INR** C LOOP1 **STA 4500** MOVA, C **STA 4501 HLT**

# Program

2. Write an Assembly Language Program to add two numbers ; results contain carry ( write the program using JC)

LXI H, 4500 MOV A, M

INX H

ADD M

JC LOOP 1

JMP LOOP 2

LOOP1 INR C

**STA 4500**

LOOP1 MOVA, C

**STA 4501**

HLT

# **ADDITION OF TWO 16 – BIT NUMBERS**

3. To write an assembly language program for adding two 16 bit numbers using 8085 micro processor.

| Address | Label | Mnemonics |               | Hex Code | Comments                   |

|---------|-------|-----------|---------------|----------|----------------------------|

| 4500    |       | MVI       | C,00          | 0E       | $C = 00_H$                 |

| 4501    |       |           |               | 00       |                            |

| 4502    |       | LHLD      | 4800          | 2A       | HL – 1 <sup>st</sup> No.   |

| 4503    |       |           |               | 00       |                            |

| 4504    |       |           |               | 48       |                            |

| 4505    |       | XCHG      |               | EB       | HL – DE                    |

| 4506    |       | LHLD      | 4802          | 2A       | HL - 2 <sup>na</sup> No.   |

| 4507    |       |           |               | 02       |                            |

| 4508    |       |           |               | 48       |                            |

| 4509    |       | DAD       | D             | 19       | Double addition DE +<br>HL |

| 450A    |       | JNC       | Ahead<br>450E | D2       | If $Cy = 0$ , G0 to 450E   |

| 450B    |       |           |               | 0E       |                            |

| 450C    |       |           |               | 45       |                            |

| 450D    |       | INR       | С             | 0C       | C = C + 01                 |

| 450E    | AHEAD | SHLD      | 4804          | 22       | HL - 4804 (sum)            |

| 450F    |       |           |               | 04       |                            |

| 4510    |       |           |               | 48       |                            |

| 4511    |       | MOV       | C,A           | 79       | Cy-A                       |

| 4512    |       | STA       | 4806          | 32       | Cy - 4806                  |

| 4513    |       |           |               | 06       |                            |

| 4514    |       |           |               | 48       |                            |

| 4515    |       | HLT       |               | 76       | Stop excution              |

# SUM OF DATAS

4. To write an assembly language program to calculate the sum of datas using 8085 microprocessor

| Address | Label | Mnemonics   | Hex Code   | Comments                     |

|---------|-------|-------------|------------|------------------------------|

| 4100    |       | LDA 4200    | 3A 00,42   | Load the accumulator with    |

|         |       |             |            | number of values             |

| 4103    |       | MOV B,A     | 4F         | Move it from A to C          |

| 4104    |       | LXI H, 4201 | 21,01,42   | Load the starting address of |

|         |       |             |            | data array                   |

| 4107    |       | SUB A       | 97         | Intialise 'A' as 00          |

| 4108    |       | MOV B,A     | 47         | Intialise 'B' as 00          |

| 4109    | Loop  | ADD M       | 86         | Add the previous sum with    |

|         |       |             |            | next data                    |

| 410A    |       | JNC Skip    | D2, 0E, 41 | Jump on if no carry          |

| 410D    |       | INR B       | 04         | Increment carry by one       |

| 410E    | Skip  | INX H       | 23         | Increment pointer for next   |

|         |       |             |            | data                         |

| 410F    |       | DCR C       | 0D         | Decrement 'C' by one         |

| 4110    |       | JNZ Loop    | C2, 09, 41 | Jump if not zero             |

| 4113    |       | STA 4400    | 32,00,44   | Store the sum in             |

|         |       |             |            | accumulator                  |

| 4116    |       | MOV A,B     | 78         | Move the value of carry to A |

|         |       |             |            | from B                       |

| 4117    |       | STA 4401    | 32,01,44   | Store the carry in memory    |

| 411A    |       | HLT         | 76         | End of program               |

# **SUBTRACTION OF TWO 8 BIT NUMBERS**

5. To write a assembly language program for subtracting 2 bit (8) numbers by using- 8085

| Address | Label | Mnemonics | Hex Code     | Comments                                     |

|---------|-------|-----------|--------------|----------------------------------------------|

| 4100    |       | MVI C,00  | OE, 00       | Initialize the carry as zero                 |

| 4102    |       | LDA 4300  | 3A, (00, 43) | Load the first 8 bit data into the           |

|         |       |           |              | accumulator                                  |

| 4105    |       | MOV, B,A  | 47           | Copy the value into register 'B'             |

| 4106    |       | LDA 4301  | 3A, (01, 43) | Load the 2 <sup>nd</sup> 8 bit data into the |

|         |       |           |              | accumulator                                  |

| 4109    |       | SUB B     | 90           | Subtract both the values                     |

| 410A    | Loop  | INC       | D2, 0E, 41   | Jump on if no borrow                         |

| 410D    |       | INR C     | OC           | If borrow is there, increment it by          |

|         |       |           |              | one                                          |

| 410E    | Loop  | CMA       | 2 <b>F</b>   | Compliment of 2 <sup>nd</sup> data           |

| 410F    |       | ADI, 01   | 6, 01        | Add one to 1's compliment of 2nd             |

|         |       |           |              | data                                         |

| 4111    |       | STA 4302  | 32,02,43     | Store the result in accumulator              |

| 4114    |       | MOV A,C   | 79           | Moul the value of borrow into the            |

|         |       |           |              | accumulator                                  |

| 4115    |       | STA 4303  | 32,03,43     | Store the result in accumulator              |

| 4118    |       | HLT       | 76           | Stop Program execution                       |

# **SUBTRACTION OF TWO 16 BIT NUMBERS**

6. To write an assembly language program for subtracting two 16 bit numbers using 8085 microprocessor kit.

| Address | Label | Mnemonics |      | Hex Code | Comments               |

|---------|-------|-----------|------|----------|------------------------|

| 4500    |       | MVI       | C,00 | 0E       | $C = 00_H$             |

| 4501    |       |           |      | 00       |                        |

| 4502    |       | LHLD      | 4800 | 2A       | $L - 1^{st} No.$       |

| 4503    |       |           |      | 00       |                        |

| 4504    |       |           |      | 48       |                        |

| 4505    |       | XLHG      |      | EB       | HL – DE                |

| 4506    |       | LHLD      | 4802 | 2A       | $HL - 2^{n\alpha} No.$ |

| 4507    |       |           |      | 02       |                        |

| 4508    |       |           |      | 48       |                        |

| 4509    |       | MOV       | A,E  | 7B       | LSB of '1' to 'A'      |

| 450A    |       | SUB       | L    | 95       | A - A - L              |

| 450B    |       | STA       | 4804 | 32       | A – memory             |

| 450C    |       |           |      | 04       |                        |

| 450D    |       |           |      | 48       |                        |

| 450E    |       | MOV       | A,D  | 7A       | MSB of 1 to A          |

| 450F    |       | SBB       | H    | 9C       | A- A – H               |

| 4510    |       | STA       | 4805 | 32       | A – memory             |

| 4511    |       |           |      | 05       |                        |

| 4512    |       |           |      | 48       |                        |

| 4513    |       | HLT       |      | 76       | Stop execution         |

# **Multiplication ; No carry**

- LDA 2000 // Load multiplicant to accumulator

- MOV B,A // Move multiplicant from A(acc) to B register

- LDA 2001 // Load multiplier to accumulator

- MOV C,A // Move multiplier from A to C

- MVI A,00 // Load immediate value 00 to a

- L: ADD B // Add B(multiplier) with A

- DCR C // Decrement C, it act as a counter

- JNZ L // Jump to L if C reaches 0

- STA 2010 / / Store result in to memory

- HLT // End

### **Multiplication ; With carry**

7.Write an assembly program to multiply a number by

8

**MVI C,OO** LXI H, 4100 MOV B, M INX H MOV A, M DCR B LOOP 2 ADD M JNC LOOP1 INR C LOOP 1 DCR B LOOP2 INZ **STA 4500** HLT

# **Multiplication**

| Address | Label | Mnemonics | Hex Code   | Comments                               |  |  |  |  |  |  |

|---------|-------|-----------|------------|----------------------------------------|--|--|--|--|--|--|

| 4100    |       | LDA 4500  | 3A, 00, 45 | Load the first 8 bit number            |  |  |  |  |  |  |

| 4103    |       | MOV B,A   | 47         | Move the 1 <sup>st</sup> 8 bit data to |  |  |  |  |  |  |

|         |       |           |            | register 'B'                           |  |  |  |  |  |  |

| 4104    |       | LDA 4501  | 3A, 01, 45 | Load the 2 <sup>nd</sup> 16 it number  |  |  |  |  |  |  |

| 4107    |       | MOV C,A   | 4F         | Move the 2 <sup>nd</sup> 8 bit data to |  |  |  |  |  |  |

|         |       |           |            | register 'C'                           |  |  |  |  |  |  |

| 4108    |       | MVI A, 00 | 3E, 00     | Intialise the accumulator as           |  |  |  |  |  |  |

|         |       |           |            | zero                                   |  |  |  |  |  |  |

| 410A    |       | MVI D, 00 | 16,00      | Intialise the carry as zero            |  |  |  |  |  |  |

| 410C    |       | ADD B     | 80         | Add the contents of 'B' and            |  |  |  |  |  |  |

|         |       |           |            | accumulator                            |  |  |  |  |  |  |

| 410D    |       | INC       | D2 11, 41  | Jump if no carry                       |  |  |  |  |  |  |

| 4110    |       | INR D     | 14         | Increment carry if there is            |  |  |  |  |  |  |

| 4111    |       | DCR C     | OD         | Decrement the value 'C'                |  |  |  |  |  |  |

| 4112    |       | JNZ       | C2 0C, 41  | Jump if number zero                    |  |  |  |  |  |  |

| 4115    |       | STA 4502  | 32 02, 45  | Store the result in                    |  |  |  |  |  |  |

|         |       |           |            | accumulator                            |  |  |  |  |  |  |

| 4118    |       | MOV A,D   | 7 <b>A</b> | Move the carry into                    |  |  |  |  |  |  |

|         |       |           |            | accumulator                            |  |  |  |  |  |  |

| 4119    |       | STA 4503  | 32,03,45   | Store the result in                    |  |  |  |  |  |  |

|         |       |           |            | accumulator                            |  |  |  |  |  |  |

| 411C    |       | HLT       | 76         | Stop the program execution             |  |  |  |  |  |  |

### DIVISION OF TWO 8 – BIT NUMBERS

• To write an assembly language program for dividing two 8 bit numbers using microprocessor

| Address | Label  | Mnemonics     | Hex Code   | Comments                                              |  |  |  |  |  |

|---------|--------|---------------|------------|-------------------------------------------------------|--|--|--|--|--|

| 4100    |        | MVI C, 00     | 0E, 00     | Intialise Quotient as zero                            |  |  |  |  |  |

| 4102    |        | LDA, 4500     | 3A 00, 45  | Get the 1 <sup>st</sup> data                          |  |  |  |  |  |

| 4105    |        | MOV B,A       | 47         | Copy the 1 <sup>st</sup> data into                    |  |  |  |  |  |

|         |        |               |            | register 'B'                                          |  |  |  |  |  |

| 4106    |        | LDA, 4501     | 3A 01, 45  | Get the 2 <sup>na</sup> data                          |  |  |  |  |  |

| 4109    |        | CMP B         | B8         | Compare the 2 values                                  |  |  |  |  |  |

| 410A    |        | JC (LDP)      | DA 12,41   | Jump if dividend lesser than                          |  |  |  |  |  |

|         |        |               |            | divisor                                               |  |  |  |  |  |

| 410D    | Loop 2 | SUB B         | 90         | Subtract the 1 <sup>st</sup> value by 2 <sup>nd</sup> |  |  |  |  |  |

|         |        |               |            | value                                                 |  |  |  |  |  |

| 410E    |        | INR C         | 0C         | Increment Quotient (410D)                             |  |  |  |  |  |

| 410F    |        | JMP (LDP, 41) | C3, 0D, 41 | Jump to Loop 1 till the value                         |  |  |  |  |  |

|         |        |               |            | of dividend becomes zero                              |  |  |  |  |  |

| 4112    | Loop 1 | STA 4502      | 32 02,45   | Store the value in                                    |  |  |  |  |  |

|         |        |               |            | accumulator                                           |  |  |  |  |  |

| 4115    |        | MOV A,C       | 79         | Move the value of remainder                           |  |  |  |  |  |

|         |        |               |            | to accumulator                                        |  |  |  |  |  |

| 4116    |        | STA 4503      | 32 03,45   | Store the remainder value in                          |  |  |  |  |  |

|         |        |               |            | accumulator                                           |  |  |  |  |  |

| 4119    |        | HLT           | 76         | Stop the program execution                            |  |  |  |  |  |

### **ASCENDING ORDER**

• 9. To write a program to sort given 'n' numbers in ascending

| Address | Label  | Mnemonics   | Hex Code   | Comments                    |  |  |  |  |

|---------|--------|-------------|------------|-----------------------------|--|--|--|--|

| 4100    |        | LDA 4500    | 3A, 00,45  | Load the number of values   |  |  |  |  |

| 4103    |        | MOV B,A     | 47         | Move it 'B' register        |  |  |  |  |

| 4104    |        | DCR B       | 05         | For (N-1) comparisons       |  |  |  |  |

| 4105    | Loop 3 | LXI H, 4500 | 21, 00,45  | Set the pointer for array   |  |  |  |  |

| 4108    |        | MOV C,M     | 4E         | Count for (N-1) comparisons |  |  |  |  |

| 4109    |        | DCR C       | 0D         | For (N-1) comparisons       |  |  |  |  |

| 410A    |        | INX H       | 23         | Increment pointer           |  |  |  |  |

| 410B    | Loop 2 | MOV A,M     | 7E         | Get one data in array 'A'   |  |  |  |  |

| 410C    |        | INX H       | 23         | Increment pointer           |  |  |  |  |

| 410D    |        | CMP M       | BE         | Compare next with           |  |  |  |  |

|         |        |             |            | accumulator                 |  |  |  |  |

| 410E    |        | JC          | DA, 16, 41 | If content less memory go   |  |  |  |  |

|         |        |             |            | ahead                       |  |  |  |  |

| 4111    |        | MOV D,M     | 56         | If it is greater than       |  |  |  |  |

|         |        |             |            | interchange it              |  |  |  |  |

| 4112    |        | MOV M,A     | 77         | Memory content              |  |  |  |  |

| 4113    |        | DCX H       | 2 <b>B</b> | Exchange the content of     |  |  |  |  |

|         |        |             |            | memory pointed by 'HL' by   |  |  |  |  |

|         |        |             |            | previous location           |  |  |  |  |

| 4114    |        | MOV M,D     | 72         | One in by 'HL' and previous |  |  |  |  |

|         |        |             |            | location                    |  |  |  |  |

| 4115    |        | INX H       | 23         | Increment pointer           |  |  |  |  |

| 4116    | Loop 1 | DCR C       | 0D         | Decrement 'C' register      |  |  |  |  |

| 4117    |        | JNZ Loop 1  | C2, 0B, 41 | Repeat until 'C' is zero    |  |  |  |  |

| 411A    |        | DCR B       | 05         | Decrement in 'B' values     |  |  |  |  |

| 411B    |        | JNZ Loop 2  | C2, 05, 41 | Repeat till 'B' is zero     |  |  |  |  |

| 411E    |        | HLT         | 76         | Stop the program execution  |  |  |  |  |

### **DESCENDING ORDER**

• 10. To write a program to sort given 'n' numbers in descending order

| Address | Label  | Mnemonics   | Hex Code   | Comments                       |  |  |  |  |  |

|---------|--------|-------------|------------|--------------------------------|--|--|--|--|--|

| 4100    |        | LDA 4500    | 3A, 00,45  | Load the number of values      |  |  |  |  |  |

|         |        |             |            | in accumulator                 |  |  |  |  |  |

| 4103    |        | MOV B,A     | 47         | Move it to 'B' register        |  |  |  |  |  |

| 4104    |        | DCR B       | 05         | For (N-1) comparisons          |  |  |  |  |  |

| 4105    | Loop 3 | LXI H, 4500 | 21, 00,45  | Set the pointer for array      |  |  |  |  |  |

| 4108    |        | MOV C,M     | 4E         | Count for (N-1) comparisons    |  |  |  |  |  |

| 4109    |        | DCR C       | 0D         | For (N-1) comparisons          |  |  |  |  |  |

| 410A    |        | INX H       | 23         | Increment pointer              |  |  |  |  |  |

| 410B    | Loop 2 | MOV A,M     | 7E         | Get one data from array        |  |  |  |  |  |

| 410C    |        | INX H       | 23         | Increment pointer              |  |  |  |  |  |

| 410D    |        | CMP M       | BE         | Compare next with number       |  |  |  |  |  |

| 410E    |        | ICE, Loop 1 | D2, 16,41  | If content 'A' is greater than |  |  |  |  |  |

|         |        | _           |            | content of 'HL' pair           |  |  |  |  |  |

| 4111    |        | MOV D,M     | 56         | If it is greater than          |  |  |  |  |  |

|         |        |             |            | interchange the datas          |  |  |  |  |  |

| 4112    |        | MOV M,A     | 77         | Accumulator to memory          |  |  |  |  |  |

|         |        |             |            | value                          |  |  |  |  |  |

| 4113    |        | DCX H       | 2B         | Decrement memory pointer       |  |  |  |  |  |

| 4114    |        | MOV M,D     | 72         | Move the old to 'HL' and       |  |  |  |  |  |

|         |        |             |            | previous location              |  |  |  |  |  |

| 4115    |        | INX H       | 23         | Increment pointer              |  |  |  |  |  |

| 4116    | Loop 1 | DCR C       | 0D         | Decrement 'C' register         |  |  |  |  |  |

| 4117    |        | JNZ Loop 2  | C2, 0B, 41 | Repeat till 'C' is zero        |  |  |  |  |  |

| 411A    |        | DCR B       | 05         | Decrement in 'B' values        |  |  |  |  |  |

| 411B    |        | JNZ Loop 3  | C2, 05, 41 | Jump to loop till the value of |  |  |  |  |  |

|         |        | _           |            | 'B' be                         |  |  |  |  |  |

| 411E    |        | HLT         | 76         | Stop the program execution     |  |  |  |  |  |

# Program

11.Write an Assembly Language Program to transfer a block of data from a series of locations to other.

• MVI C, 0AH ; Initialize counter i.e no. of bytes

Store the count in Register C, ie ten

LXI H, 2200H ; Initialize source memory pointer Data Starts from 2200 location

• LXI D, 2300H ; Initialize destination memory pointer

BK: MOV A, M ; Get byte from source memory block i.e 2200 to accumulator.

• STAX D ; Store byte in the destination memory block i.e 2300 as stored in D-E pair

# Program

- INX H

- INX D

- DCR C

- JNZ BK

- HLT

- ; Increment source memory pointer

- ; Increment destination memory pointer

- ; Decrement counter to keep track of bytes moved

- ; If counter 0 repeat steps

- ;Terminate program

### Largest Number

• Write an Assembly Language Program to find a largest number.

LXI H, 4500

MOV A, M

INX H

CMP M

JNC LOOP 1

JMP LOOP 2

- LOOP1 STA 4500

- LOOP2 MOVA, M

**STA 4500**

HLT

### **Smallest Number**

• Write an Assembly Language Program to find a smallest number.

LXI H, 4500 MOVA, M **INX H CMP** M JC LOOP1 LOOP 2 JMP LOOP1 **STA 4500** LOOP2 MOVA, M **STA 4500** HLT

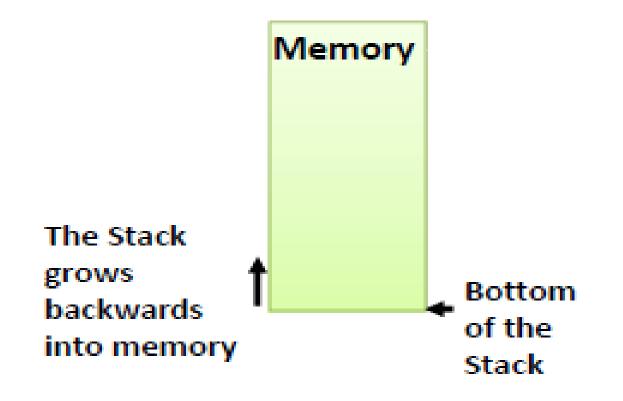

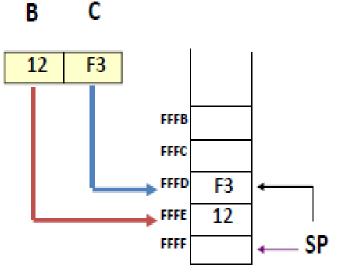

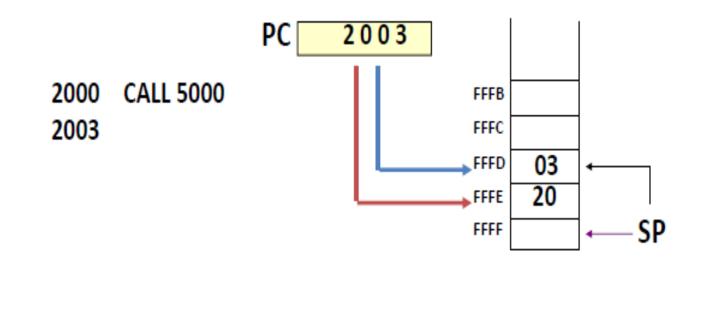

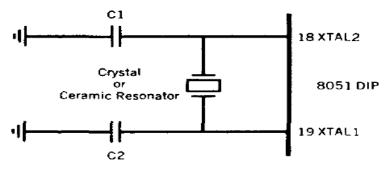

# **STACK AND SUBROUTINE**

### STACK

- The **stack is an area of memory** identified by the programmer for temporary storage of information.

- The stack is a **LIFO** structure.

- The stack normally **grows backwards into memory**.

- **Programmer can defines the bottom of (SP) the stack** and the stack grows up into reducing address range.

### STACK

- Stack is defined by setting the SP (Stack Pointer) register.

- LXI SP, FFFFH, This sets SP to location FFFFH (end of memory for 8085).

### STACK

- Save information by **PUSHing onto STACK**

- Retrieved from STACK by POPing it off.

- PUSH and POP work with register pairs only.

- Example "PUSH B"

- – Decrement SP, Copy B to (SP-1)

- – Decrement SP, Copy C to (SP-1)

- Example "POP B"

- – Copy (SP+1) to C, Increment SP

- – Copy (SP+1) to B, Increment SP

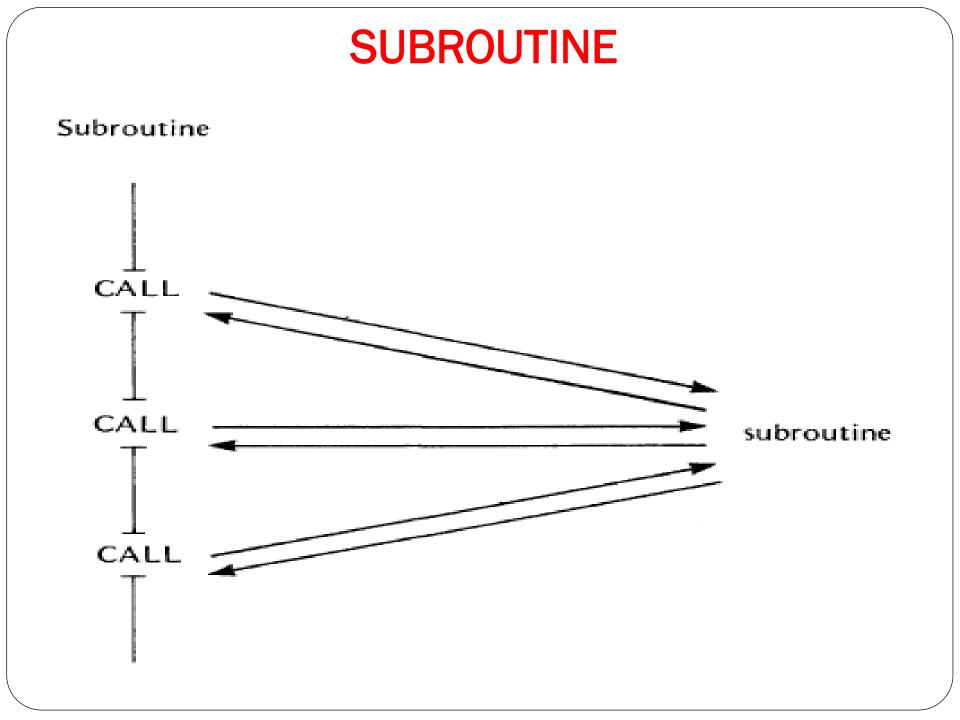

# SUBROUTINE

- A subroutine is a group of instructions that is used repeatedly in different places of the program.

- It can be grouped into a **subroutine and call from the different locations.**

- The **CALL instruction** is used to redirect program execution to the subroutine.

- The **RET instruction** is used to return the execution to the calling routine.

# SUBROUTINE

- You must set the SP correctly before using CALL

- CALL 5000H

- – Push the PC value onto the stack

- - Load PC with 16-bit address supplied CALL ins.

- RET : Load PC with stack top; POP PC

# **SUBROUTINE**

- SUBRTN:

- PUSH PSW

- PUSH B

- PUSH D

- PUSH H

- subroutine coding

- POP H

- POP D

- POP B

- POP PSW

- RETURN

# MODULE 3 INTERFACING

#### • <u>SORT ARRAY OF DATA IN</u> <u>ASCENDING ORDER</u>

LDA 2100 MOV B,A DCR B LOOP 2: LXI H,2100 MOV C,M DCR C INX H LOOP 1: MOV A,M INX H CMP M **JC AHEAD** MOV D,M MOV M,A DCX H MOV M,D INX H AHEAD: DCR C JNZ LOOP 1 DCR B JNZ LOOP 2 HLT

#### SORT ARRAY OF DATA IN DESCENDING ORDER

LDA 2100 MOV B,A DCR B LOOP 2: LXI H,2100 MOV C,M DCR C INX H LOOP 1: MOV A,M INX H CMP M JNC AHEAD MOV D,M MOV M.A DCX H MOV M,D INX H AHEAD: DCR C JNZ LOOP 1 DCR B JNZ LOOP 2 HLT

ICET

| CONVERSION OF BCD NUMBER TO | CONVERSION OF HEXADECIMAL TO BCD |

|-----------------------------|----------------------------------|

| HEXADECIMAL                 | MVI B ,00                        |

| LDA 2100                    | MOV C,B                          |

| MOV B,A                     | LDA 2100                         |

| ANI OF                      | SKIP : CPI 64                    |

| MOV C,A                     | JC LOOP                          |

| MOV A,B                     | SUI 64                           |

| ANI FO                      | INR B                            |

| JZ SKIP                     | JMP SKIP                         |

| RRC                         | LOOP : CPI 0A                    |

| RRC                         | JC UNIT                          |

| RRC                         | SUI 0A                           |

| RRC                         | INR C                            |

| MOV D,A                     | JMP LOOP                         |

| XRA                         | UNIT : MOV D,A                   |

| LOOP: ADI 0A                | MOV A,B                          |

| DCR D                       | STA 2200                         |

| JNZ LOOP                    | MOV A,C                          |

| SKIP : ADD C                | RLC                              |

| STA 2200                    | RLC                              |

| HLT                         | RLC                              |

|                             | RLC                              |

|                             | ADD D                            |

|                             | STA 2201                         |

| 93 ICET                     | HLT                              |

|                             |                                  |

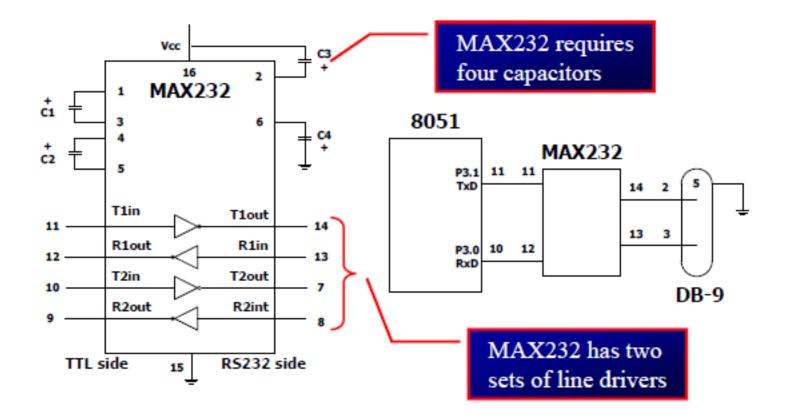

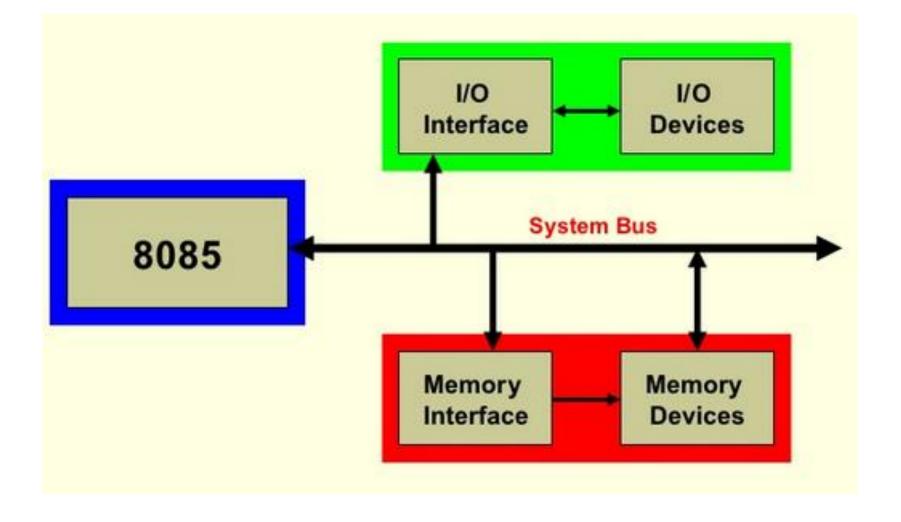

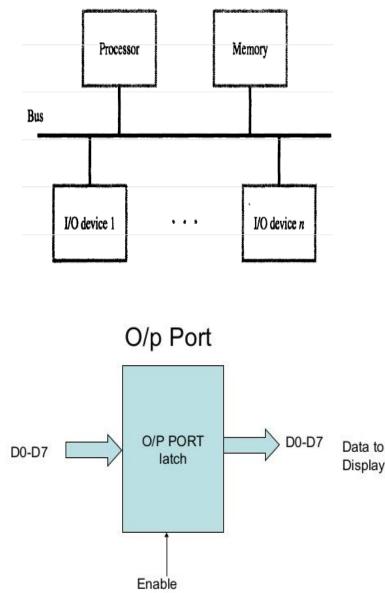

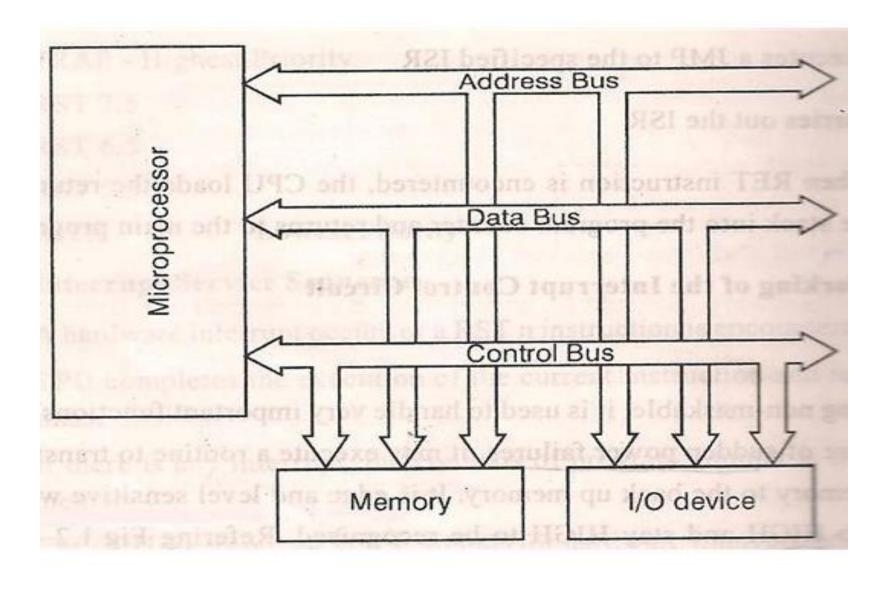

# INTERFACING

- Interfacing a microprocessor is to connect it with various peripherals to perform various operations to obtain a desired output.

- **Memory Interfacing** and **I/O Interfacing** are the two main types of interfacing.

- Memory Interfacing is used when the microprocessor needs to access memory frequently for reading and writing data stored in the memory . It is used when reading/writing to a specific register of a memory chip.

- I/O Interfacing is achieved by connecting keyboard(input) and display monitors(output) with the microprocessor.

## Memory and I/O addressing

# Memory

- Integral part of microprocessor

- •Primary memory:rom,eprom, static ram etc

- •Secondary memory: hard disc

- •One is Program memory.

- •This is where the program is located.

- •ROM

### •Another is Data memory.

- •This is where data, that might be used by the program, is located.

- •RAM

### memory

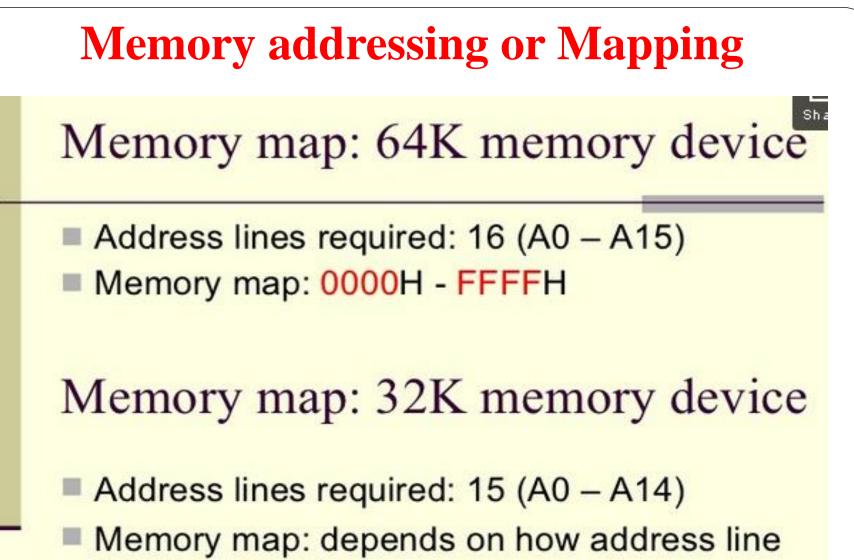

# **Memory addressing or Mapping**

- 8085 has 16-bit Address Bus

- The complete address space is thus given by the range of addresses 0000H – FFFFH

- The range of addresses allocated to a memory device is known as its memory map

# **Memory addressing or Mapping**

| A <sub>15</sub> | 5 A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | $A_{10}$ | Ag | $A_8$ | A <sub>7</sub> | $A_6$ | A5 | A4 | A <sub>3</sub> | $A_2$ | $A_1$ | $A_0$ | Hex Address |

|-----------------|-------------------|-----------------|-----------------|-----------------|----------|----|-------|----------------|-------|----|----|----------------|-------|-------|-------|-------------|

| 0               | 0                 | 0               | 0               | 0               | 0        | 0  | 0     | 0              | 0     | 0  | 0  | 0              | 0     | 0     | 0     | 0000H       |

| 0               | 0                 | 0               | 0               | 0               | 0        | 0  | 0     | 0              | 0     | 0  | 0  | 0              | 0     | 0     | 1     | 0001H       |

| 0               | 0                 | 0               | 0               | 0               | 0        | 0  | 0     | 0              | 0     | 0  | 0  | 0              | 0     | 1     | 0     | 0002H       |

| -               |                   |                 | -               | -               |          | -  | -     | -              | -     | -  |    | -              | -     | -     |       |             |

| -               |                   |                 | -               | -               |          |    | -     | -              | -     | -  |    | -              | -     | -     |       |             |

| 1               | 1                 | 1               | 1               | 1               | 1        | 1  | 1     | 1              | 1     | 1  | 1  | 1              | 1     | 1     | 0     | FFFEH       |

| 1               | 1                 | 1               | 1               | 1               | 1        | 1  | 1     | 1              | 1     | 1  | 1  | 1              | 1     | 1     | 0     | FFFFH       |

A15 is connected

# **Memory interfacing**

AO-A14

AO-A15

A15

\_\_\_\_\_

7FFFH

FFFFH

15

16

32kB

64kB

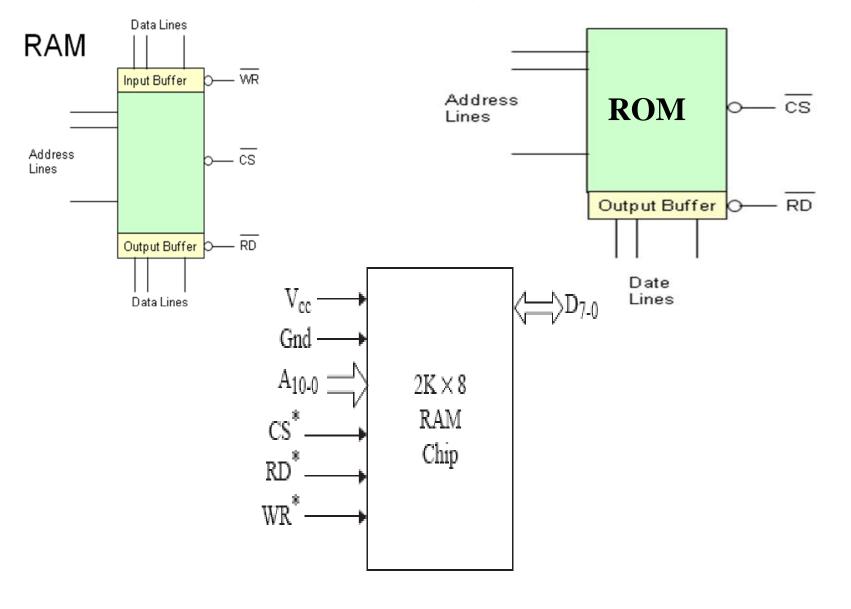

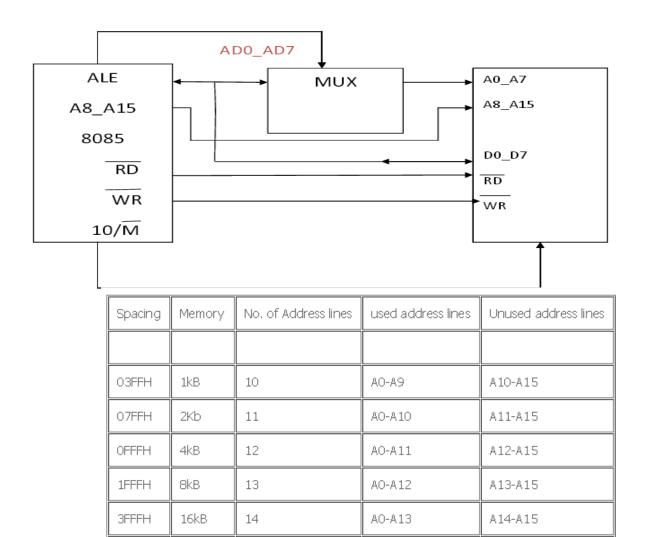

# Memory interfacing 64KB

•Interface a 8085 system in which full memory space utilized for EPROM memory

# Memory interfacing 64KB

•In this system the entire 16 address lines of the processor are connected to address input pins of memory IC.

• The chip select (CS) pin of EPROM is permanently tied to logic low (i.e., tied to ground).

• Since the processor is connected to EPROM, the active low RD pin is connected to active low output enable pin of EPROM.

• The range of address for EPROM is 0000H to FFFFH.

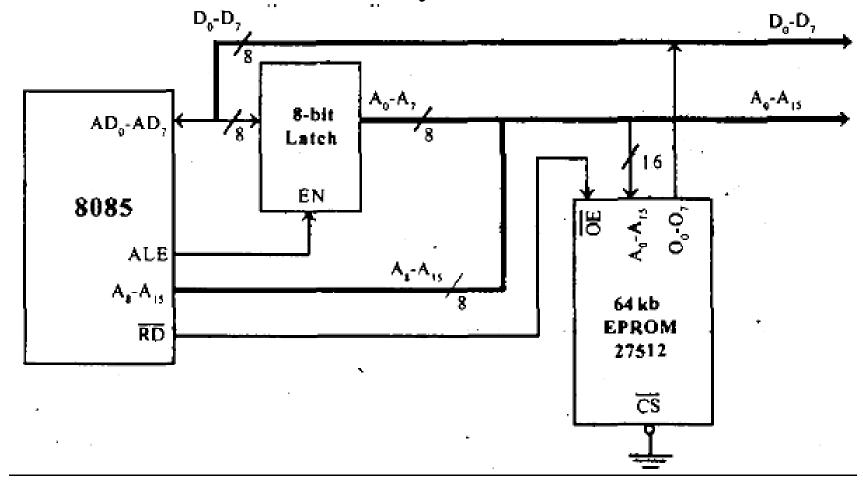

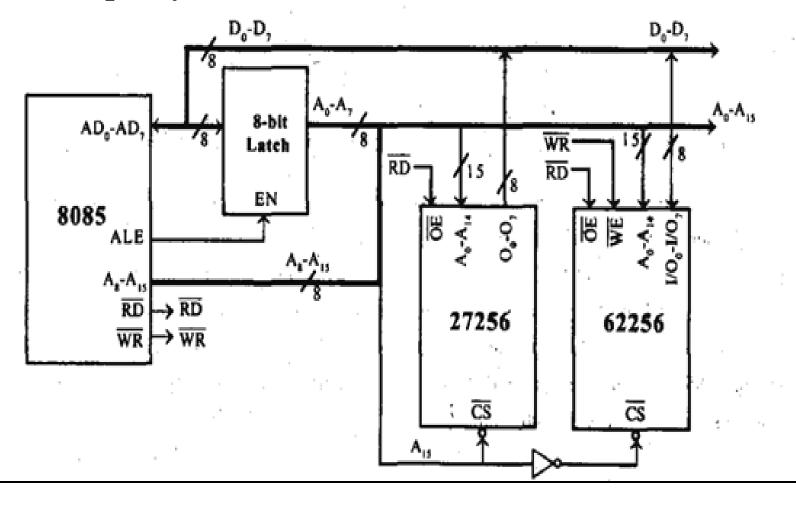

# Two 32 kb Memory interfacing

•Interface a system 8085 in which the available memory 64 k is equally divided between EPROM &RAM

# Two 32 kb Memory interfacing

- Implement 32kb memory capacity of EPROM using single IC 27256.

- 32kb RAM capacity is implemented using single IC 62256.

• The 32kb memory requires 15 address lines and so the address lines A0 - A14 of the processor are connected to 15 address pins of both EPROM and RAM.

# Two 32 kb Memory interfacing

- The 32kb memory requires 15 address lines and so the address lines A0 A14 of the processor are connected to 15 address pins of both EPROM and RAM.

- The unused address line A15 is used as to chip select. If A15 is 1, it select RAM and If A15 is 0, it select EPROM.

- The memory used is both Ram and EPROM, so the low RD and WR pins of processor are connected to low WE and OE pins of memory respectively.

- The address range of EPROM will be 0000H to 7FFFH and that of RAM will be 7FFFH to FFFFH.

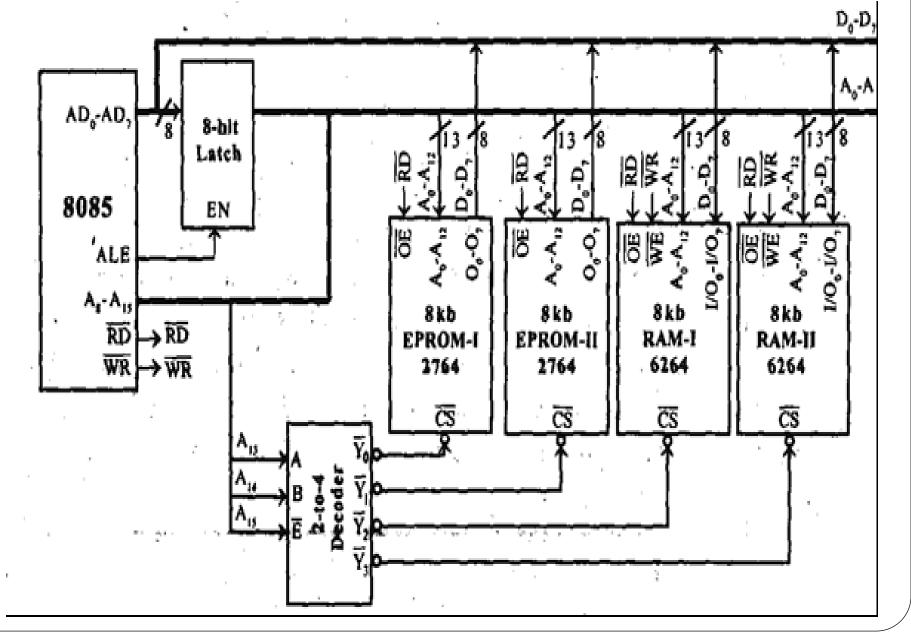

## 32kb Memory interfacing using 4 "8 kb"

# 32kb Memory interfacing using 4 "8 kb"

- The total memory capacity is 32Kb. So, let two number of 8kb n memory be EPROM and the remaining two numbers be RAM.

- Each 8kb memory requires 13 address lines and so the address lines A0- A12 of the processor are connected to 13 address pins of all the memory.

- The address lines and A13 A14 can be decoded using a 2to-4 decoder to generate four chip select signals.

- These four chip select signals can be used to select one of the four memory IC at any one time.

- The address line A15 is used as enable for decoder.

### Multiple Memory interfacing

|                | Binary address          |             |             |                                    |             |             |              |                |      |      |                 |      |                |                |             |                |                      |

|----------------|-------------------------|-------------|-------------|------------------------------------|-------------|-------------|--------------|----------------|------|------|-----------------|------|----------------|----------------|-------------|----------------|----------------------|

| Device         | Decoder<br>enable/input |             |             | Input to address pins of memory IC |             |             |              |                |      |      | Hexa<br>address |      |                |                |             |                |                      |

|                | A,5                     | A,4         | A,3         | A <sub>12</sub>                    | Α,,         | A10         | Α,           | A <sub>8</sub> | А,   | Α,   | $A_{s}$         | A,   | A <sub>3</sub> | A <sub>2</sub> | А,          | A <sub>o</sub> |                      |

| 8kb            | 0                       | 000         | 000         | 000                                | 000         | 0000        | 000          | 000            | 000  | 000  | 000             | 000  | 000            | 0<br>0<br>0    | 0<br>0<br>1 | 010            | 0000<br>0001<br>0002 |

| EPROM - I      | -                       | :           | :           | :                                  | :           | -           | :            | :              |      |      |                 | :    | -              | :              | :           | :              |                      |

| •              | ò                       | ò           | ò           | i                                  | i           | i           | i.           | i              | i    | i    | i               | i    | i              | i              | i           | i              | 1FFF                 |

| 8kb            | 000                     | 0000        | 1<br>1<br>1 | 000                                | 0           | 0<br>0<br>0 | 0<br>0<br>0. | 000            | 0000 | 0000 | 000             | 000  | 000            | 000            | 0<br>0<br>1 | 0<br>1<br>0    | 2000<br>2001<br>2002 |

| EPROM - II     |                         | :           |             |                                    |             |             |              | •              |      |      | -               | -    | :              |                |             |                |                      |

|                | 0                       | ò           | i           | i                                  | ì           | ì           | ì            | i              | ì    | ì    | ì               | i    | i.             | ì              | i           | i              | 3FPF                 |

| 8kb<br>RAM - I | 0000                    | 1<br>1<br>1 | 000         | 000                                | 0<br>0<br>0 | 000         | 0000         | 000            | 000  | 000  | 000             | 000. | 000            | 000            | 0<br>0<br>1 | 010            | 4000<br>4001<br>4002 |

|                | ò                       | i           | ò           | i                                  | ì           | i           | i            | i              | i    | ì    | i ·             | i    | i              | i              | ì           | i              | 5FFF ·               |

| 8kb<br>RAM -11 | 000                     | 1           | 1           | 000                                | 000         | 000         | 000          | 000            | 0000 | 000  | 000             | 000  | 0<br>0<br>0    | 000            | 0           | 0<br>1<br>0    | 6000<br>6001<br>6002 |

|                | ò                       | i           | i           | i                                  | i           | i           | i            | i              | i    | i    | i               | i    | i              | i              | i           | į              | ZFFF                 |

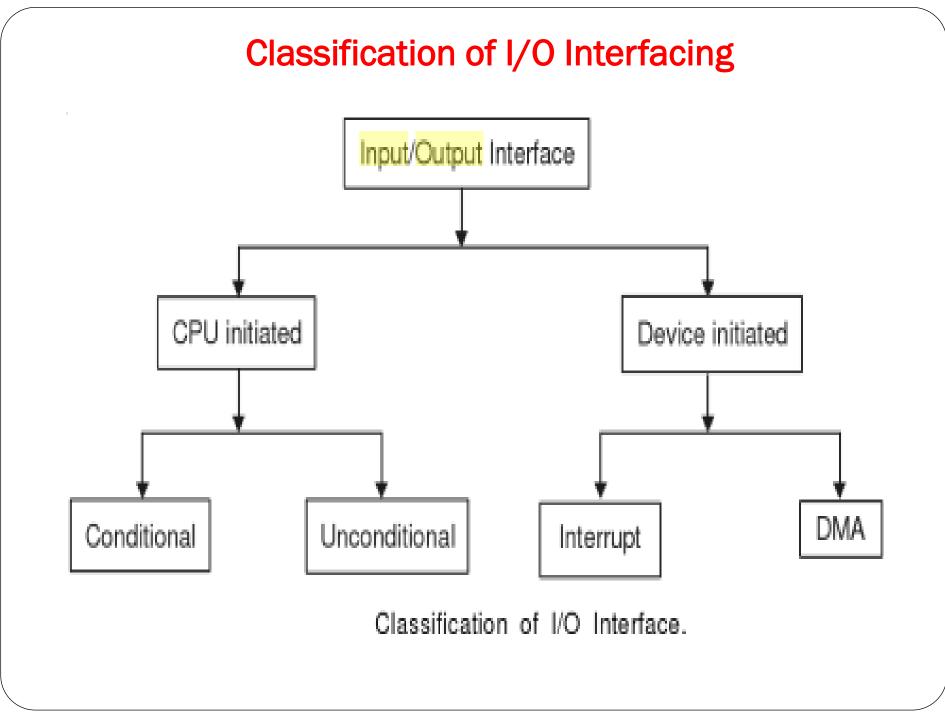

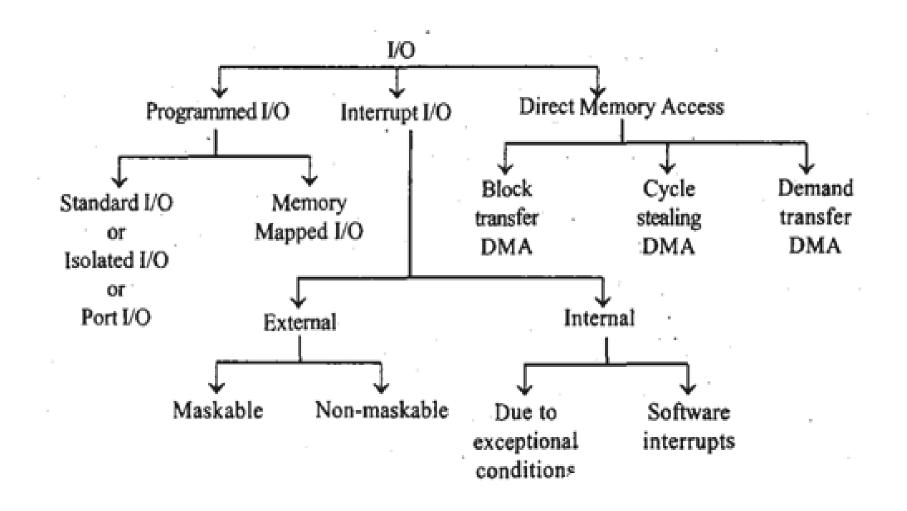

## **I/O addressing or Mapping**

# I/O interfacing techniques

I/O devices can be interfaced in two ways

- 1) I/O mapped I/O

- 2) Memory mapped I/O

## **I/O Addressing Schemes :comparison**

| Memory Mapping of I/O device                                                                                                                                                                                                    | I/O Mapping of I/O device                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                 | <ol> <li>8-bit addresses are provided for I/O devices.</li> <li>The devices are accessed by I/O read or I/O write cycle. During these cycles the 8-bit address is available on both low order address lines and high order address lines.</li> </ol> |

| 3.The I/O ports or peripherals can be treated<br>like memory locations and so all instructions<br>related to memory can be used for data<br>transfer between I/O device and the processor.                                      | processor.                                                                                                                                                                                                                                           |

| <ol> <li>In memory mapped ports the data can be<br/>moved from any register to ports and vice-<br/>versa.</li> </ol>                                                                                                            | <ol> <li>In I/O mapped ports the data transfer can take<br/>place only between the accumulator and ports.</li> </ol>                                                                                                                                 |

| 5. When memory mapping is used for I/O<br>devices, the full memory address space cannot<br>be used for addressing memory. Hence<br>memory mapping is useful only for small<br>systems, where the memory requirement is<br>less. | 5. When I/O mapping is used for I/O devices<br>then the full memory address space can be<br>used for addressing memory. Hence it is<br>suitable for systems which requires large<br>memory capacity.                                                 |

| <ol> <li>In memory mapped I/O devices, a large<br/>number of I/O ports can be interfaced.</li> </ol>                                                                                                                            | 6. In I/O mapping only 256 ports<br>(2 <sup>8</sup> = 256) can be interfaced.                                                                                                                                                                        |

| <ol> <li>For accessing the memory mapped devices,<br/>the processor executes memory read or write</li> </ol>                                                                                                                    | 7. For accessing the I/O mapped devices, the                                                                                                                                                                                                         |

| cycle. During this cycle IO/ $\overline{M}$ is asserted low (IO/ $\overline{M} = 0$ ).                                                                                                                                          | During this cycle IO/ $\overline{M}$ is asserted high (IO/ $\overline{M} = 1$ ).                                                                                                                                                                     |

#### **BASIC INTERFACING IN MICROPROCESSOR**

#### **BASIC INTERFACING IN MICROPROCESSOR**

- In memory interfacing, 8 bit data line, 16 bit address line, control signals are connected to corresponding lines of memory IC.

- In I/O device interfacing, 8 bit data line, only 8 bit address line , control signals are connected to corresponding lines of I/O devices.

#### Data Transfer using I/O STRUCTURE

#### Data Transfer using I/O STRUCTURE

- There are **three major types of data transfer** between the microprocessor and I/O device.

- Programmed I/O : In programmed I/O the **data transfer is accomplished through an I/O port** and controlled by software.

- Interrupt driven I/O : In interrupt driven I/O, the I/O device will interrupt the processor, and initiate data transfer.

- Direct memory access (DMA) : In DMA, the data transfer between memory and I/O can be **performed by bypassing the microprocessor.**

# **INTERFACING OF INPUT AND OUTPUT DEVICE** I/P device Tri state Buffer O/P D0- D7 device Address decoder

AD0-AD7

Logic

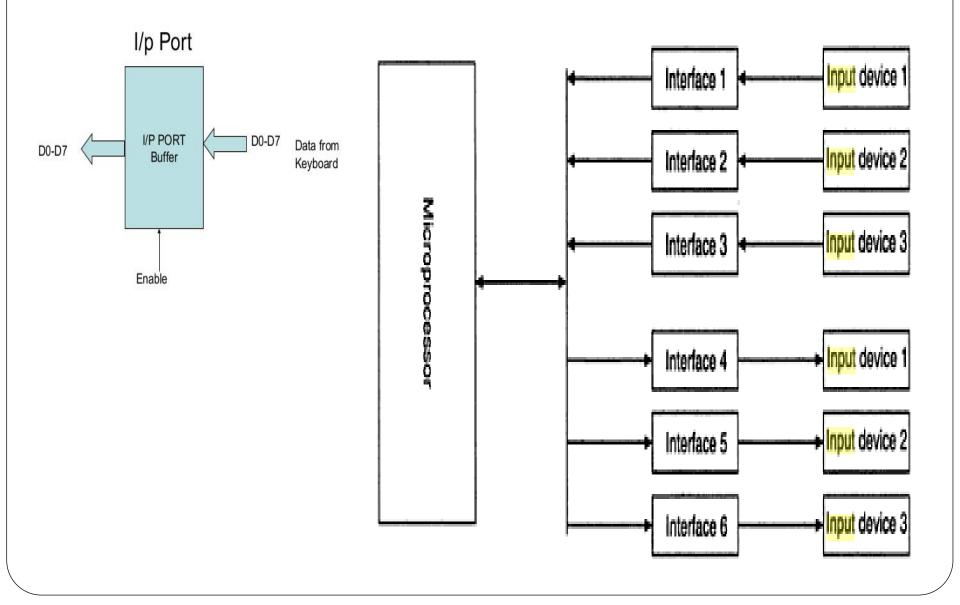

#### **INTERFACING OF INPUT AND OUTPUT DEVICE**

•I/O mapped or programmed interfacing scheme is commonly used. The data lines are connected to the I/O devices through Tri-state buffer. Tri- State buffer is enabled from address decoder logic.

•The address decoder logic **makes an enable signal** according to the address data coming from microprocessor.

• These address is the address of a ports.

•IN and OUT instruction is used for data transfer

- •Eg. IN ,Port address; IN 02

- OUT, Port address; OUT 03

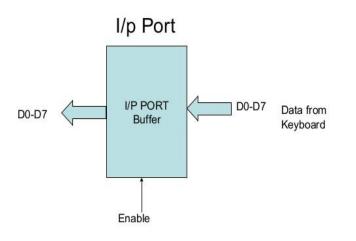

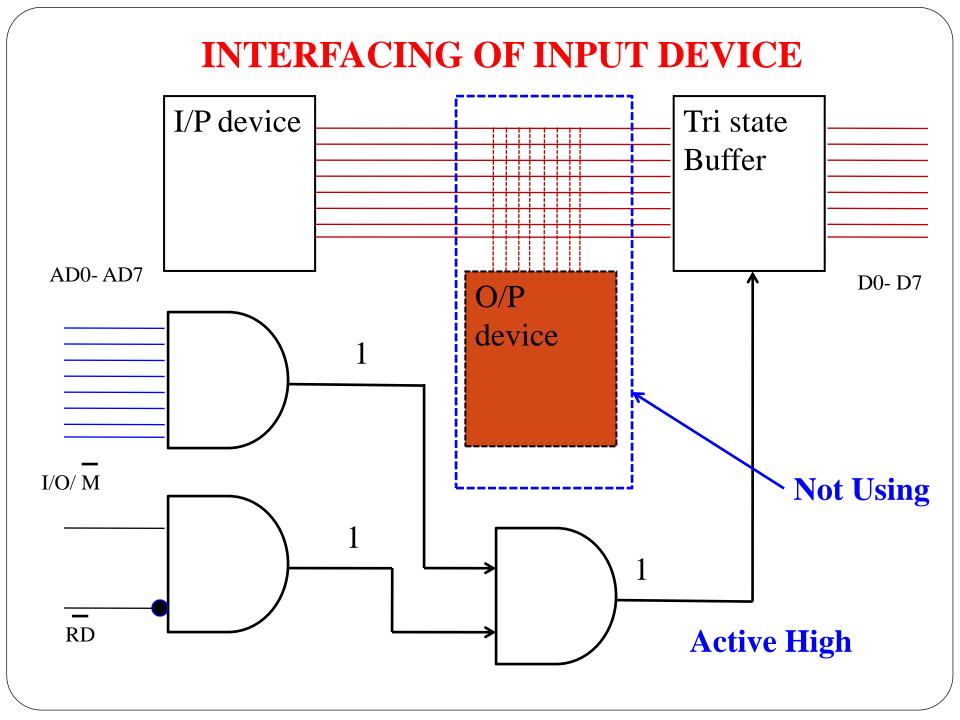

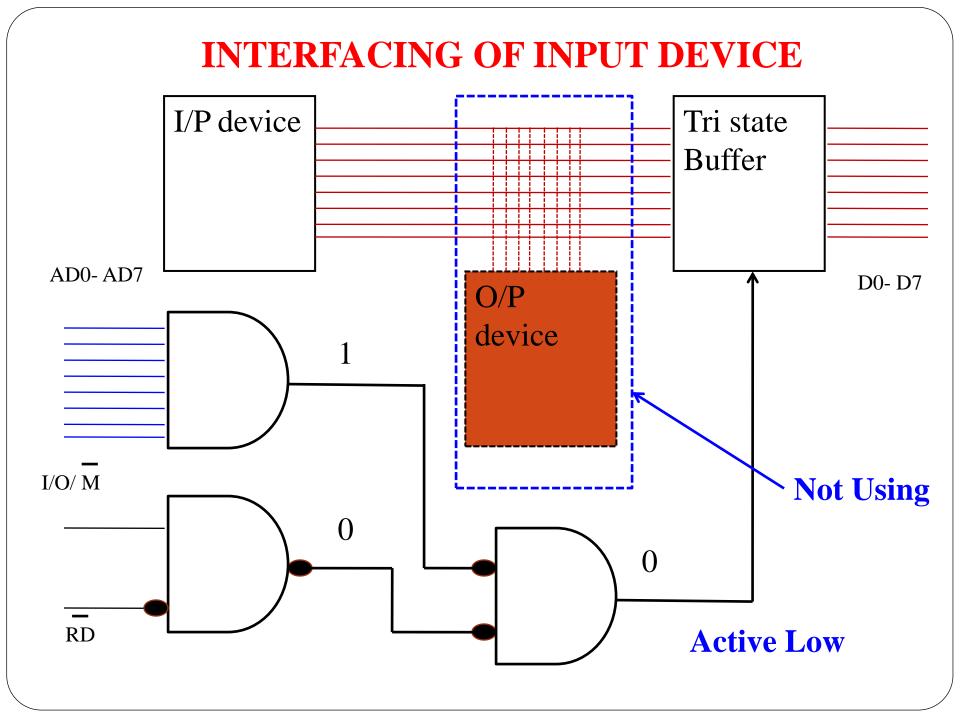

### **INTERFACING OF INPUT DEVICE**

### **INTERFACING OF INPUT DEVICE**

- The address lines are decoded to generate a signal that is active when the particular port is being accessed.

- An **IORD signal is generated by combining the IO/M and the RD** signals from the microprocessor.

- Lets **choose I/O port 0FH** for the Input devices.

- So, the buffers must be enabled when:

- RD = 0IO/M = 1 A0-A8= 0FH

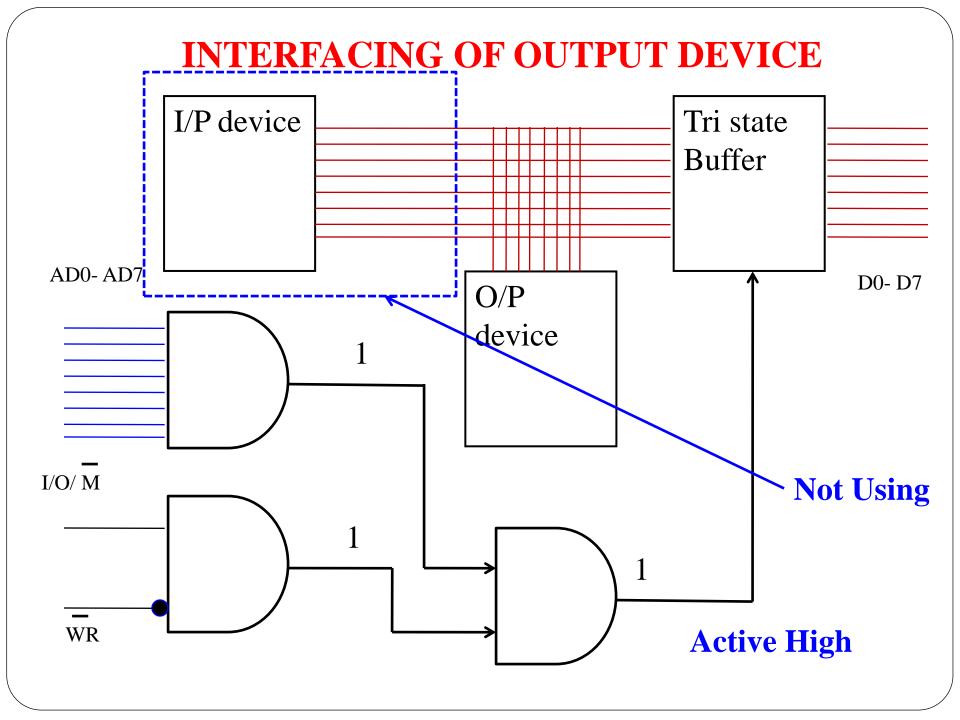

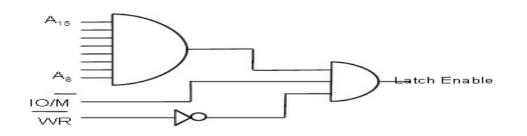

### **INTERFACING OF OUTPUT DEVICE**

- The address lines are decoded to generate a signal that is active when the particular port is being accessed.

- An IOWR signal is generated by combining the IO/M and the WR signals from the microprocessor.

The Latch will be enabled when:

- -VVR = 0

- IO/M = 1

- The address on A8 A15 = FFH

## **Memory Mapped I/O Interfacing**

- Input and output transfer using memory mapped I/O are not limited to the accumulator.

- Same of 8085 instructions can be used for memory mapped I/O ports.

- MOV r, m move the connects of input port whose address is available in (H,L) register pair to any internal register.

- LDA address load the acc with the content of the input port whose address is available as a second and third byte of the instruction.

### **INTERFACING OF OUTPUT DEVICE**

#### •LED INTERFACING

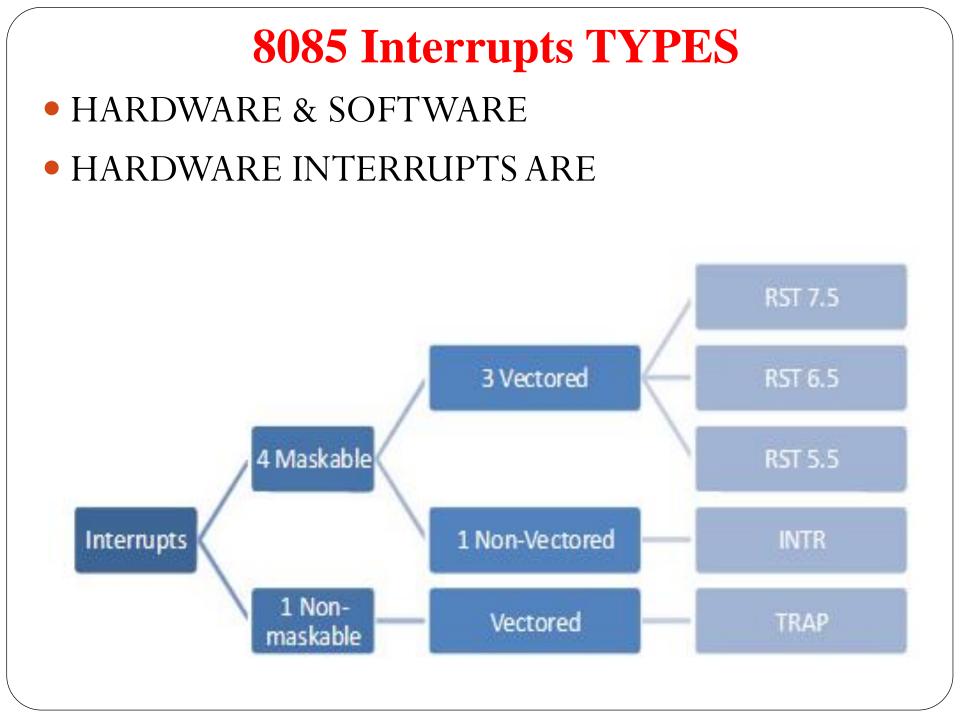

- An interrupt is considered to be an **emergency signal** that may be serviced.

- The Microprocessor may respond to it as soon as possible.

- When the Microprocessor receives an interrupt signal, it suspends the currently executing program and jumps to an Interrupt Service Routine (ISR) to respond to the incoming interrupt.

- Each interrupt will most probably have its own ISR.

- There are two ways of redirecting the execution to the ISR depending on whether the interrupt is vectored or non-vectored.

- <u>Vectored</u>:The address of the subroutine is <u>already known</u> to the Microprocessor

- <u>Non Vectored</u>: The device will have to supply the address of the subroutine to the Microprocessor

- The '**EI' instruction** is a one byte instruction and is used to Enable the maskable interrupts.

- The '**DI' instruction** is a one byte instruction and is used to Disable the maskable interrupts.

| Interrupt<br>Name    | Maskable | Masking<br>Method | Vectored | Memory | Triggering<br>Method         |

|----------------------|----------|-------------------|----------|--------|------------------------------|

| INTR                 | Yes      | DI / EI No        |          | No     | Level<br>Sensitive           |

| RST 5.5 /<br>RST 6.5 | Yes      | DI / EI<br>SIM    | Yes      | No     | Level<br>Sensitive           |

| RST 7.5              | Yes      | DI / EI<br>SIM    | Yes      | Yes    | Edge<br>Sensitive            |

| TRAP                 | No       | None              | Yes      | No     | Level &<br>Edge<br>Sensitive |

| 8085 has '8' software interrupt |

|---------------------------------|

| 1)RST0                          |

| 2)RST1                          |

| 3)RST2                          |

| 4)RST3                          |

| 5)RST4                          |

| 6)RST5                          |

| 7)RST6                          |

| 8)RST7                          |

|                                 |

| Interrupt | Restart locations |

|-----------|-------------------|

| RST 0     | 0 X 8 = 0000h     |

| RST 1     | 1 X 8 = 0008h     |

| RST 2     | 2 x 8 = 0010h     |

| RST 3     | 3 X 8 = 0018h     |

| RST 4     | 4 X 8 = 0020h     |

| RST 5     | 5 X 8 = 0028h     |

| RST 6     | 6 X 8 = 0030h     |

| RST 7     | 7 X 8 = 0038h     |

|           |                   |

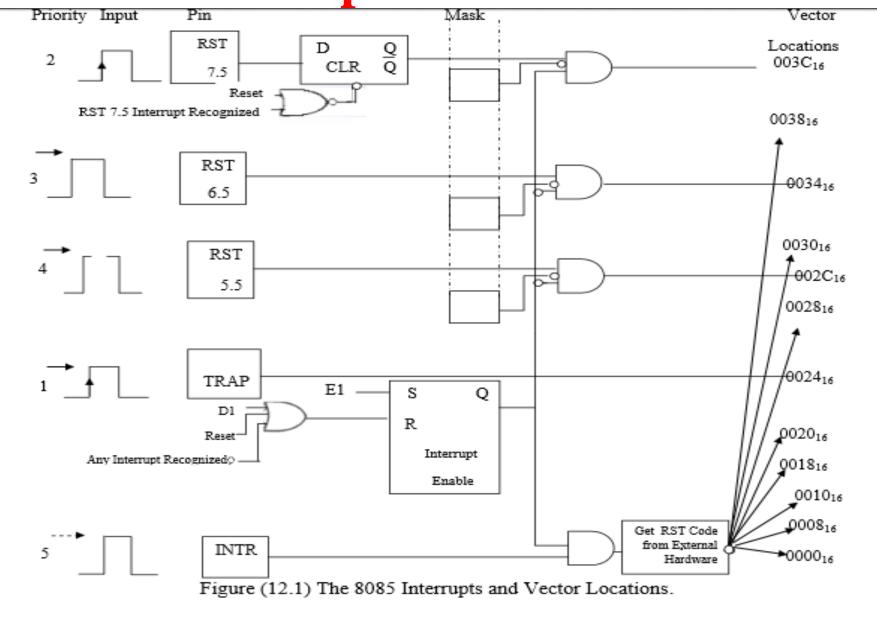

## **Interrupts PRIORITY**

| Interrup t type | Trigger        | Priority        | Maskable | Vector<br>address |

|-----------------|----------------|-----------------|----------|-------------------|

| TRAP            | Edge and Level | 1 <sup>st</sup> | No       | 0024H             |

| RST 7.5         | Edge           | 2 <sup>nd</sup> | Yes      | 003CH             |

| RST 6.5         | Level          | 3 <sup>rd</sup> | Yes      | 0034H             |

| RST 5.5         | Level          | 4 <sup>th</sup> | Yes      | 002CH             |

| INTR            | Level          | 5 <sup>th</sup> | Yes      | -                 |

## **Interrupt STRUCTURE**

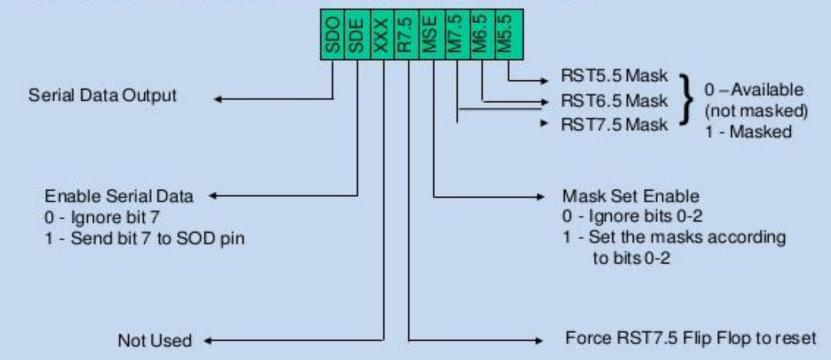

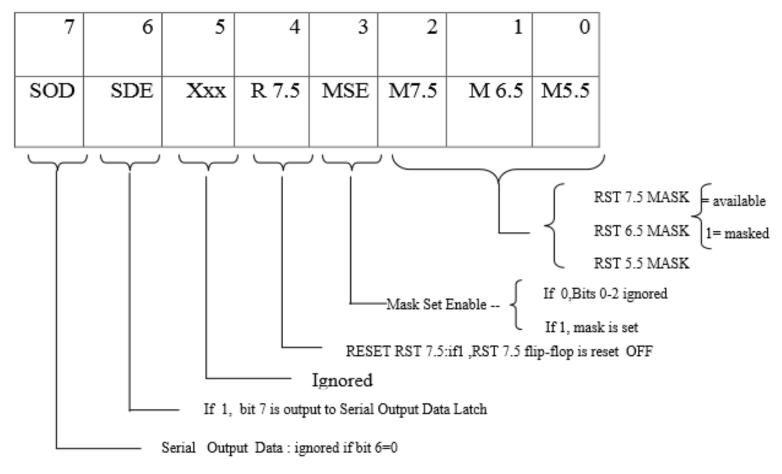

### **SIM Instruction**

SIM instruction can be used to perform two different tasks: 1. For masking of 3 interrupts 2. For serial data transmission (Each time a SIM instruction is executed, 7<sup>th</sup> bit of Accumulator is automatically copied to SOD pin of 8085)

While EI/DI instructions enable/disable all maskable interrupts at once, SIM instruction can be used to selectively mask (or disable) 3 out of 4 maskable interrupts which are RST7.5,RST6.5 & RST5.5. Fourth maskable interrupt INTR can only be enabled/disabled by using EI/DI instructions.

#### • SIM

Figure (12.2) Interpretation of the Accumulator Bit \_

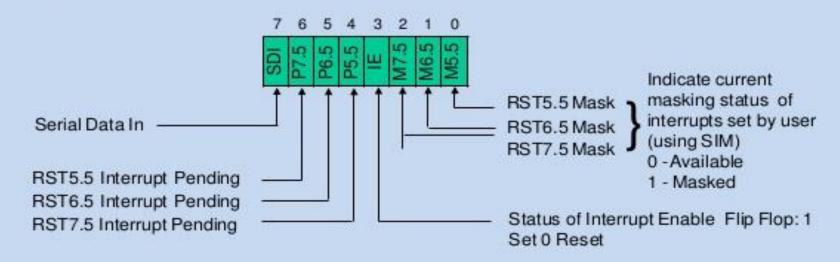

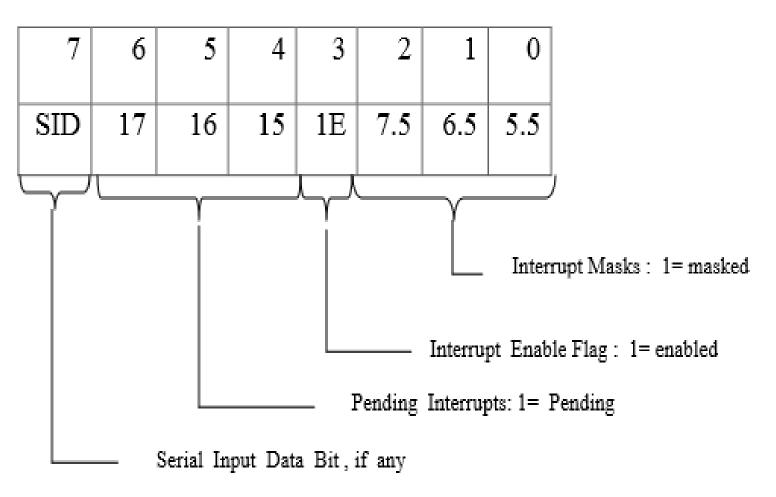

#### **RIM** instruction

Like SIM instruction, RIM can be used to perform two different tasks: 1. To read current status of 3 maskable interrupts 2. For serial data reception (Each time a SIM instruction is executed, the bit present on SID pin of 8085 is automatically moved to 7<sup>th</sup> bit of the Accumulator)

**Pending Interrupts:** Since the 8085 has 5 interrupt lines, another interrupts may occur while an interrupt is being attended and thus remain pending. Such interrupts are called pending interrupts & would be attended as soon as ISR of current interrupt is executed. A programmer may know the status (current value of high/low on the respective interrupt pin) of such interrupts anytime by using RIM instruction.

#### • RIM

### **Peripheral Interfacing**

#### 8255 PIN

$\leftrightarrow PA_{4}$ 40  $PA_3 \leftrightarrow$ D<sub>0</sub> - D<sub>7</sub> k→ PA, 39  $PA_2 \leftrightarrow$ 2 PA<sub>o</sub> PA., ₩8 38 A PA  $PA_i \leftrightarrow$ 3.  $\leftrightarrow$  PA,  $PA_{o} \leftrightarrow$ 37 4  $\overrightarrow{RD} \rightarrow \overrightarrow{CS} \rightarrow$ 36 🗲 WR 5 RD-– RESET 35 6  $34 \leftrightarrow D_0$ WR-V<sub>ss</sub> ← 7 PC<sub>7</sub> - PC<sub>4</sub>  $k \rightarrow D_1$ 33  $A_1 \rightarrow$ 8 8255A 8255A A<sub>0</sub>  $k \rightarrow D_2$ A., 9 32  $k \rightarrow D_3$ 31  $PC, \leftrightarrow 10$ A<sub>0</sub> - $PC_6 \leftrightarrow 11$ 30  $\rightarrow D_{4}$  $\rightarrow D_{s}$ 29  $PC, \leftarrow 12$ PC<sub>3</sub> - PC<sub>0</sub> RESET k→ D₀ 28 PC, () 13 k→ D, 27  $PC_{\circ} \leftrightarrow 14$  $-v_{cc}$  $\overline{cs}$ 26  $PC_1 \leftrightarrow 15$ 25  $\leftrightarrow$  PB,  $PC_2 \leftrightarrow 16$ (+5V)V<sub>cc</sub>  $24 \leftrightarrow PB_6$ PB, - PB PC, ↔ 17  $\leftrightarrow PB_{s}$  $PB_{0} \leftrightarrow 18$ 23 (0V)V<sub>ss</sub>  $PB_1 \leftrightarrow 19$ 22  $\rightarrow PB_{1}$ 21  $\leftrightarrow$  PB,  $PB_2 \leftrightarrow 20$

| Pin                             | Description      |

|---------------------------------|------------------|

| $\mathbf{D}_0 - \mathbf{D}_7$   | Data lines       |

| RESET                           | Reset input      |

| <u>C</u> S                      | Chip select      |

| RD                              | Read control     |

| WR                              | Write control    |

| A <sub>0</sub> , A <sub>1</sub> | Internal address |

| PA, - PA                        | Port-A pins      |

| $PB_7 - PB_0$                   | Port-B pins      |

| $PC_7 - PC_0$                   | Port-C pins      |

| V <sub>cc</sub>                 | +5V              |

| V <sub>ss</sub>                 | OV (GND)         |

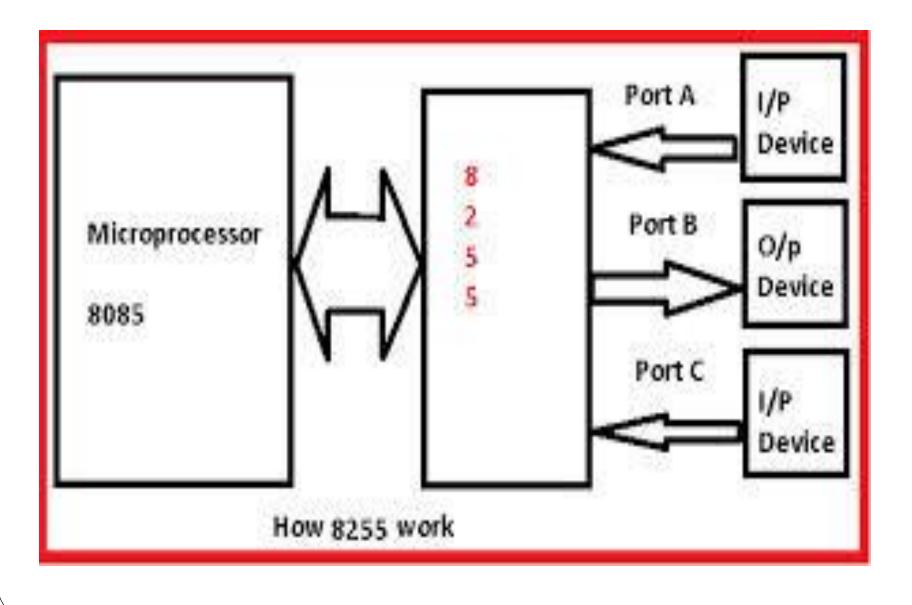

#### PPI 8255

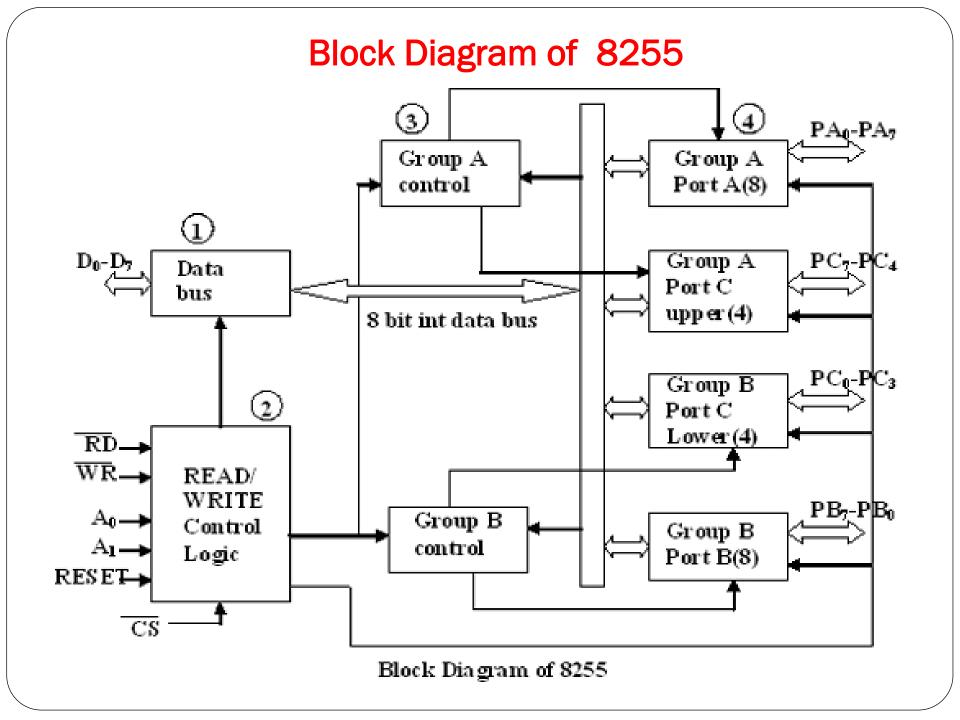

• It is an I/O port chip used for interfacing I/O devices with microprocessor. The parallel input-output port chip 8255 is also called as programmable peripheral input-output *port.* It has 40 PINS. **24 input/output lines** which may be individually programmed in groups. The groups of I/O pins are named as Group A, Group B and group C upper and Group C lower. Each of these two groups contains a subgroup of eight I/O lines called as 8-bit port and another subgroup of four lines or a 4-bit port. The port A lines are identified by symbols PA0-PA7 while the port C lines are identified as PC4-PC7. Similarly, Group B contains an 8-bit port B, containing lines PB0-PB7 and a 4-bit port C with lower bits PC0- PC3.All of these ports can function independently either as input or as output ports. This can be achieved by programming the bits of an internal register of 8255 called as control word register (CWR).

#### Pin Diagram of 8255

- The 8255 is a 40 pin integrated circuit (IC), designed to perform a variety of interface functions in a computer environment.

- **D0 D7** These are the data input/output lines for the device.

- All information read from and written to the 8255 occurs via these 8 data lines.

- CS (*Chip Select Input*). If this line is a logical 0, the microprocessor can read and write to the 8255.

- RD (*Read Input*) Whenever this input line is a logical 0 and the CS input is a logical 0, the 8255 data outputs are enabled onto the system data bus.

#### Pin Diagram of 8255

- WR (*Write Input*) Whenever this input line is a logical 0 and the CS input is a logical 0, data is written to the 8255 from the system data bus

- A0 A1 (*Address Inputs*) The logical combination of these two input lines determines which internal register of the 8255 data is written to or read from.

- **RESET** The 8255 is placed into its reset state if this input line is a logical 1. All peripheral ports are set to the input mode.

## Pin Diagram of 8255

- **PA0 PA7**, **PB0 PB7**, **PC0 PC7** These signal lines are used as 8-bit I/O ports.

- They can be connected to peripheral devices.

- The 8255 has three 8 bit I/O ports and each one can be connected to the physical lines of an external device.

- These lines are labeled PA0-PA7, PB0-PB7, and PC0-PC7.

- The groups of the signals are divided into three different I/O ports labeled port A (PA), port B (PB), and port C (PC).

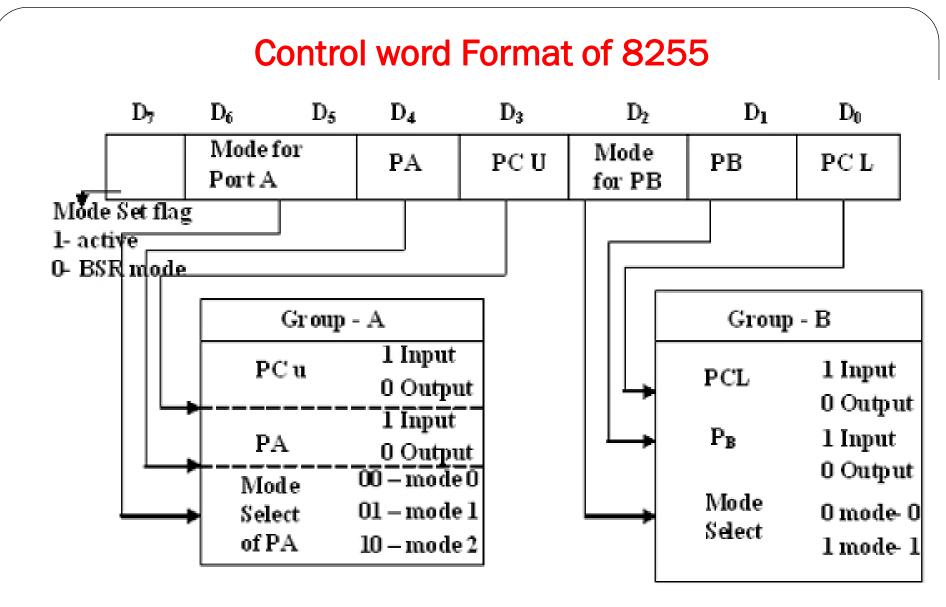

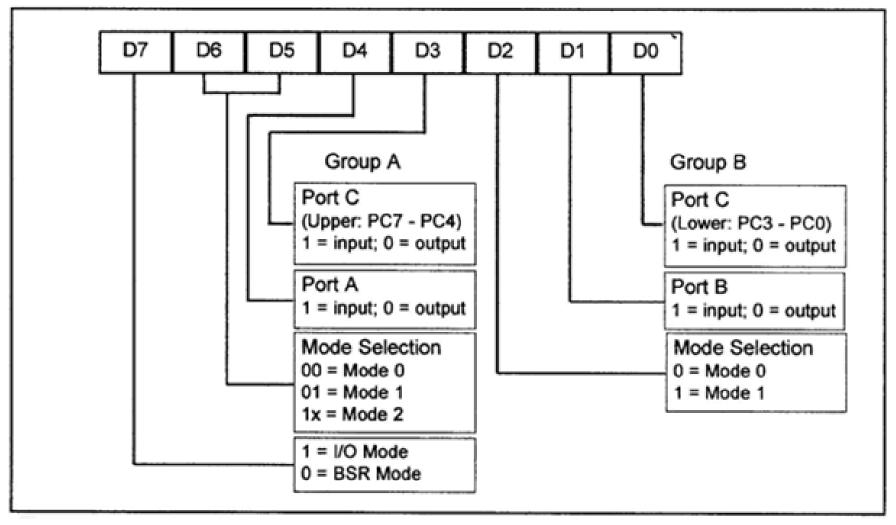

Control Word Format of 8255

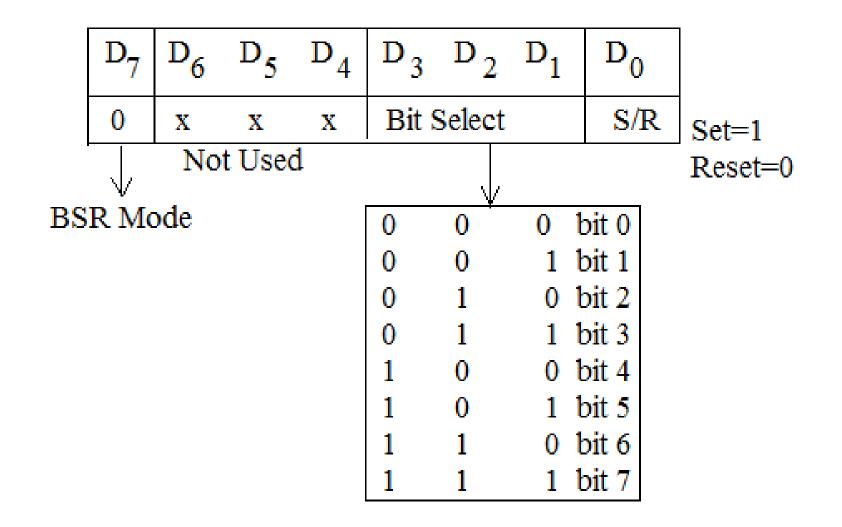

- There are two basic modes of operation of 8255, They are:

- 1. I/O mode.

- 2. BSR mode.

- In I/O mode, the 8255 ports work as programmable I/O ports, while

- In BSR mode only port C (PC0-PC7) can be used to set or reset its individual port bits.

- There are 3 I/O modes of operation for the ports of 8255.

- Mode 0, Mode 1, and Mode 2

```

• 1) Mode 0 - Basic I/O mode

```

```

2) Mode 1 - Strobed I/O mode

```

3) Mode 2 - Strobed bi-directional I/O

- <u>Mode 0 Operation</u>

- It is Basic or **Simple I/O.**

- It does not use any handshake signals.

- It is used for interfacing an i/p device or an o/p device.

- It is used when timing characteristics of I/O devices is well known

- <u>Mode 1 Operation</u>

- It uses handshake I/O.

- 3 lines are used for handshaking.

- It is used for interfacing an i/p device or an o/p device.

- Mode 1 operation is used when timing characteristics of I/O devices is not well known, or used when I/O devices supply or receive data at irregular intervals.

- Handshake signals of the port inform the processor that the data is available, data transfer complete etc.

- <u>Mode 2 Operation</u>

- It is bi-directional handshake I/O.

- Mode 2 operation uses 5 lines for handshaking.

- It is used with an I/O device that receives data some times and sends data sometimes.

- Mode 2 operation is useful when timing characteristics of I/O devices is not well known, or when I/O devices supply or receive data at irregular intervals.

- Port A, Port B and Port C can work in Mode 0

- Port A and Port B can work in Mode 1

- Only Port A can work in Mode 2

# IO MODE CONTROL WORD

Control Word Format 8255A

# BSR MODE WORD

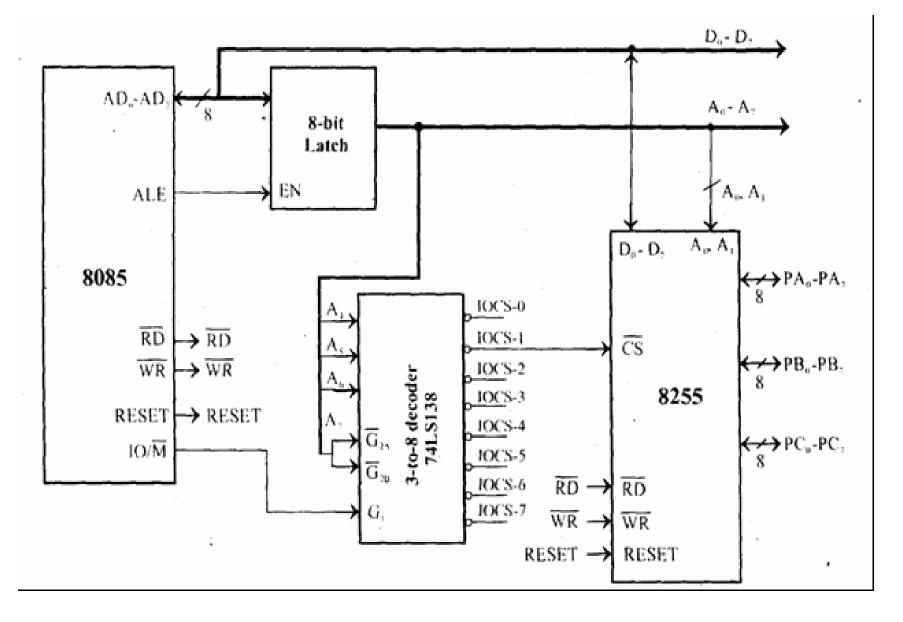

## **Interfacing WITH8255**

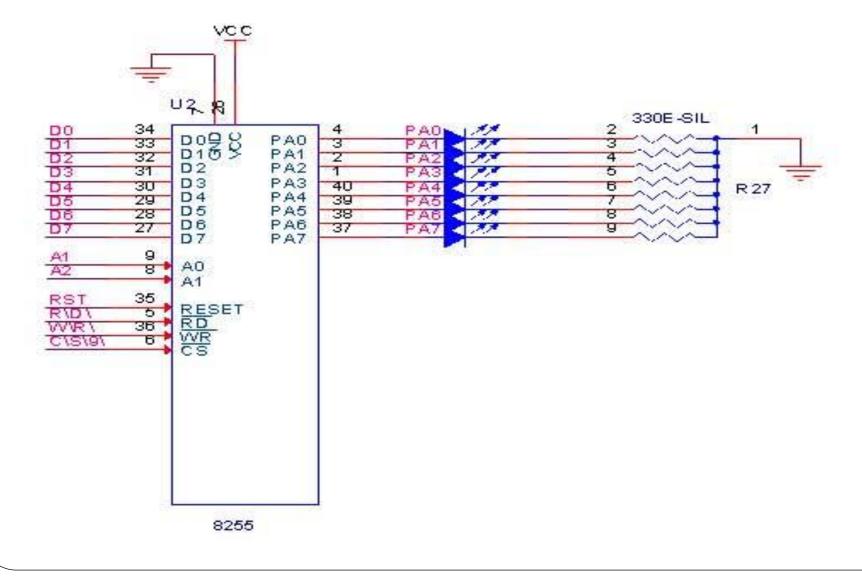

# LED INTERFACING

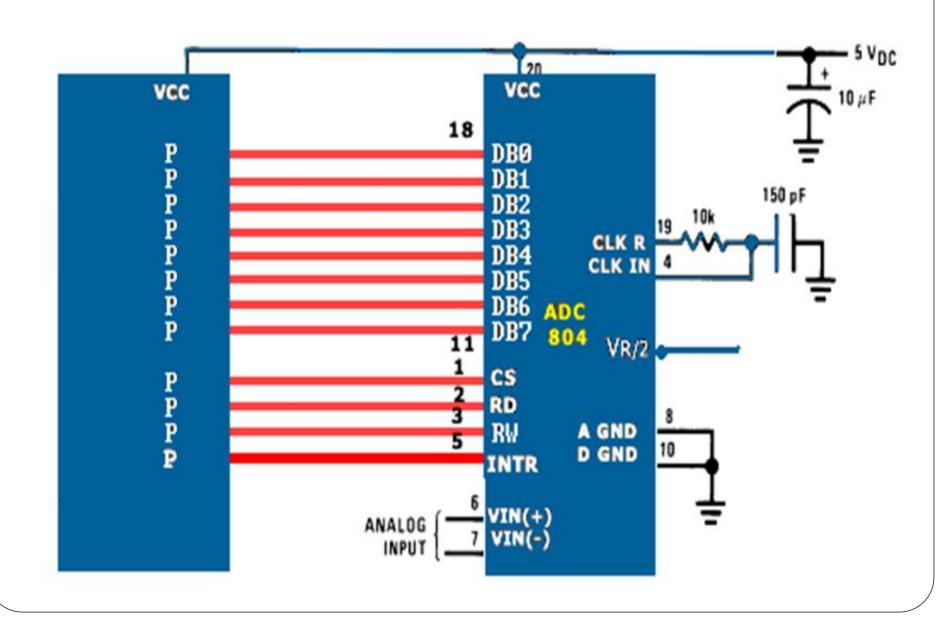

- In most of the cases, the PIO 8255 is used for interfacing the analog to digital converters with microprocessor through its ports.

- The analog to digital converters is treated as an input device by the microprocessor, that sends an initializing signal to the ADC to start the analogy to digital data conversation process.

- The process of **analog to digital conversion is a slow process**, and the **microprocessor has to wait for the digital data** till the conversion is over.

- After the conversion is over, the ADC sends end of conversion EOC signal to inform the microprocessor that the conversion is over and the result is ready at the output buffer of the ADC.

- These tasks of issuing an SOC pulse to ADC, reading EOC signal from the ADC and reading the digital output of the ADC are carried out by the CPU using 8255 I/O ports.

- The time taken by the ADC from the active edge of SOC pulse till the active edge of EOC signal is called as the conversion delay of the ADC.

- Successive approximation techniques and dual slope integration techniques are the most popular techniques used in the integrated ADC chip.

- The analog to **digital converter chips 0808 and 0809 are 8-bit CMOS**, successive approximation converters.

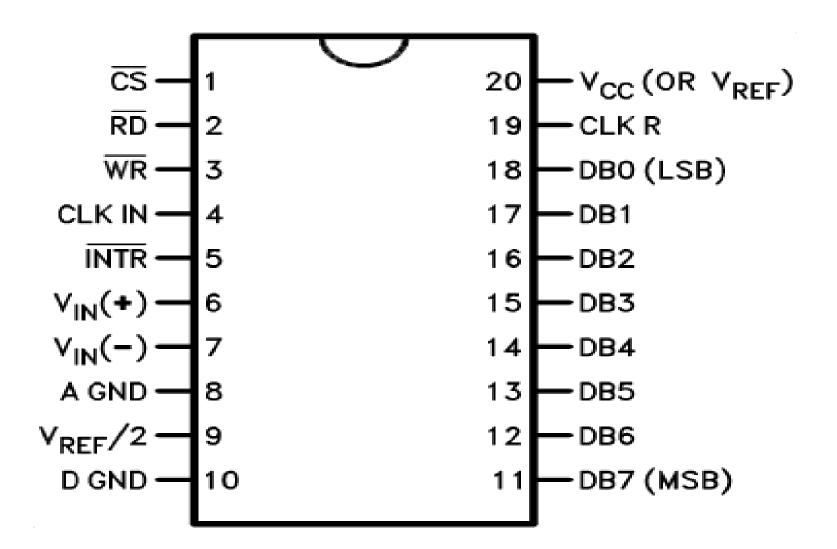

## **ADC 0804**

• <u>CS</u>: Active low input used to activate the ADC0804 chip.

<u>*RD* (*data enable*) : Active low input used to get converted data out of the ADC0804 chip. When CS = 0, if a high-to-low pulse is applied to the RD pin, the 8-bit digital output shows up at the D0-D7 data pins.</u>

<u>*WR* (*start conversion*): Active low input used to inform the ADC0804 to start the conversion process. If CS = 0when WR makes a low-to-high transition, the ADC0804 starts converting the analog input value of Vin to an 8bit digital number. When the data conversion is complete, the INTR pin is forced low by the ADC0804.</u>

• <u>CLK IN and CLK R</u>: Connect to external capacitor and resistor for self-clocking, f = 1/(1.1RC). The clock affect the conversion time and this time cannot be faster than 110 micros.

**INTR (end of conversion)** This is an active low output pin. When the conversion is finished, it goes low to signal the CPU that the converted data is ready to be picked up. After INTR goes low, we make CS = 0 and send a high-to-low pulse to the RD pin to get the data out of the ADC0804 chip.

- Vin (+) and Vin (-): These are the differential analog inputs where Vin = Vin (+) Vin (-). Often the Vin (-) pin is connected to ground and the Vin (+) pin is used as the analog input to be converted to digital.

- <u>VCC</u>: This is the +5V power supply. It is also used as a reference voltage when the Vref/2 (pin 9) input is open.

| Vref/2 (V)    | Vin (V)   | Step Size (mV)   |

|---------------|-----------|------------------|

| Not connected | 0 to 5    | 5/255 = 19.60    |

| 2.0           | 0 to 4    | 4/255 = 15.69    |

| 1.5           | 0 to 3    | 3/255 = 11.76    |

| 1.28          | 0 to 2.56 | 2.56/255 = 10.04 |

| 1.0           | 0 to 2    | 2/255 = 7.84     |

| 0.5           | 0 to 1    | 1/255 = 3.92     |

<u>Vref/2:-</u> Input voltage pin used for the reference voltage. If this pin is open, the analog input voltage for the the ADC is ranged from 0 to 5 volts. This is optional input pin. It is used only when the input signal range is small. When pin 9 is at 2V, the range is 0-4V, i.e. Twice the voltage at pin 9. Pin 6 (V+), Pin 7(V-): The actual input is the difference in voltages applied to these pins. The analogue input can range from 0 to 5V.

<u>**D0**</u> – <u>**D7**</u> output PINs of ADC: D0 – D7 are the digital data output pins. These are the tri-state buffered and the converted data is accessed only when CS = 0 and RD is forced low. The output voltage:

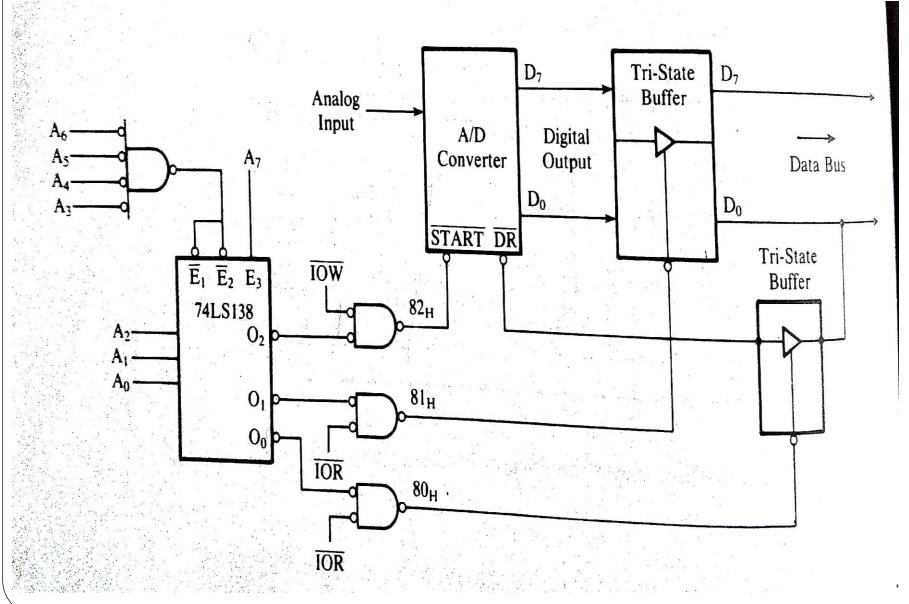

# A/D Interfacing [0808 ]

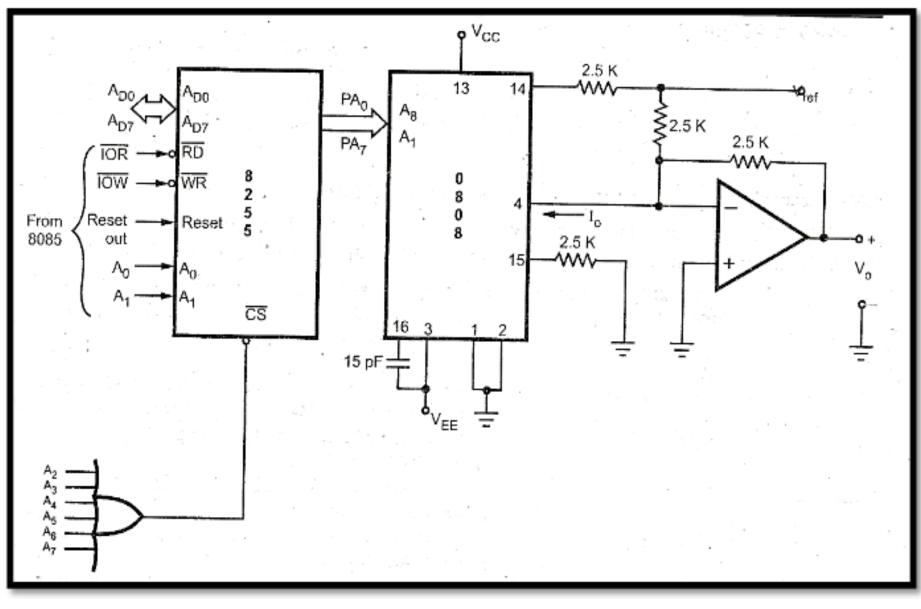

# D/A INTERFACING

• INTERFACING DIGITAL TO ANALOG CONVERTERS: The digital to analog converters convert binary number into their equivalent voltages. The DAC find applications in areas like digitally controlled gains, motors speed controls, programmable gain amplifiers etc.

## **D/A Interfacing**

# **MODULE 4**

# **EMBEDDED SYSTEM**

# EMBEDDED SYSTEM

#### System

A system is an arrangement in which all its unit assemble work together according to a set of rules. It can also be defined as a way of working, organizing or doing one or many tasks according to a fixed plan.

For example, a watch is a time displaying system. Its components follow a set of rules to show time. If one of its parts fails, the watch will stop working. So we can say, in a system, all its subcomponents depend on each other

# **EMBEDDED SYSTEM**

• Embedded means something that is attached to another thing. An embedded system can be thought of as a computer hardware system having software embedded in it. An embedded system can be an independent system or it can be a part of a large system. An embedded system is a microcontroller or microprocessor based system which is designed to perform a specific task. For example, a fire alarm is an embedded system; it will sense only smoke.

# COMPONENTS

- It has hardware.

- It has application software.

- L It has Real Time Operating system (RTOS) that supervises the application software and provide mechanism to let the processor run a process as per scheduling by following a plan to control the latencies. RTOS defines the way the system works. It sets the rules during the execution of application program. A small scale embedded system may not have RTOS.

# Characteristics of an Embedded System

- Single-functioned An embedded system usually performs a specialized operation and does the same repeatedly. For example: A pager always functions as a pager.

- Tightly constrained All computing systems have constraints on design metrics, but those on an embedded system can be especially tight

- Reactive and Real time Many embedded systems must continually react to changes in the system's environment and must compute certain results in real time without any delay.

# Characteristics

- **Microprocessors based** It must be microprocessor or microcontroller based.

- Memory It must have a memory, as its software usually embeds in ROM. It does not need any secondary memories in the computer.

- Connected It must have connected peripherals to connect input and output devices.

- HW-SW systems Software is used for more features and flexibility. Hardware is used for performance and security.

# ADVANTAGES & DISADVANTAGES

#### **ADVANTAGES**

#### DISADVANTAGES

- Easily

Customizable

- Low power consumption

- Low cost

- Enhanced performance

- High development effort

- Larger time to market

ICET

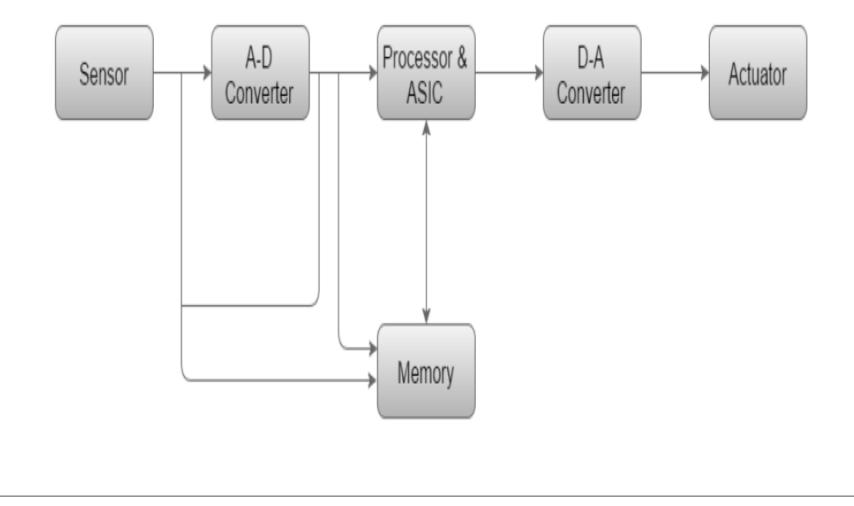

# **ES BLOCK DIAGRAM**

- Sensor It measures the physical quantity and converts it to an electrical signal which can be read by an observer or by any electronic instrument like an A2D converter. A sensor stores the measured quantity to the memory.

- **A-D Converter** An analog-to-digital converter converts the analog signal sent by the sensor into a digital signal.

- **Processor & ASICs** Processors process the data to measure the output and store it to the memory.

- **D-A Converter** A digital-to-analog converter converts the digital data fed by the processor to analog data.

- Actuator An actuator compares the output given by the D-A Converter to the actual (expected) output stored in it and stores the approved output.

#### www.pantechsolutions.net

## **Generalization of Application Areas**

- Embedded Systems cover such a broad range of products that generalization is difficult. Here are some broad categories:

- Aerospace and Defense Electronics

- Automotive

- Broadcast and Entertainment

- Consumer and Internet Appliances

- Data Communication

- Digital Imaging

- Industrial Measurement and Control

- Telecommunications

- Mobile Data Infrastructures etc.

PARTECH SOLUTIONS Technology Beyond The Dreams

# SYSTEM SOFTWARE

- It consist of many programs that support the operation of a computer

- It helps the user to concentrate in the application program without worrying about how the computers work internally

- System softwares are