# MUMBER SYSTEMS AND CODES

Denvert to do en D.

# CO. 10111101.0112

2). Convert deimal to binary 1). 2910 MSB -> HOST significant byte. LSB -> Lowest significant byte MSB 11). 5710 2 28-1 3-1 2 5710: 1110012 (111). 25610 256 04-0 25010, 1000000000 32-0 16-0

Scanned by CamScanner

$$2 \times 0.065 = 0.13$$

$2 \times 0.13 = 0.26$

$2 \times 0.26 = 0.52$

$2 \times 0.58 = 1.04$

$2 \times 0.04 = 0.08$

$$2 \times 0.625 = 1.25$$

$2 \times 0.25 = 0.5$

$2 \times 0.5 = 1$

$$2 \times 0.726 = 1.452$$

$2 \times 0.452 = 0.904$

$2 \times 0.904 = 1.808$

$2 \times 0.808 = 1.616$

$2 \times 0.808 = 1.616$

$2 \times 0.616 = 1.232$

$2 \times 0.232 = 0.464$

$0.72610 = 0.101112$

# BINARY ADDITION

$$\begin{array}{c} \text{Veiyication:} \\ 10.1101_2 + \\ \hline 11111_2 + \\ \hline 15 \\ \hline \hline 11100_2 + \\ \hline 28 \end{array}$$

$$\begin{array}{c}

O_{10} \longrightarrow O_{2} \\

I_{10} \longrightarrow I_{2} \\

O_{10} \longrightarrow IO_{2} \\

O_{10} \longrightarrow II_{2} \\

O_{10} \longrightarrow IO_{2}

\end{array}$$

·14=21-01-1200

# BINARY SUBTRACTION

NEGATIVE NOS.

1) -> We should take one's compliment (1's comp)

Eg: 11100102 3000 110 12

2). 2'S complement

Take is complument +1

Eg: 00011012

11100112

Eq: 1) -2510

\* we take 8 bits for -ve No.

MSB

-ve = 1

tve > 0

13 complement

11/00/102

2's complement

111001112

=> 111000110<sub>2</sub>

-128-64+32+14+04

= -26 +1 = -25

= - 128+64+32+4

Scanned by CamScanner

For 1°s complement, when converted to desimal, we need to add one (weighted sum) whereas for 2's compliment, we need not add 1. 2). - 39 2 9-1 >001001112 2 2-0 18s complement 2's complement 110110002 00101000 : -40+1: -39 110110012 = 2 + 2 + 2 + 2 + 2 + 2 + 2

$$= 2^{0} + 2^{1} + 2^{2} + 2^{4}$$

$$= 23_{10}$$

(b)

$$11101000_2$$

$= 2^3 + 2^5 + 2^6 - 2^7 = -24 + 1$

Q. Find deumal value of signed brainy no in 2's complement.

a)

$$01010110_2$$

$$= 2^{4} + 2^{2} + 2^{4} + 2^{6}$$

$$= 86$$

a. Add the signed nos:

Q. Add the signed numbers:

& Subtract the signed nos.

- ve sign with a bring of lake 2's complement &

U. 0 00 01 000, -000000112 take 2's complement & add.

(2).  $00001100_2 - 11110111_2$  12 - (-9) = 21

0 0 0 0 11 0 0 12+

(3)

$$11100111_{2} - 00010011_{2} \Rightarrow -25 - 19$$

$$= -25 + (-19)$$

$$= -44$$

$$= -44$$

# HEXADECIMAL

| DECIMAL | BINARY | HEXADECIHAL |

|---------|--------|-------------|

| 0       | 0000   | 00000       |

| 1.      | 00.01  | 1           |

| 2       | 0040   | 2           |

| 3       | 0011   | 3           |

| 4       | 0100   | 4           |

| 5       | 0101   | 5           |

| G       | 0110   | 6           |

| 7       | 0111   |             |

| 8       | 1000   | 8-          |

| 9       | 1001   | 9           |

| 10      | 1010   | A           |

| 11      | 1011   | B           |

| 12      | 1100   | C           |

| 13      | 1101   | D           |

| 14      | 1110   | E           |

| 15      | 1111   | +           |

|         | 1111   | F           |

a Convert binary to hexaderimal 0. 1100 1010 0101 01112 Group into 4 each. 1100, 6100101,01112 C A 5 716 > CA5716 (2)000/11/1/000/01/01/00/2 1 F 1 6 916 => 1F16916 - A SEAST TO XI T O Hexa to binary: (1). 10A416 1 0 A 4 16 000100001010010002 2) 4CFA16 0100110011111010,

Q. Hexa to decimal

1. Weighted Sum technique

3. Hexa - Binary - decimal

(b)

$$\cdot 2 \text{ Fi6}$$

$\downarrow \downarrow \downarrow$

00 1011112  $\longrightarrow |x2^2 + |x2^1 + |x2^0 + |x2^3 + |x2^5 + |x2$

a. Convert Deumal to hexa:

$$0.16|65_{10}$$

$\Rightarrow 41_{16}$

D. 86010

16 1860 16 18

| DECIMAL | BINARY |

|---------|--------|

| 0       | 000    |

| 1       | 001    |

| 2       | 010    |

| 3       | 011    |

| 4       | 100    |

| 5       | 101    |

| 6       | 110    |

| 7       | 111    |

a. convert & binary to Octal

O Convert octal to binary

O. Convert octal to decimal

1) Weighted Coding Ex-3 code

(2) Non-weighted Coding Carry code

= 4008

$$\begin{array}{c}

(add3) & 01002 + \\

01112 & 01112

\end{array}$$

$$\begin{array}{c}

011112 \\

011112

\end{array}$$

Now add, 01002 + 01112 = 81

BINARY TO GRAY 1stro write as it is 1877 = 11102 gnore the carry 1. 3 11012 = 10112 GRAY TO BINARY 1012 Write 1st no as it is

#### LOGIC GATES

The term gate is used to describe a circuit that performs logic operation

#### NOT

The invested or NOT performs the operation called invested or complementation. The invested changes one logic level to the opposite level. In terms of bits it changes bit I to o f o to i

Symbol. Truth Table

A y

O I

A y

I O

The regative indicator is a bubble (0) that indicates invession or complementation when it appears on the ilp or olp of one logic element. Generally, inputs are on the left of the logic symbol of the olp is on the right

Or Active low

Active high.

In boolean algebra a variable is represented by a letter. The complement of a variable is designated by a bar over the letter. A variable can take an a value of either 1 a a.

Bodean algebra uses variables of operators to describe a logic circuit.

The logic operation of NOT glade can be expressed as by taking A as input variable of variabl

| TRUTH | INPUT | TABLE OP |

|-------|-------|----------|

| A     | B     | У        |

| 0     | 0     | 0        |

| 0     | I     | t        |

| 1     | 0     | 1        |

| ŧ     | 1     | I        |

If A & B are two of variables and Y is the of variable, the logical of the can be expressed by a if blu two variables.

Y = A + B

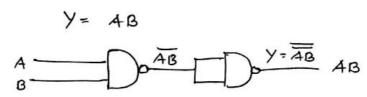

#### NAND GATE

It is a universal gate is, HAND gates can be used in combination to perform AND, OR & NOT operations. The team NAND is a contraction of NOT-AND & implies & AND function with complimental autput.

The NAND gate produces a low of only when all the inputs are high when one of the 1/p is low of is high.

| I   | 141h | Table  |     |         |             |

|-----|------|--------|-----|---------|-------------|

| 1np | +    | output | The | boolean | expressi on |

| A   | В    |        | for | CIMAN   | gate is     |

| AO  | 0    | 1      | V   |         |             |

| 0   |      | ľ      |     | Y =     | AB          |

| l   | 0    | 1      |     |         |             |

| ı   | ï    | ^      |     |         |             |

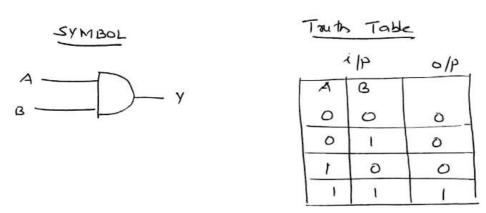

#### AND GATE

An AND gate produces a high olp only when all the inputs are high. When any one of the ilp is how olp is how. If A & B are the two inputs then y is the olp variable. Its tenth table is shown below. It performs logical multiplication

The logic expression of AND gate using two vasiables is represented mathematically either by placing a slot (1) between the two vasiables as A.B a by simply writing the adjacent letters without the dot as AB.

Thus the Boolean expression for AND get is

[Y = AB.]

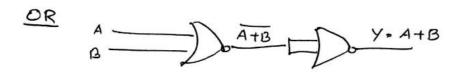

#### OR GATE

An or gate can have two armore input and performs logical addition. An or gate produces a high on the olp when any of the ilp is high. The olp is low only when all the ilps are low. ... an or gates determine when one or more inputs are high produces a high on the olp.

#### EXCLUSIVE OR ( EXO R)

The Ex-OR gate has only two inputs. The old Ex OR gate is high only when the two inputs one at opposite logic levels.

|   | Truth | Table | Bodean expression for |

|---|-------|-------|-----------------------|

| A | В     | olp   | Ex-or gate is         |

| 0 | 0     | 0     |                       |

| 0 | 1     | 1     | , ,,,,                |

| 1 | 0     | ı     | SYMIBOL               |

| ١ | ı     | 0     | A Y= A B              |

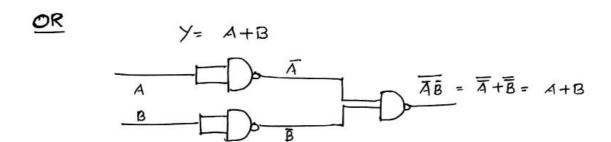

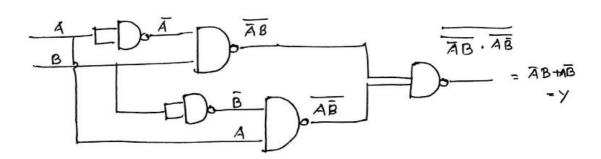

REALISATION OF AND OR NOT AND EX-OR GATES

USING NAND GATE

AND

NOT A Do A

Ex-OR  $Y=\overline{AB}+\overline{AB}$

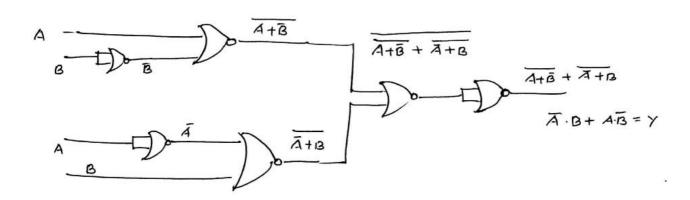

REALIZATION OF AND, OR, NOT & EX-OR GATES

AND y = AB AB = AB

EX-OR GATE Y, AB+ AB

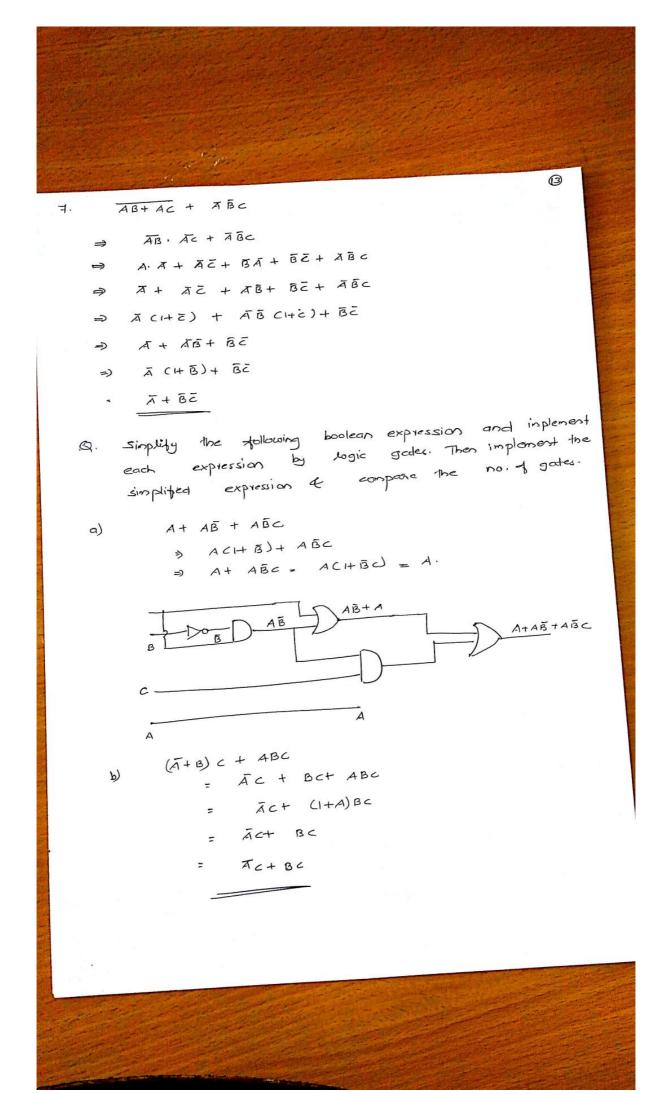

SIMPLIFICATION OF BOOLEAN EXPRESSIONS

RULE 1: Let a be a vasiable than

a+ a= 1 (sun ex a variable & its complement=1)

a.ā = 0 (product " = 0)

= a (double complement)

a ā a+ā aā jā

0 1 0 0

1 0 1 0 1

RULE 2 Let a be a variable then

a+1=1 (any variable +1=1)

ato=a (any variable + 0 = 0)

foord

Absorption law: it a & b are two variables

then at ab = a or a (1+b) = a·1 = a

Here the variable b is absorbed by variable a

Proof:  $a+\bar{a}b = a+ab+\bar{a}b = a+(a+\bar{a})b$ ; a+b  $a(\bar{a}+b) = a\bar{a}+ab = ab+1 = ab$   $\bar{a}(a+b) = \bar{a}a+\bar{a}b = 1+\bar{a}b$

RULE 4: Idempotency: Let a be a versible than

ata: a & a.a.a

a ata a.a

o o o

- 1

1

RULE 5: COMMUTATIVE LAW: If a fb are too variables

then

a+b: b+a & a.b., b.a

RULEG: Associative law: If a, b & c are three variables then

a+(b+c) = (a+b)+c & a.(b.c).((a.b-c)

RULET: DISTRIBUTIVE LAW If a, b & c are three

Vasicides then, a(b+c) = ab + ac + c a+bc = (a+b)(a+c) boolean algebraSpecial property of boolean algebra

RUE 8: DEMORGAN'S LAN

If  $a \notin b$  are two variables then  $\overline{a+b} = \overline{a} \cdot \overline{b} \notin$   $\overline{ab} = \overline{a+b}$

RULE 9 Consensus theorem: If a,bfc are three variable then  $ab+bc+ca = ab+c\overline{a}$   $ab+bc+c\overline{a} = ab+(a+\overline{a})bc+\overline{a}c$   $= ab+abc+\overline{a}bc+\overline{a}c$   $= ab(1+c)+\overline{a}c(1+b)$

= ab+ac

# REPRESENTATION OF BOOLEAN EXPRESSION

Boolean expression can be represented in two terms

1. Sum of Products (SOP) term

2. Product of sums (POS) term

SOP FORM

This firm is also called Disjunctive Normality form (DNF)

eg: f(A,B,c) = AB+Bc

Standard sop form

This firm is also called Disjunctive canonical from CDCF). It is also called the expanded sund product form or canonical sum of product form. In this firm, the for is the sum of a number of product team where each product team contains all the variables of the form either in contains or uncomplemented form. This can be derived from the truth table by finding the sun of all the teams that correspond to those combination for which it assumes the value of all the teams.

$A(A, B, c) = \overline{A}B + \overline{B}c = \overline{A}B(c+\overline{c}) + (A+\overline{A})\overline{B}c$   $= \overline{A}Bc + \overline{A}B\overline{c} + \overline{A}Bc + \overline{A}\overline{B}c$

A product team which conforms all the variables of the An either in complemented or uncomplemented from is called a mintern. A mintern assumes the value 1 only for one combination of the variables.

An n- variable the can have in all 2n mintans.

The sum of the mintan whose value = 1 is the std., sop form of the offin.

The minterms are often denoted as mo, m, m2 where the suffixes are the decimal codes of the combinations. For a 3- variable of mo = \$\overline{ABC}\$ m, \$\overline{

\$(A, B, c) = m, + m2 + ms+m4

or by histing the decimal codes of the minterns of which it = 1

4 (ABC) = & m(1, 2, 3, 5)

where In represents the sum of all the ninterns whose decimal codes are given in the paranthesis

CONVERT THE FOLLOWING SOP FORM INTO STD

1. A+B = A(B+B) + (A+A)B

= AB+ AB+ AB+ AB

= AB + AB + AB

= 01 + 10 + 00

= mo + m + m2

= Em(0,102)

2. AB+ AB+ AC+ AC

= AB(C+Z)+ AB(C+Z)+ ACB+B)+A (B+B)E

\* ABC + ABC

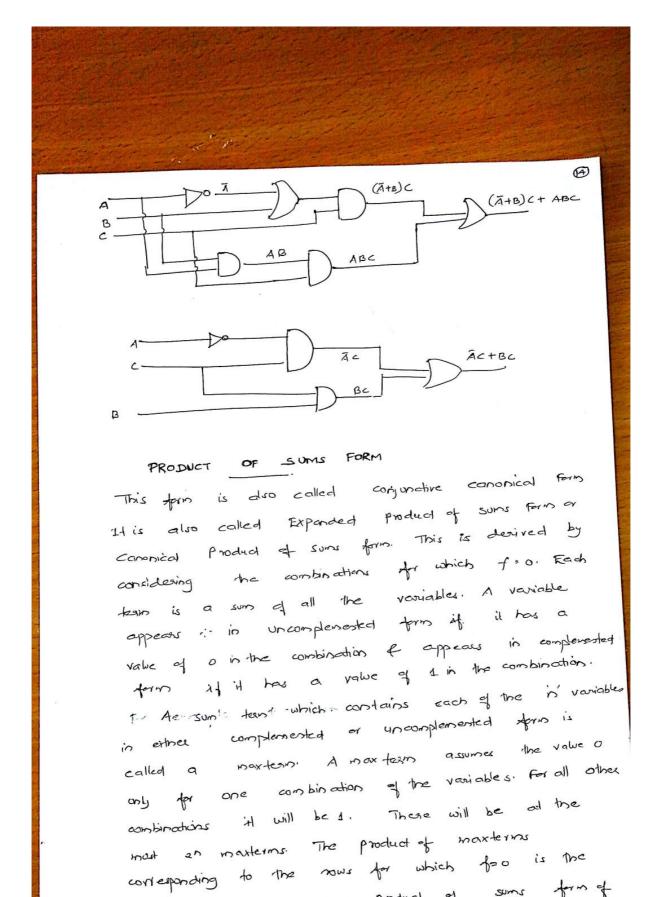

standard or canonical product of sums from of

the function.

Q. find the canonical post form for the following expression

2.

$$f(A, B, c) = Ac + Ac$$

#### 3. f(A,B, CD) = AC

(A+B+c+D) CA+B+c+D) CA+B+E+D) CA+B+E+D)

(A+B+c+D) CA+B+c+D) CA+B+E+D) CA+B+E+D)

(A+B+c+D) CA+B+c+D) CA+B+c+D) CA+B+c+D)

F(A,B,C,D) = AB+ ABC+ ED = AB(C+E) CD+B) + FBCCD+ B)+ (A+A) CB+B)CE

4BCO + 4BCO + 4BCO+ ABCO + ABCO+ ABCO

+ 4BCO + 4BCO + ABCO + ABCO

484) + 4865 + 4850 + 4856 + 486) + A 866 + 4850 + 4850

Emc 15, 14, 13, 12, 7, 6, 9, 5, 1)

Emc 1, 5, 6, 7, 9, 12, 13, 14, 15)

Emc 1, 5, 6, 7, 9, 12, 13, 14, 15)

(A+B+c+1) (A+B+E+BO) CA+B+E+B) (A+B+c+D)

CA+B+C+D)(4+B+&D) (A+B+E+D)

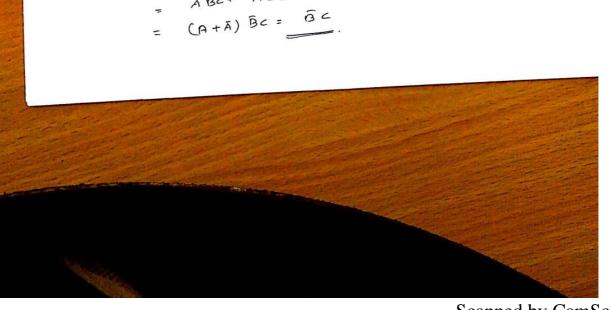

) - AB + AB + AC + AE

- AB(C+E) + ABCC+E) + A(B+B)C + ACB+B)C

- ABC+ ABC + ABC+ ABC+ ABC+ABC+ABC

+ ABC

ABC+ ABC+ ABC+ ABC+ ABC+ ABC

Em (9,52,567)

15 (34)

( A+&+ & ) ( A+B+c)

Scanned by CamScanner

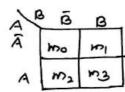

## K- MAP

The Karnaugh map is a systematic method of simplifying the Bodean expressions. The k-map is a chart or a group composed of an arrangement of adjacent cells, each representing a particular combination of variables in sun or product form.

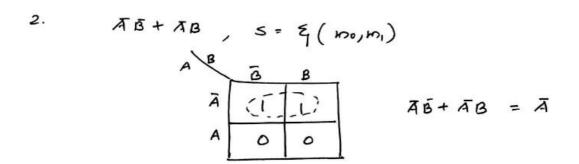

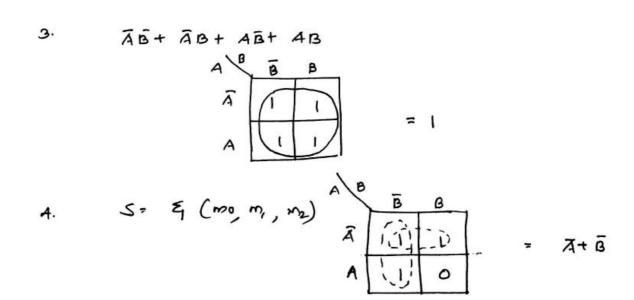

### TWO VARIABLE K- MAP

A two variable expression can have  $2^2 = 4$  possible combinations. Each of these combinations are  $\overline{AB}$ ,  $\overline{AB}$ ,  $A\overline{B}$  and AB (in the sop form) is called a minterm. Instead of representing the minterns in terms of the input variable using short hand notation the minterms may be represented in terms of their decimal designation on — for  $\overline{AB}$  on for  $\overline{AB}$  on  $\overline{AB}$

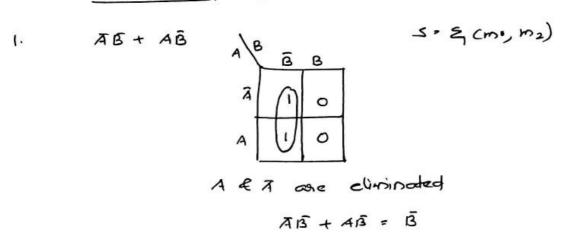

# MAPPING OF SOP EXPRESSIONS

A two variable is map has 2°-4 squares. These squares are called cells. Each square on the k map represents a unique minterm. A 1 placed in any square indicates that the corresponding mintern is included in the output expression of a o or no entry in a square indicates that the corresponding minterns about not appear the corresponding minterns about not appear in the expression for hour.

MAP FORMAT

#### a) Two voriable

If there are in variables 2" combinations are there and 2" cells are there.

mo, m, m2 & m3 one called minterns

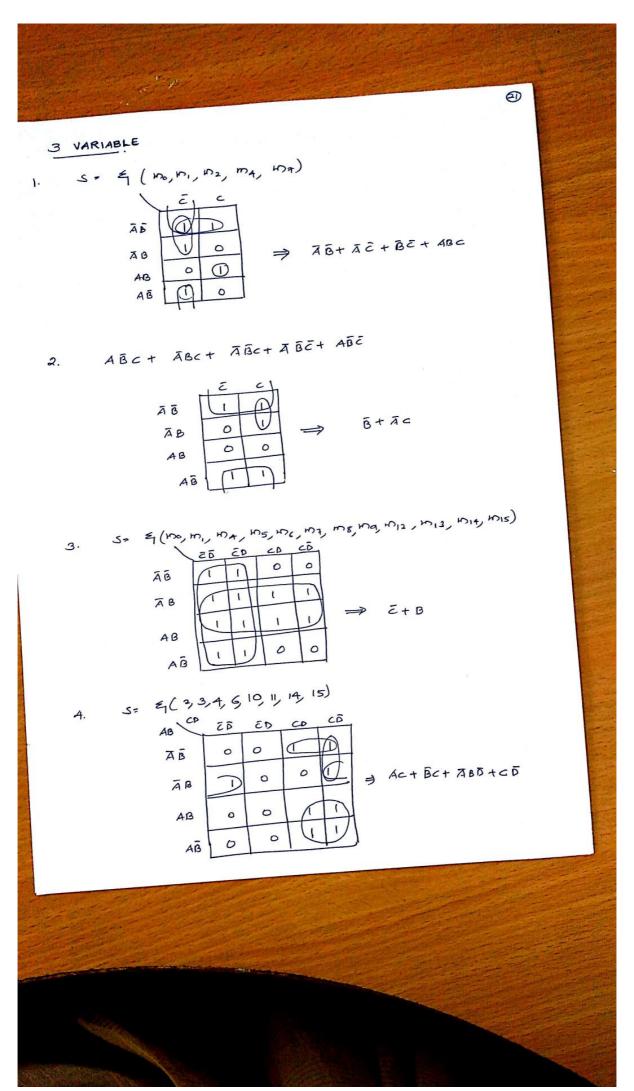

### b) Three variable

consider three variables AB&C

| AB | 2  | ٤  |

|----|----|----|

| AB | Mo | m  |

| AB | ma | Ms |

| AB | m6 | mz |

| AB | MA | m5 |

3 variable - stol now change.

#### c) four variables

ma

mil

PLOTTING THE BOOLEAN EXPRESSION

Once the Boolean expression is in son of the product form. Plot each on the K-map by placing a 1 in each cell corresponding to the team in so p expression Scanned by CamScanner

GROUPING OF CELLS

Group the is that all on adjacent cell Adjacent cells and a single variable.

A B B B

A III Adjacent cells of

The 1's in adjacent cells must be combined in groups of 1,2,4,8,16 of so on.

#### SIMPLIFICATION

Each group of 1 composed of all variable that appears in one form with in group. The variables that appears both complimentated of uncomplimented are eliminate the final simplified expression is formed by summit the part teams of all groups.

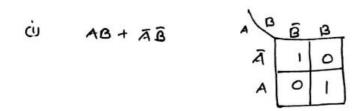

2 Variable K-Map

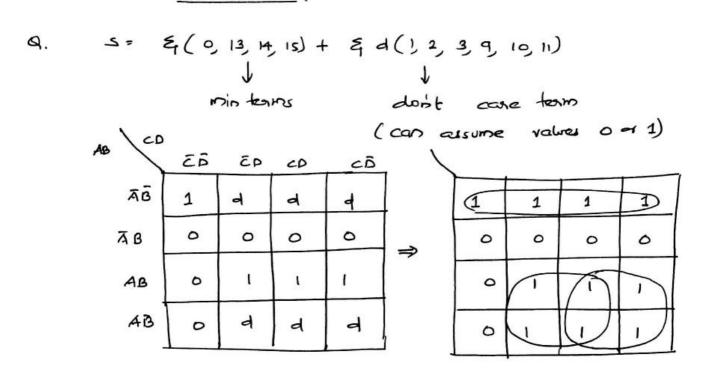

#### K- MAP INCLUDING DONT CARE

S= AB+AD+AC

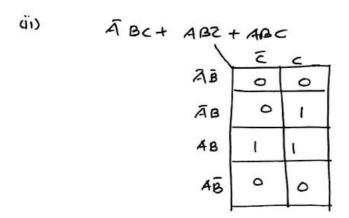

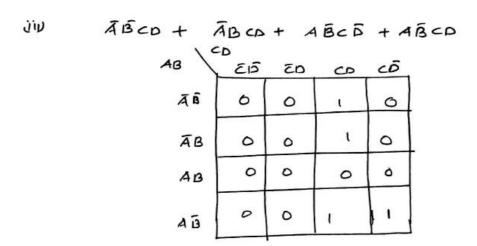

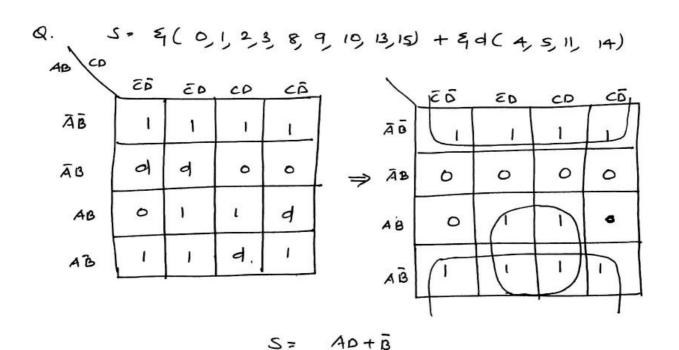

Q. Simplify the following expression using K-map approach.

5- 5(1,3,7,1,15)+ 5d(0,2,5)

| AB CO | ćβ | ED | CD | دة |

|-------|----|----|----|----|

| ĀĒ    | d  | ı  | ı  | d  |

| Zβ    | ٥  | d  | ı  | 0  |

| AВ    | 0  | 0  | 1  | ٥  |

| 48    | 0  | ٥  | ı  | 0  |

| /   | ζĎ | ćρ | CD | cō |

|-----|----|----|----|----|

| ΑĒ  |    | 1  |    | 7  |

| ĀB  | 0  | ٥  | 1  | 0  |

| A13 | 6  | 0  | 1  | ٥  |

| AB  | 0  | ٥  |    | ٥  |

|     |    |    |    |    |

Instructed and and

### MODULE-3

COMBINATIONAL CIRCUITS

XOR (Exclusive OR)

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 | 0 |

XNOR (Exclusive NOR)

| A | В | У |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

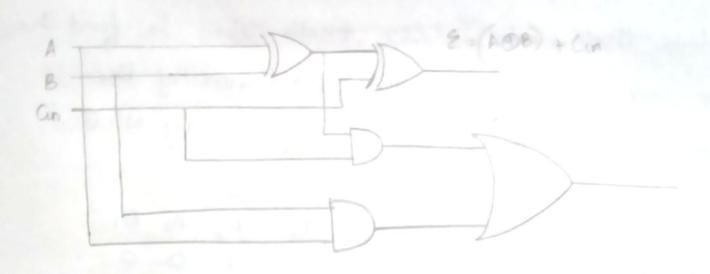

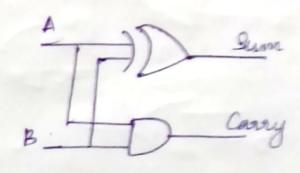

ADDER CIRCUITS

| (2). | FOOL | adder |

|------|------|-------|

| 6    | ruu  | adde  |

| A | B | Cin | ٤ | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 |   | 0   | 1 | 0    |

| 0 |   | (   | 0 | 1    |

| 1 | 0 | 0   | I | 0    |

| 1 | 0 | . 1 | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

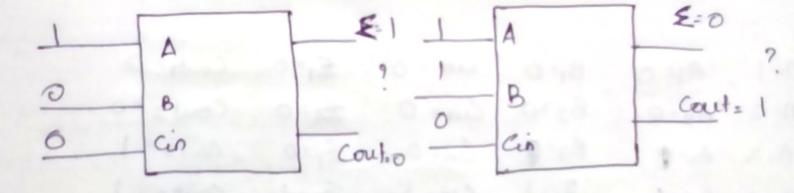

For the full adder shown, determine The outputs:

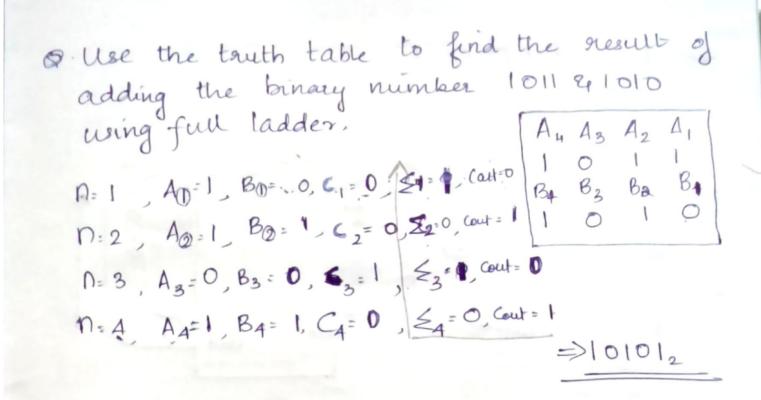

a. Use the 4 bit adder truth table to find the Sum and of carry for the addition of the following two flit nos y 4p carry is o. A4 A3 A2 A1 1 1 0 0 1=1 , A1=0 an = 0 1 = 0 Couty = 0 B1=0 )= 2 A2=0 £1:0 B2 =0 Cin = 0 Cout 2 = 0 B3= Cin= 0 \ \ = 0 Cout3 = 1 1=3 Az=1 Couta : 1 B4=1 Cin= 1 \{ |= 1 7=4 A4=1 = 110002  $A_1 = A_2 = A_3 = A_4 = A_4 = A_5 = A_5$

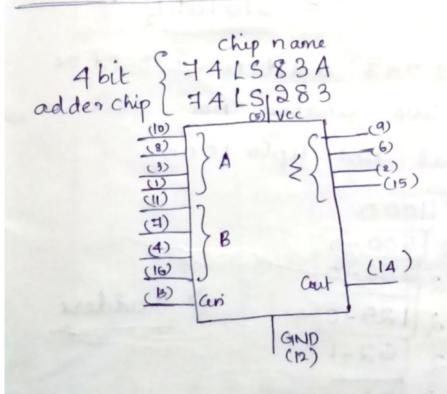

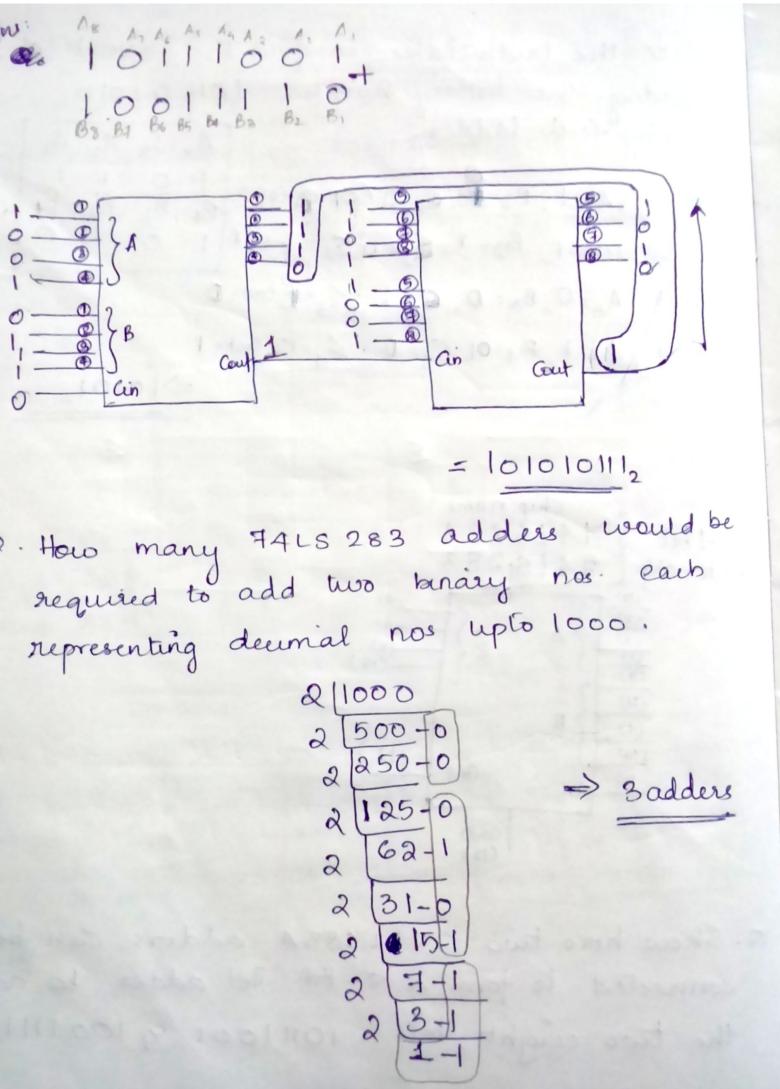

a. Show how two Q741583A adders can be connected to form a 8-bit Hel adder to add the two eight bits 10111001 410011110

| HALF | 30 | B | TRACT | OR |

|------|----|---|-------|----|

|      |    | - |       |    |

| A | B | D | Brut |

|---|---|---|------|

| 0 | 0 | 0 | 0    |

| 0 | 1 | 1 | 1    |

| 1 | 0 | 1 | 0    |

| 1 | 1 | 0 | 0    |

### FULL SUBTRACTOR

|   | A  | В    | Bin | Bout   | D   |

|---|----|------|-----|--------|-----|

|   | 0  | 0    | 0   | 0      | 0   |

|   | 0  | 0    | 1   | 1      | 1   |

| 1 | 0  | 1    | 0   | 1      |     |

| 1 | 0  | 1    | 1   | 1      | 0   |

|   | )  | 0    | 0   | 0      | 1   |

| 1 | 1  | 0    | 1   | 0      | 2   |

|   | 1  | 1000 | 0   | 0      | 0   |

|   | ما |      | 10  | salda, | 2 1 |

D=

$$\overline{A}$$

$\overline{B}$   $\overline{B}$

Bout: ABBin + ABBin + ABBin + ABBin = ABBin + ABBin = (AB+AB) Bin+ AB = (AOB) Bin + AB ADB - AB + AB.

Q. Explain ALU cising block diagram.

Q. Implement a fell subtractor vising a fell adder

Journal by Curricournion

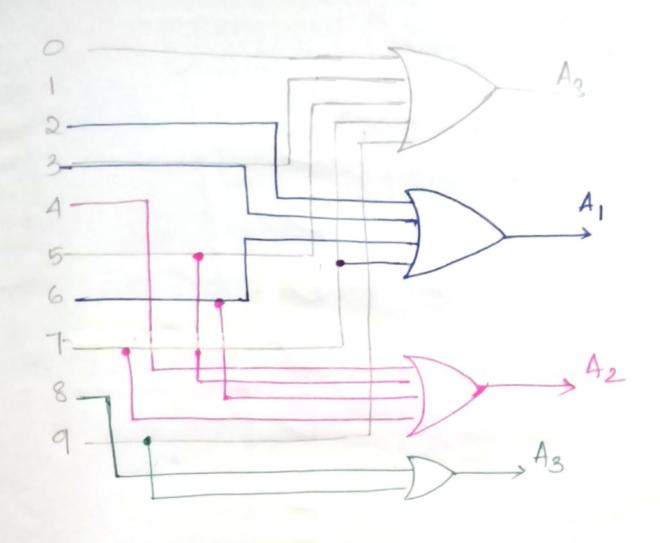

## ENCODER

converts decimal or octal to BCD or burary

| Pecimal | BCD        |

|---------|------------|

|         | A3 A2 A A0 |

| 0       | 0000       |

| 1       | 0001       |

| 2       | 0010       |

| 3       | 0011       |

| 4       | 0100       |

| 5       | 0101       |

| 6       | 0110       |

| J       | 0111       |

| 8       | 1000       |

| 9       | 1001       |

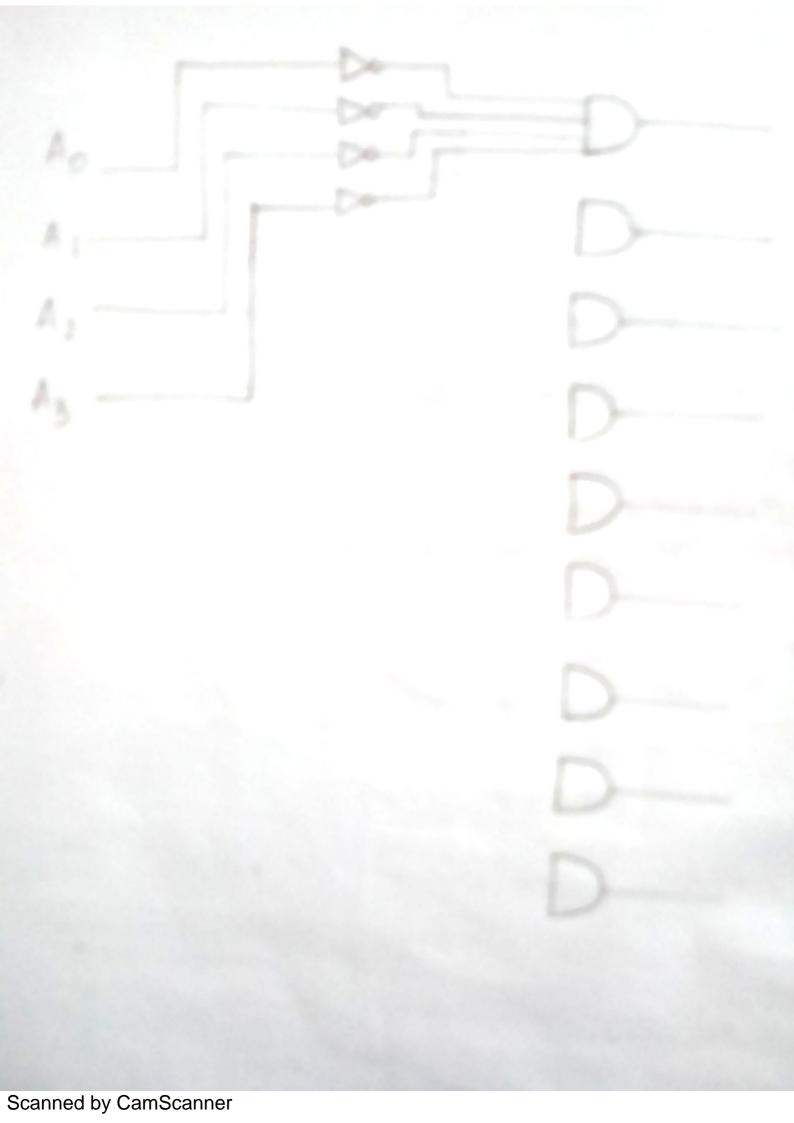

### DECORDER

converts BCD or binary to decimal or outal.

|    | BC             | D  |    | 0 | 1 | 2  | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|----|----------------|----|----|---|---|----|---|---|---|---|---|---|---|

| An | A <sub>2</sub> | A  | Ao |   |   |    |   |   |   |   |   |   |   |

|    |                |    |    | 1 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0  | 0              | 0  | 0  | - |   | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 9 |

| 0  | 0              | 0  | •  | 0 | 1 |    |   |   | 0 | 0 | 0 | 0 | 0 |

| 0  | 0              | 1  | 0  | 0 | 0 | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0  | 0              | 1  | 1  | 0 | 0 | 0  | , | 0 |   | 0 | 0 | 0 | 0 |

| 0  | 1              | 0  | 0  | 0 | 0 | 0  | 0 | 1 | 0 |   |   |   |   |

| 0  | 1              | 0  | 1  | 0 | 0 | 0  | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0  | 1              | 1  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

|    | Ι.             | L. |    |   |   |    | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0  | U              |    | 1  | 0 | 0 | 0  |   | 0 | 0 | 0 | 0 | 1 | 0 |

| 1  | 0              | 0  | 0  | 0 | 0 | 00 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

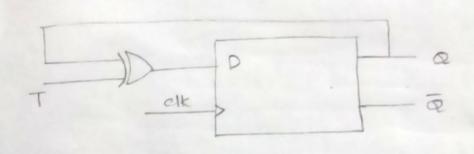

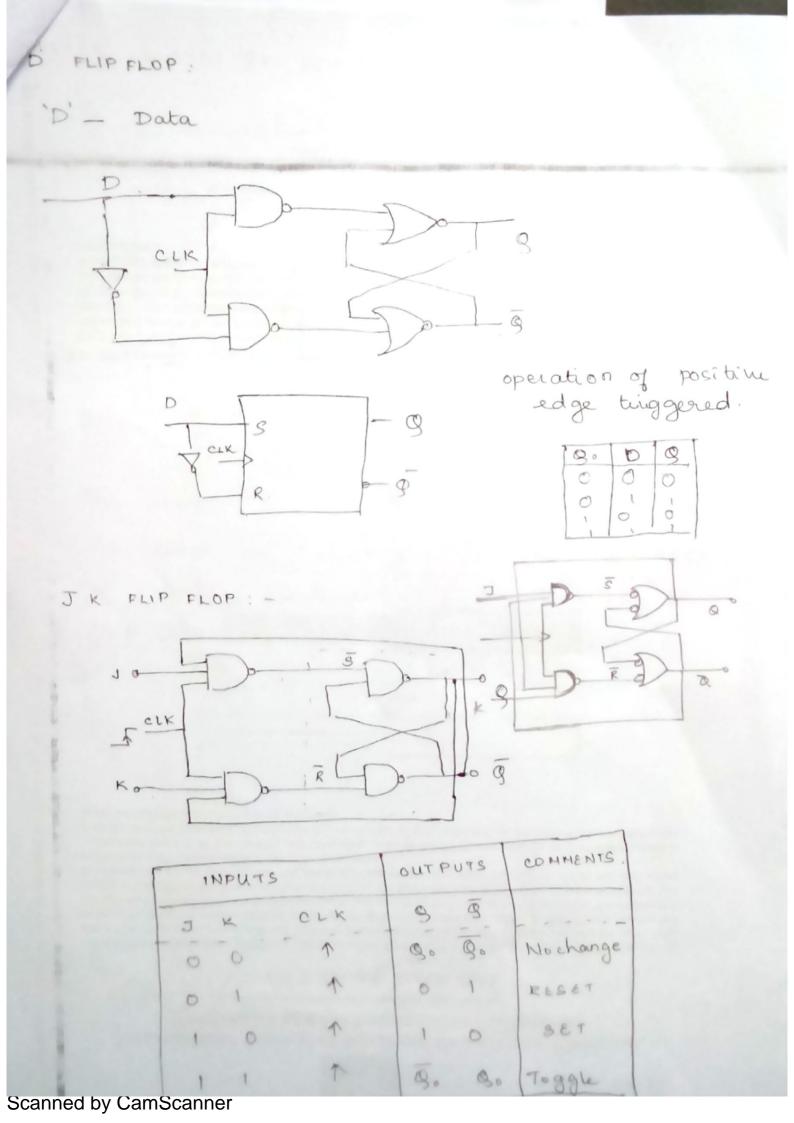

MODULE - 4 - combination al cercuits > Logic gates because it doesnot care about the previous 4p & it doesnot have a memory. Sequential circuit > It has an 4p & 0/p -> It has a memory sequence and is given as input through a feedback FLIP-FLOPS \* Printed notes. CONVERSION OF FLIP-FLOP Excitation table K J (prenous) Settle 0

# a Convert DFF to TFF

From the excitation table:

|   |   |   |   | 7 |

|---|---|---|---|---|

| 1 | T | Q | D |   |

| + | 0 | 0 | 0 |   |

| 1 |   | 0 | 1 | 1 |

| - |   | 1 | 0 | 1 |

|   | 0 | 1 | 1 |   |

| - |   |   | - | _ |

D: TQ + QT

### 9 . Convert SRFF to DFF

From the excitation lable

| A STATE OF THE STA |        |       |     |    |             |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-----|----|-------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S      | R     | D   | Q  |             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0      | ×     | 0 1 | 00 | 7 5         | 0 10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X      | 0     | 0   | 1  | 20 R=D      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |       |     |    | R.D'<br>S.D |      |

| ocanneu by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | / Camo | canne |     |    | 8 D         |      |

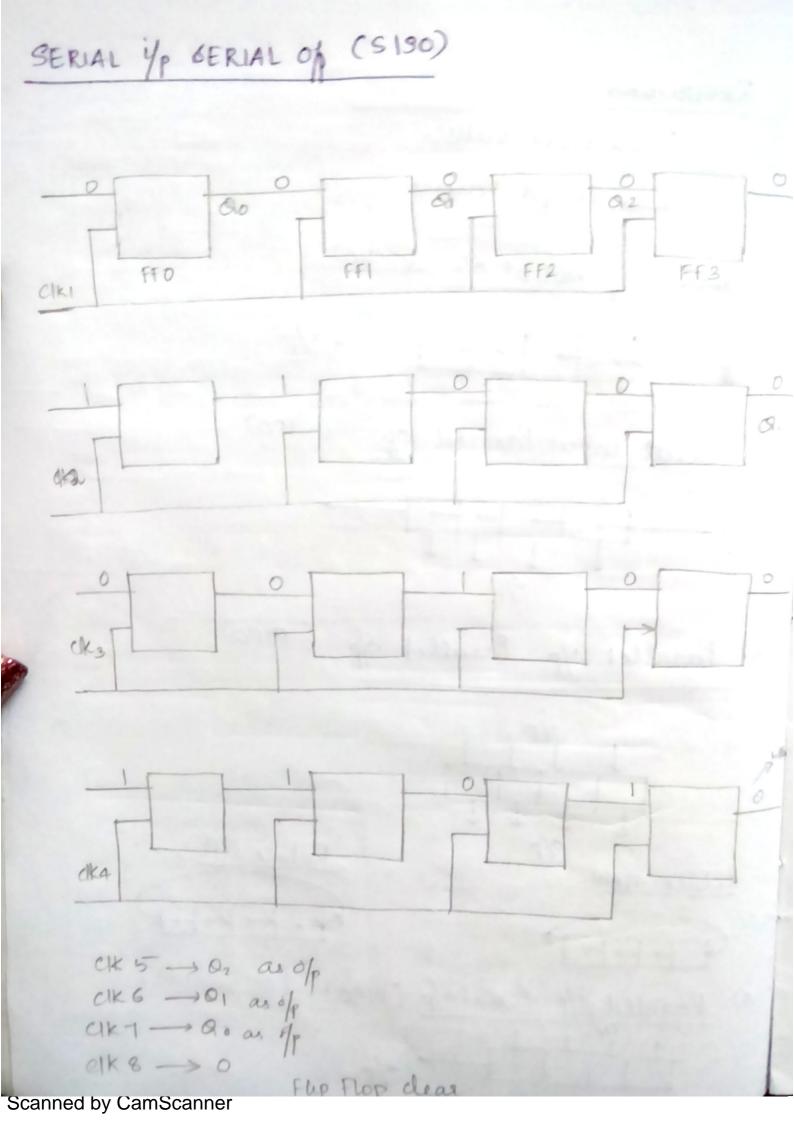

REGISTERS L-> store values - Shifts values 1) Berial if serial of (SISO) -> 9/P (SIPO) 2). Serial input Parallel op ip - F - F De Parallet 4p Parallet 8p (PIPO) J JP J J Rolate left: Rotate night 4नन्तर 4) Parallel 4p Serial of (PISO)

Mad-10 (0-9) To count 10 Nos (0-9) we need 4 flip-flops But 4 flip-flops will count upto 0-15 So use clear. Here, when the 10th clock comes a high (1) will come to 'clear' and sets all the Supslops to o. Thus containing only upto 1 HGH 13 JI MOD-12 (0-11) Preset HIGH \* with bubbles - Active Low

\* without bubbles - Active high.

Scanned by CamScanner

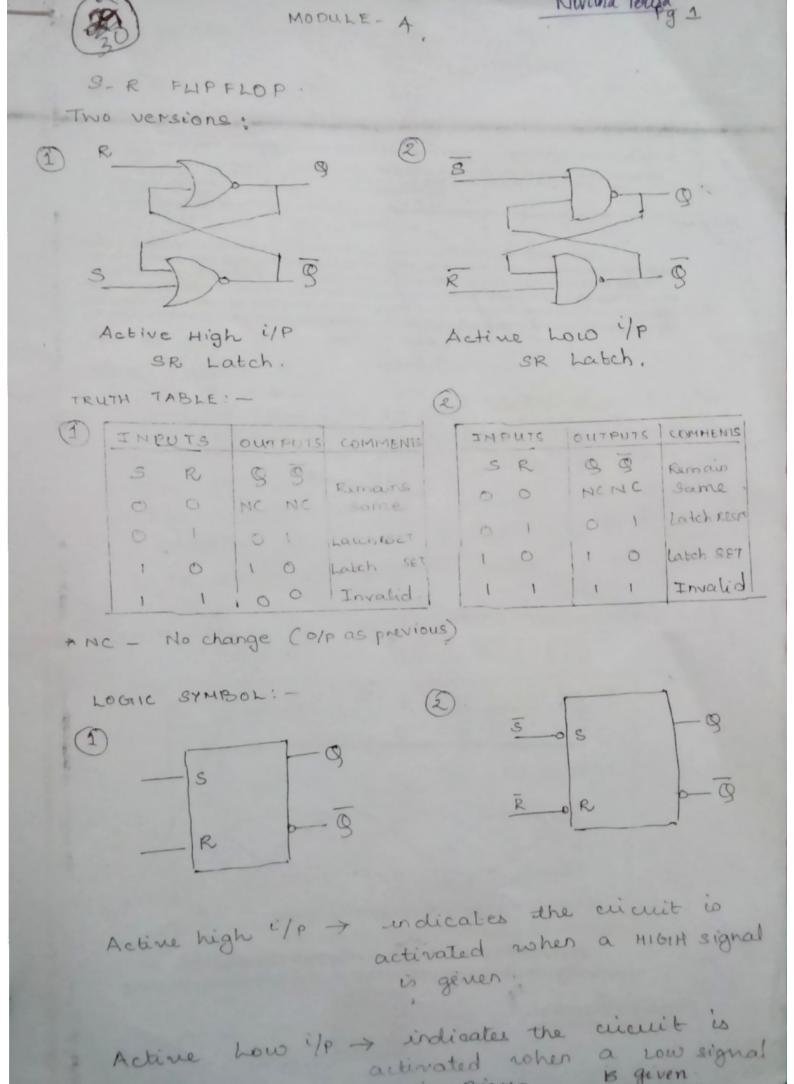

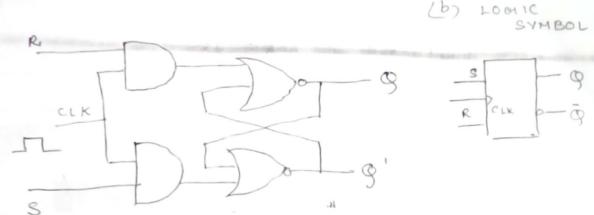

(a)

- clock pulse is 8.

- With both Sc1; Rz1 and clock pulse 1 the O/P goes to 0, both g & g'. Then when pulse goes to Low the O/P of AND gates becomes o, which causes it to choose a state g. O or g=1 and thus it is called in determinate.

TRUTH TABLE OF POSITIVE EDONE TRIGGERED 3-R FF :-

| COMMENTS  | OUTPUTS |     | INPUTS |   |   |

|-----------|---------|-----|--------|---|---|

|           | 18      | 9   | CLK    | R | 3 |

| No change | 90      | 9.  | ×      | 0 | 0 |

| RESET     | 1       | 0   | 1      | 1 | 0 |

| 3 E T     | 0       | 1   | ^      | 0 | 1 |

|           | alid.   | Inv | 1      | 1 | 1 |

\* 1 -> clock bransition Low to HIGH

x > innelevant ("don't care")

90 > previous state; prior to clock bransition.

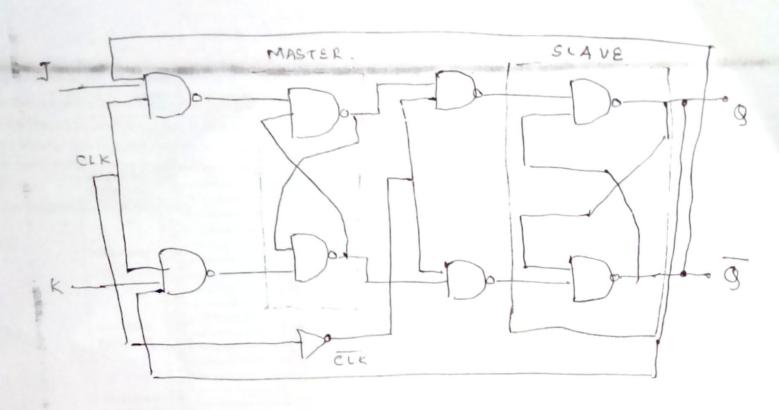

The sisput J K is connected to master SR.

As clock to 'slave' FF is complement

of master, clock input, the slave SR

flip flop does not toggle.

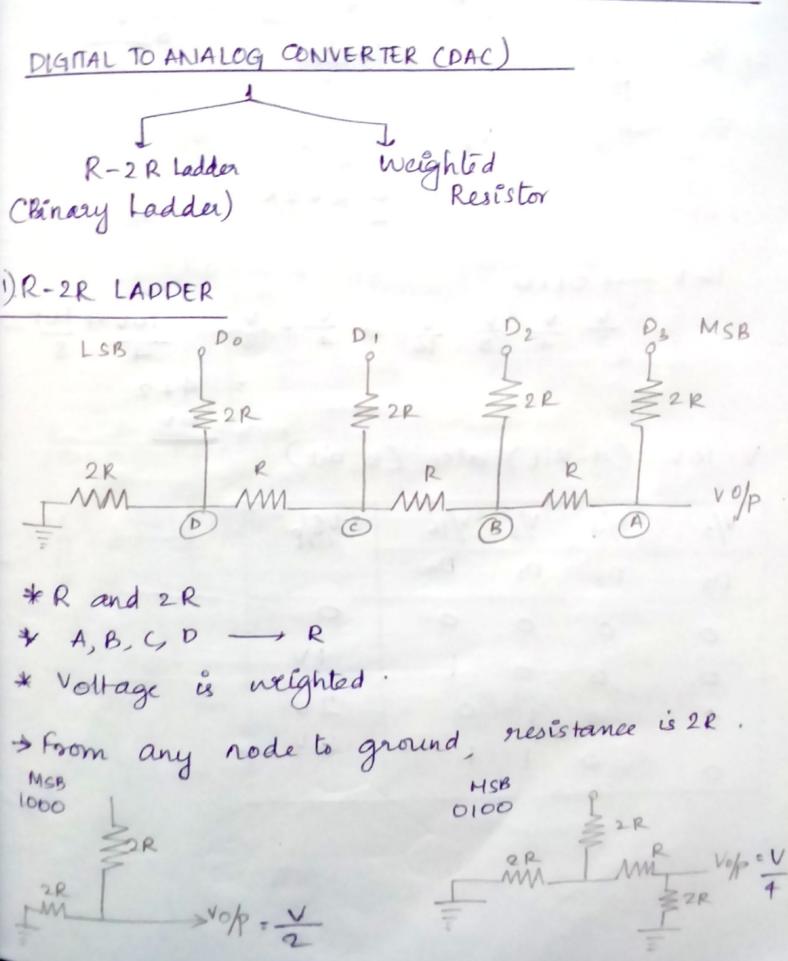

## MODULE-6 DIGITAL TO ANALOG CONVERTOR (DAC)

$$\frac{V_{B} = V\left(\frac{6}{5}\right)R}{16^{2}R} \Rightarrow \frac{3}{8}V$$

$$V_{R} = V \times 6 R$$

$$\frac{V}{2} \frac{V}{4} \frac{V}{8} \frac{V}{16} \Rightarrow \frac{V}{4} + \frac{V}{8} = \frac{16V + \frac{16V}{8}}{4}$$

$$= 4 + 2$$

| V/2 | V/4 | 1/8            | V/16 | Volp |

|-----|-----|----------------|------|------|

| 03  | D2  | D <sub>1</sub> | Do   |      |

| 0   | 0   | 0              | 0    | 0    |

| 0   | 0   | 0              | 1    | IV   |

| 0   | 0   | 1              | 0    | 2 V  |

| 0   | 0   | 1              | 1    | 3 V  |

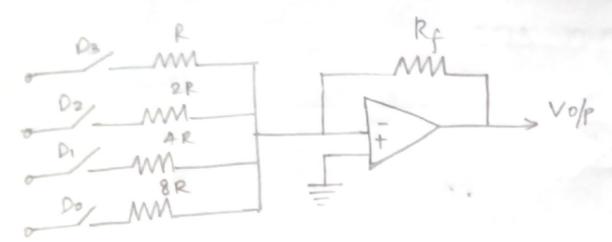

# 1.4-BIT WEIGHTED RESISTOR (Check &-bit weighted Ruiston)

$$VO[P = -Rf \left[ \frac{V}{R} + \frac{V}{2R} + \frac{V}{4R} + \frac{V}{8R} \right]$$

$$= -Rf \left[ \frac{D_3V}{R} + \frac{D_2V}{2R} + \frac{D_1V}{4R} + \frac{D_0V}{8R} \right]$$

$$V0|_{P^{2}} - 1* \left[ D_{3}V + \frac{D_{2}V}{2} + \frac{D_{1}V}{4} + \frac{D_{0}V}{8} \right]$$

Vin = 5 V

| Vin = | 10V |

|-------|-----|

|       |     |

| Vin                                     | Vnef              |      |

|-----------------------------------------|-------------------|------|

| 5 × 5 × 5 × 5 × 5 × 5 × 5 × 5 × 5 × 5 × | 8 V<br>4 V<br>6 V | 0000 |

| Vin               | Vref               |      |

|-------------------|--------------------|------|

| 10V<br>10V<br>10V | 0<br>8<br>12<br>10 | 1000 |

VHSIC Hardware Design Language Very high Scale Integrated aimit. KUHN Y-CHART GAJSKI Behaviour 3 gstero , sequential aranit -> Gate : Physical 1) Entity level - Name plate Jop 2). Architecture level 3). Configuration 1). Package declaration 5). Package body.

ARCHITECTURE LEVEL Behaviour 3 Large ckt

ARCHITECTURE LEVEL Data flow 3 Smaller

Structural 3 Size ckt

CONFIGURATION

Library ieee;

AND GIATE

A

B

D

Y

entity and 1 is

Port (A, B: in std-Logic);

Y: out std-Logic);

end and 1;

architecture behaviour 1 is

begin

Y

A and B

end behaviour 1;

OR GATE

entity or 1 is

Port (A, B: in Std - Logic;

y: out std - Logic;

end or 1;

agehitecture behaviour 1 is

begin

Y = A or B

End behaviour 1;

Port (A,B: in BIT;

SUM, CARRY: OUT BIT).

end hay-adder 1;

architecture structural - HA of hay adda 14

Port (A, B: in BIT:

architecture structural—HA of hayaddu is

Component and I is

port (A, B: in BIT;

Carry: trut BIT);

end component:

beguin

XI: XORI (A, B, Sum);

X2: ANDI (A, B, Garry);

end structural HA:

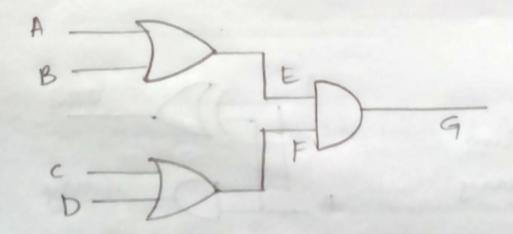

a - write the VHDL code for:

entity ext 1 is Port CA, B, C,D: In BIT: G: Out BIT); end ckt1; architecture structural 19 CK+1 is component or 1 is Port (x, y: In BIT; Z: Out BIT); end component; Component NADI Signal E, F: BIT; begin (Instances). XI: OR1 port map X2: OR1 port map X3: AND1 port map (A,B,E) (C,P,F) (E, F, G) end structural 1

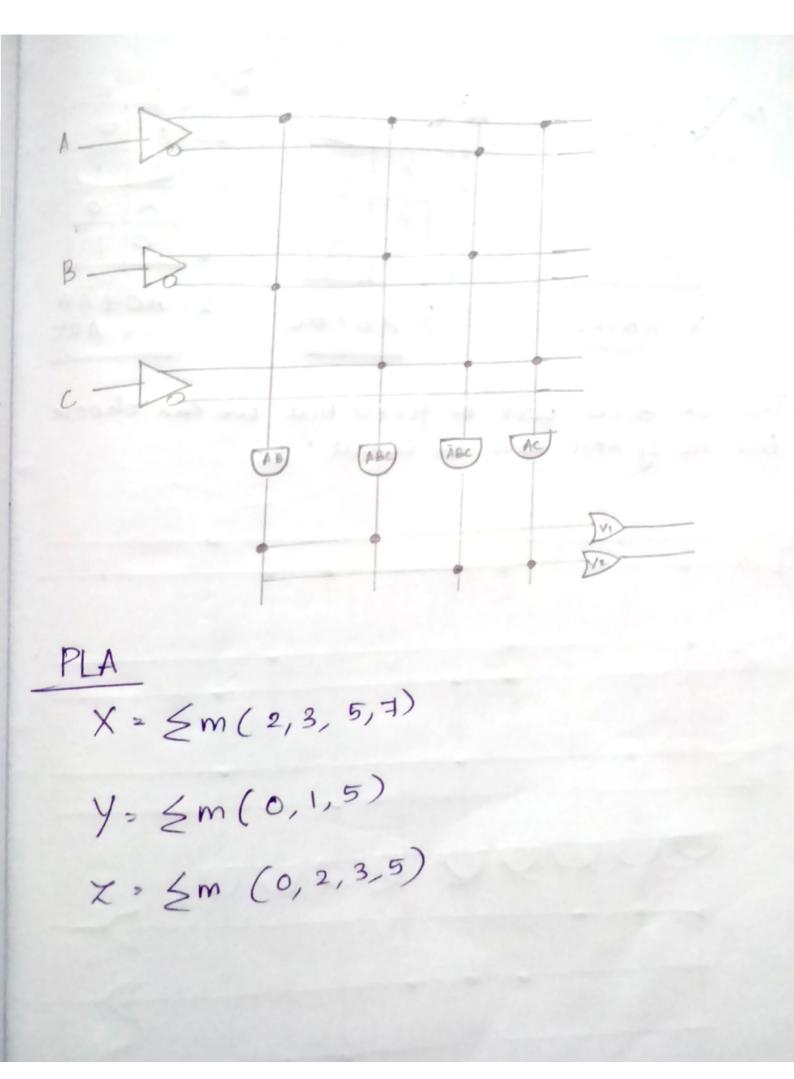

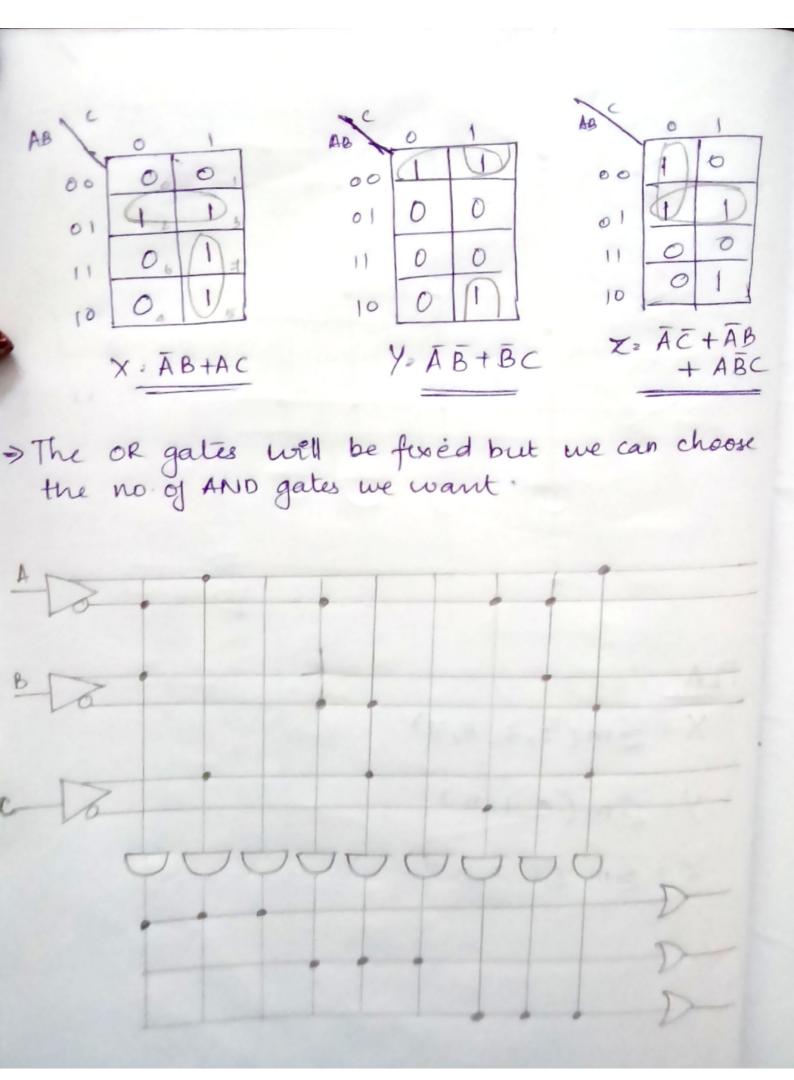

# PLD (PROGRAMMABLE LOGIC DEVICE) L> PAL (Programmable array Log(e) Program ANDgate program program of gal -> PLA (Programmable Legic Array) Fixed or got program AND gate PAL YI Y2 0 Y1: AB + ABC 0 Y2 > ABC +AC 0 0